By Thomas Tzscheetzsch, FAE Manager, Analog Devices

Question:

May I use the disable pin of an amplifier to save power without losing performance?

Answer:

Battery-operated applications are becoming popular in the IoT era. Luckily, there doesn’t have to be a trade-off between power saving and accuracy. Some operational amplifiers have disable pins and, when used correctly, they can yield up to 99% power savings without compromising accuracy.

The disable pin is primarily used in static operation (standby mode). In this mode, all ICs are switched to a state of low power consumption, without the device being used for signal processing, slashing the power consumption by several orders of magnitude.

If the operational amplifier is needed as a buffer amplifier for an ADC, as shown in Figure 1, it must be active to perform its function. However, the power consumption can still be kept low if the amplifier is switched to the power-down mode via the ‘disable’ pin. In general, the power-down mode is used whenever the ADC does not have to read any new values into its sample-and-holdfunction block.

Figure 1. Typical schematic of an ADC input stage with ADC driver and reference buffer

The easiest way to implement this is via the start command for conversion. In a standard ADC, the input (sample-and-hold) capacitor is first charged to the value to be measured, until the signal is sent to the ADC for conversion. The input capacitor is then isolated and connected to the inputs on the converter stage, which is when conversion begins. Then, it is completed, and a finishedsignal is set, which is dependent on the converter type.

Now comes the question: when does the operational amplifier have to be active?

It must be active long enough in advance of the conversion start-signal to ensure that the internal input capacitor has assumed the same value as the signal to be measured. The amount of time depends on such factors as input capacitor size, magnitude of voltage to be measured, and the rate at which the operational amplifier can drive a capacitive load.

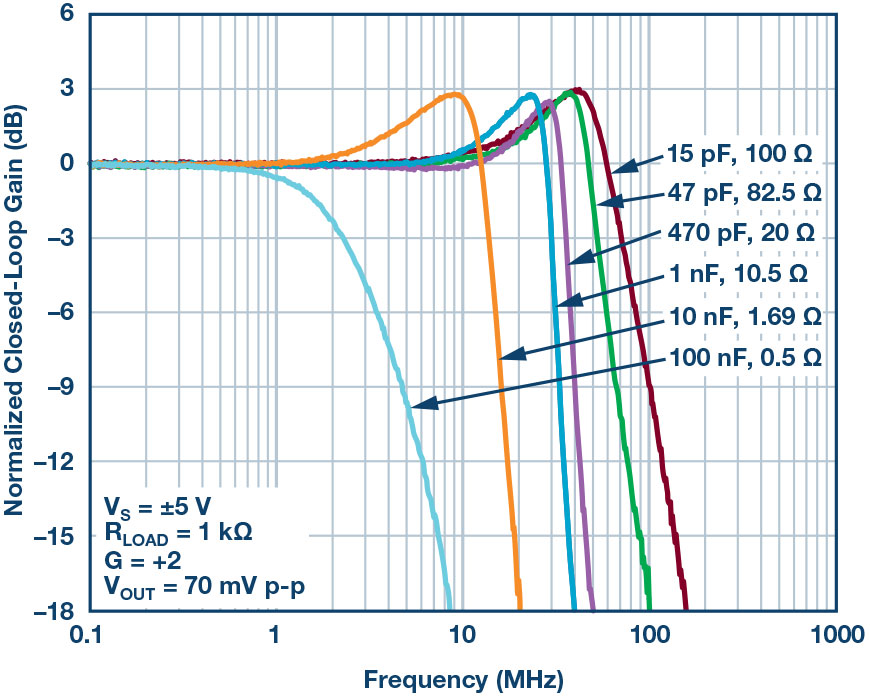

The data sheet for ADI’s ADC AD7980 gives a value of 30pF for the input capacitance in series with an impedance of 400Ω. However, with the operational amplifier, it isn’t that simple. A capacitive load of 15pF is stated in the parameter table, but more is possible, as can be seen in the corresponding diagram of Figure 2. The low-pass filter with 2.7nF and 20Ω also needs to be considered.

Figure 2. Frequency response of the ADA4807

The diagram shows that the module can drive sufficiently-high capacitive loads. After a disable, the amplifier needs about 500ns to settle to the full output level, which in our case is a maximum of 5V, or 4.096V.

To be on the safe side, we assume that the amplifier is switched on 750ns before the start of conversion. The extrapolated data for 1kSPS to 1MSPS is compared.

The savings potential ranges from 99.83% (0.02mW total consumption) at 1kSPS, to 92.41% (10.75mW total consumption) at 1MSPS. That’s only the savings from the ADC driver; the reference buffer also has savings potential.

Modern-Devices Example

This example is intended to show what modern devices are capable of. At the minimum sampling time of 500ns, the SINAD deviation was < 0.5dB. In the case of the driver, it is worthwhile to focus on faster derivatives and operate them dynamically. We have only considered the application as a buffer (gain = 1). For inverting or other amplifiers, the savings will be different depending on the conditions. Measurements should be carried out to check this.