# ELECTRONICS WORLD

THE ESSENTIAL ELECTRONICS ENGINEERING MAGAZINE

Volume 116 • Issue 1886

February 2010 • £4.60

[www.electronicsworld.co.uk](http://www.electronicsworld.co.uk)

## SOFTWARE REPORT:

- COMPLIANCE

- CLEANLINESS

- VIRTUALIZATION

- TOOLS

## RTOS:

- SCHEDULING AND TIMING ANALYSIS TECHNIQUES

## SIMPLE AND EFFICIENT DEBUG

4-CHANNEL 40MHZ-300MHZ OSCILLOSCOPES

TECHNOLOGY

POWER

EFFICIENCY

BREAKTHROUGH

FOR MMI

RF COLUMN

AN

ENGINEER'S

NEW YEAR

RESOLUTIONS

FOCUS

BATTERIES

REGULATIONS:

A ROUND-UP OF

RESPONSIBILITES

ALSO IN THIS ISSUE: TREND • DESIGN • LAST NOTE

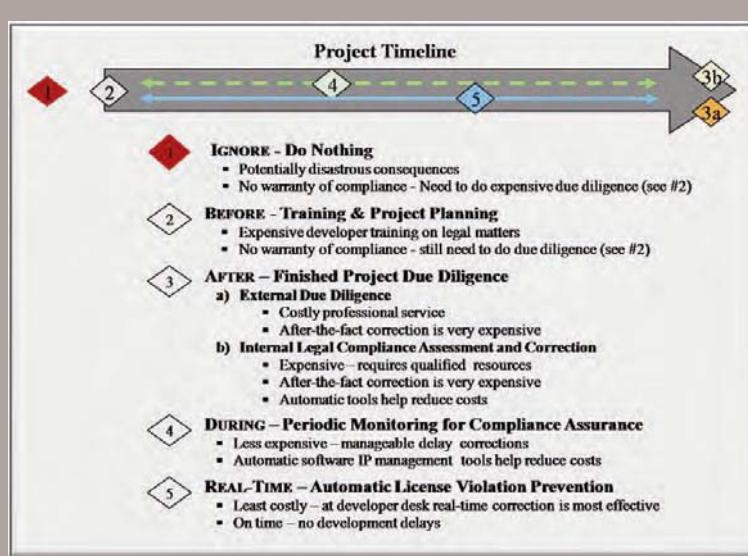

Find your distributor:

<http://www.mikroe.com/en/distributors/>

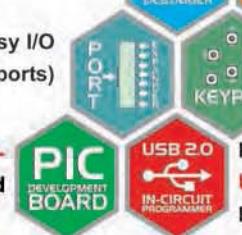

# DEVELOPMENT TOOL JUST THE WAY YOU LIKE IT

Everything you've always wanted from a development tool

Experience the ease of creating your own electronic devices!

## Complete PIC development solution

Speed up your prototype development with the EasyPIC6 Development System. The EasyPIC6 comes packed with examples that makes your PIC development fast and easy.

## Save time & money!

Get extra value for your money with this first-class tool for PIC development solutions. Get into the PIC world faster and easier than ever before with the EasyPIC6 Development System.

## Designed to suit your needs

Your development time can be considerably reduced, resulting in an early prototype design and fast time-to-market for your end product.

Thanks to many new features, you can start creating your own devices immediately. EasyPIC6 supports 8-, 14-, 18-, 20-, 28- and 40- pin PIC microcontrollers. The mikroICD (Hardware In-circuit Debugger) enables very efficient step by step debugging. Examples in C, BASIC and Pascal are provided with the board.

Hardware In-Circuit Debugger for step by step debugging at hardware level

On-Board 2x16 Serial LCD Display

Port Expander provides easy I/O expansion (2 additional ports) using serial interface

Keypad enables easy and fast data entry

Full-featured and user-friendly development board for PIC microcontrollers

High-Performance USB 2.0 On-Board Programmer

We deliver our products across the globe and our satisfied customers are the best proof of our first-rate service. The company is an official consultant on PIC microcontrollers and a Third Party Partner of Microchip Technology. We are also an official consultant and Third Party Partner of Cypress Semiconductors since 2002 and official consultants to Philips Electronics. All our products are RoHS compliant.

**mikroElektronika**

SOFTWARE AND HARDWARE SOLUTIONS FOR EMBEDDED WORLD

[www.mikroe.com](http://www.mikroe.com)

# REGULARS

## FEATURES

16

### 18 SCHEDULING AND TIMING ANALYSIS FOR SAFETY-CRITICAL REAL-TIME SYSTEMS

**Professor Alan Burns** and **Chris Dale** explore the scheduling and timing analysis techniques necessary for safety critical, real-time operating systems

### 22 REALISTIC IMPLEMENTATION OF SIGNAL INTEGRITY SCREENING – GUIDELINES FOR PCB DESIGNERS

**Griff Derryberry** looks at each of the roles of the engineer and PCB designer; considers the traditional design process; and makes suggestions on how the designer can contribute significantly to improving a design's overall signal integrity whilst saving time

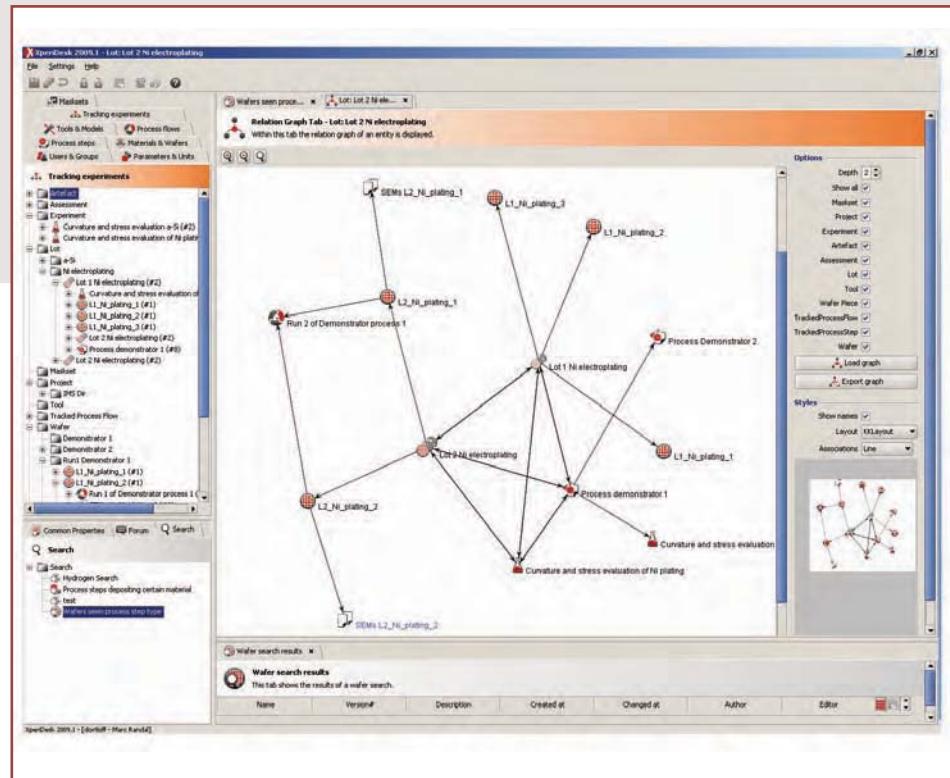

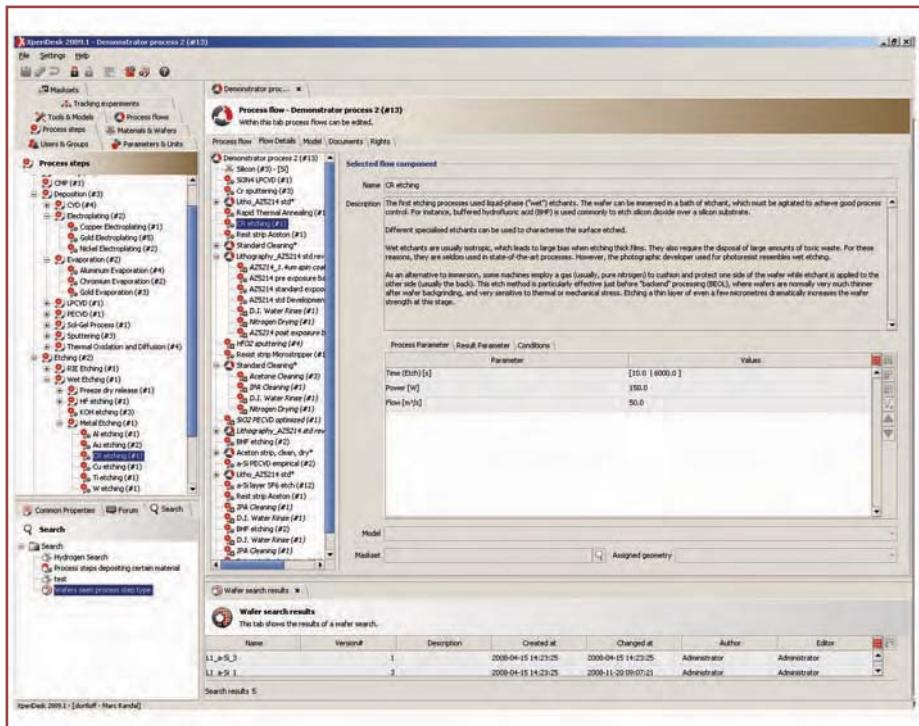

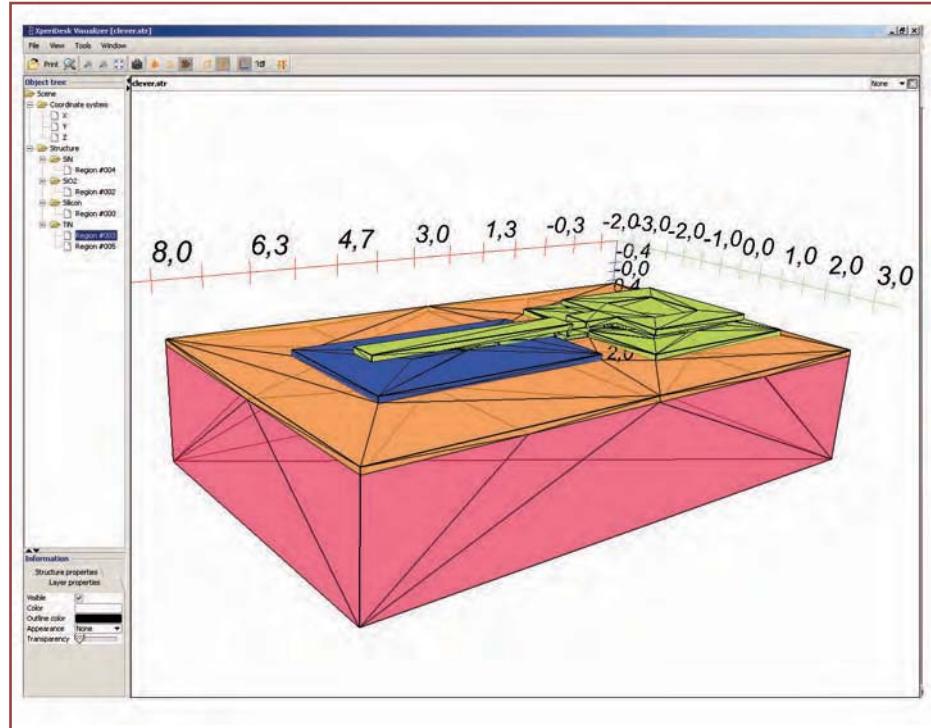

### 26 IMPROVING PROCESS DEVELOPMENT WITH BETTER DATA

**Dr Dirk Ortloff** discusses how better data management can benefit engineers in the high-tech process development field

### 30 LEGAL COMPLIANCE – FROM SOFTWARE DEVELOPMENT TO DELIVERY

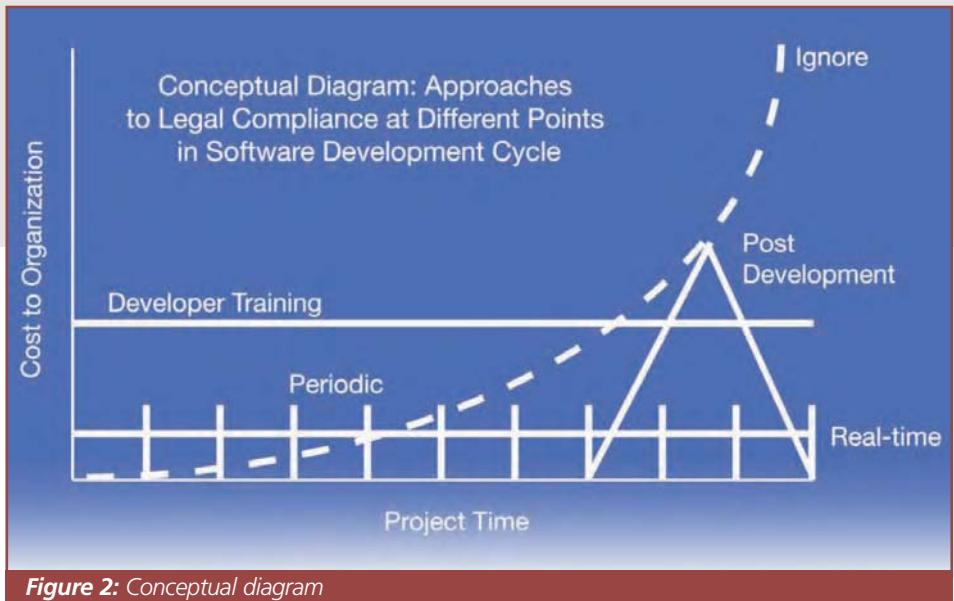

**Mahshad Koohgoli**, **Dr Sorin Cohn-Sfetcu** and **Kamal Hassin** discuss what's needed to keep the quality of software intact but also ascertain its legal compliance in today's ever more present open source and large scale outsourcing environments

### 34 VIRTUALIZING EMBEDDED LINUX

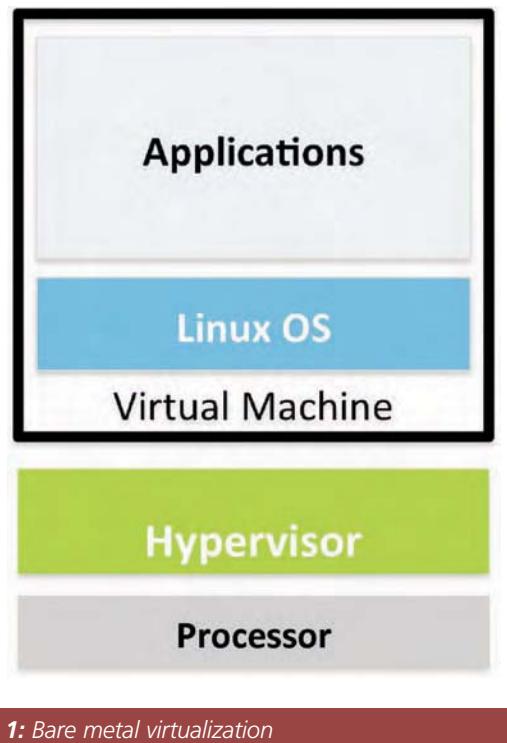

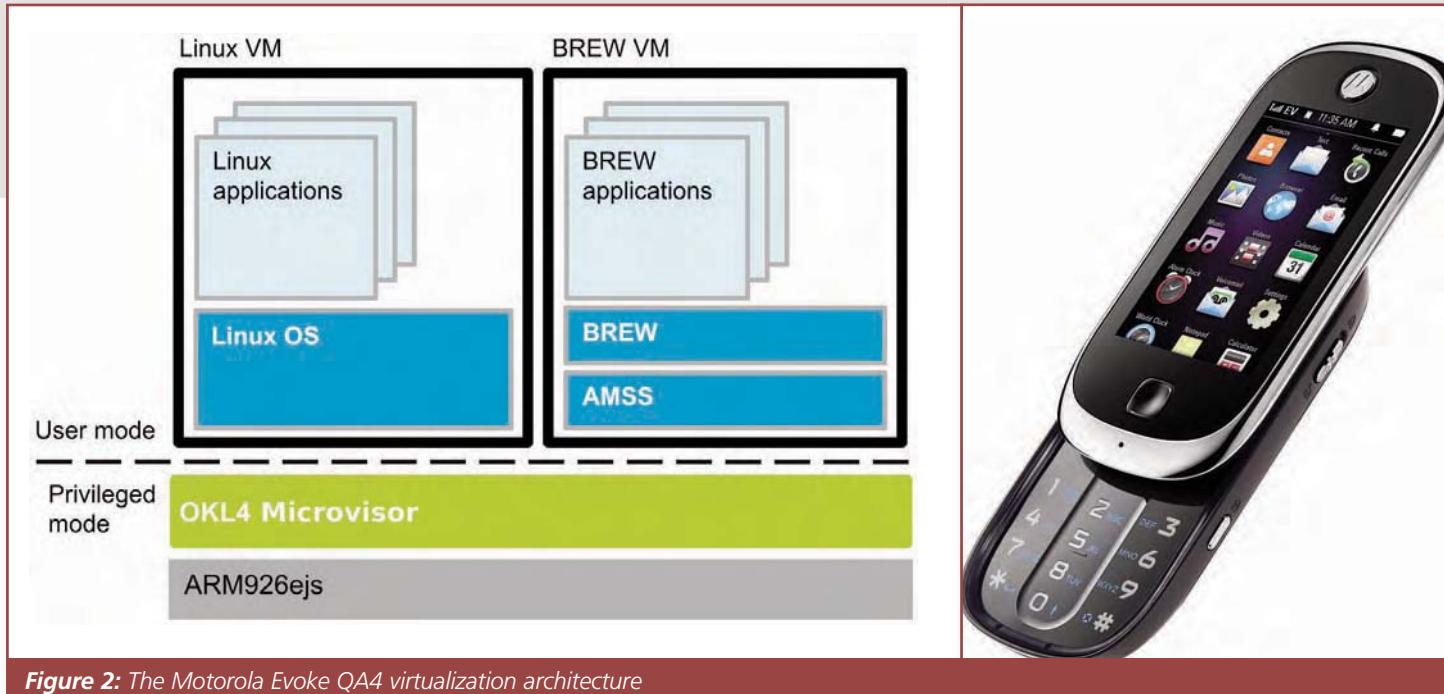

**Gernot Heiser** explains embedded and mobile virtualization technologies and explores how they can make Linux-based applications faster, more responsive, secure and IP-friendly

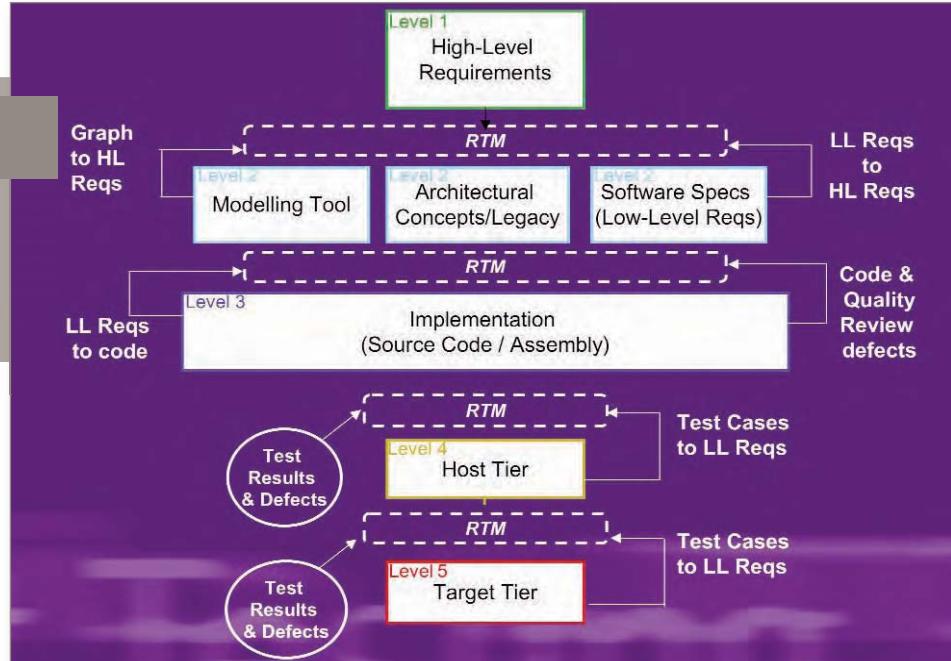

### 38 MIND THE GAP – MAKING THE LINK FROM REQUIREMENTS TO VERIFICATION

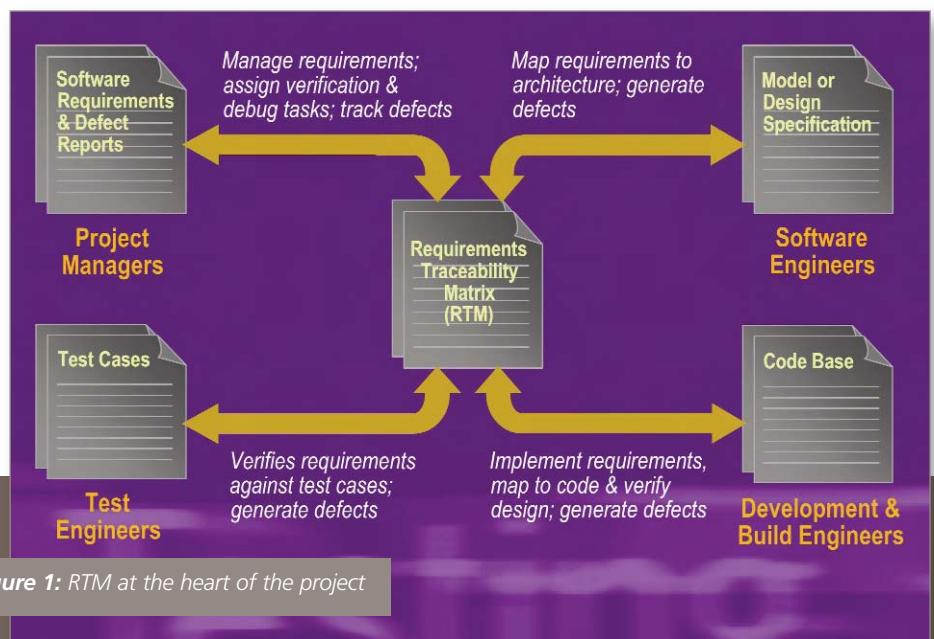

**Brian Hooper** and **Bill StClair** delve into an area that is regularly flagged up by gap analyses of software projects: the troubling field of requirements traceability, a key discipline for safety and security-critical projects

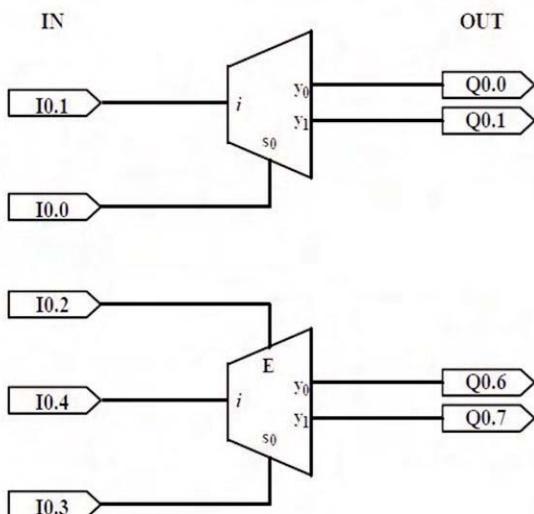

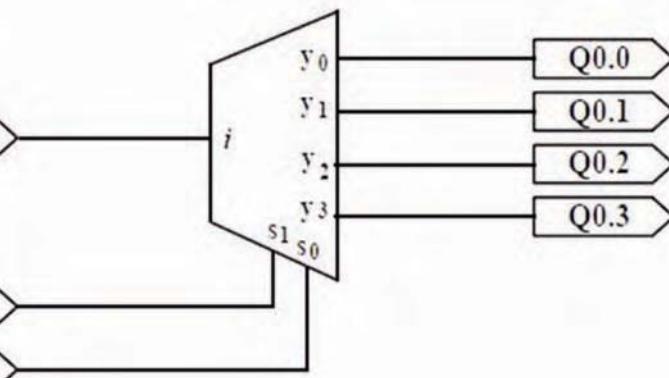

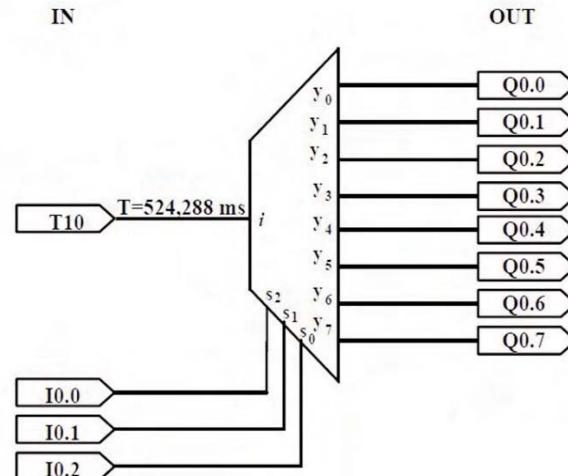

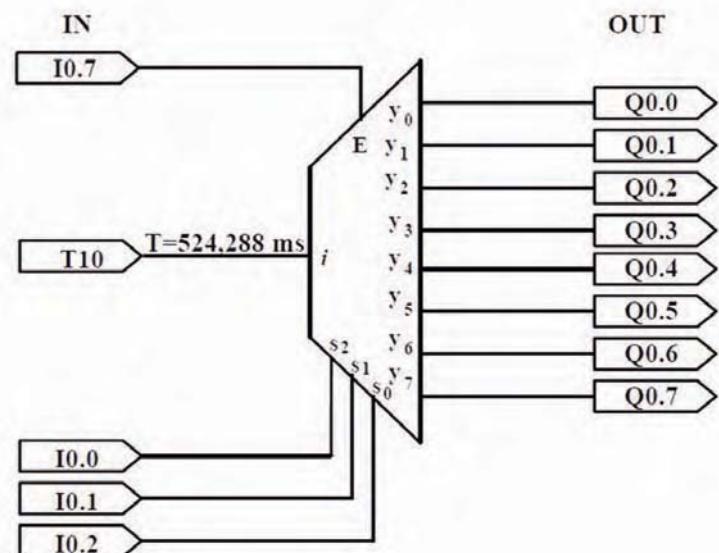

### 41 PLC WITH PIC16F648A MICROCONTROLLER – PART 16

**Prof Murat Uzam** presents the sixteen article in the series providing four examples to show the use of demultiplexer macros

### 05 TREND

OPTICAL COMMS: TOP FIVE TRENDS AND AREAS TO WATCH IN 2010

### 06 TECHNOLOGY

### 08 QUARTERLY ANALYST COLUMN

THE GREAT FAB-LITE DELUSION

by **Malcolm Penn**

### 10 INSIGHT

FASTER TIME TO MARKET THROUGH RAPID PROTOTYPING

by **Dave Robertson**

### 12 THE TROUBLE WITH RF...

A NEW YEAR

by **Myk Dormer**

### 16 FOCUS

BATTERIES REGULATIONS: A ROUND-UP OF RESPONSIBILITIES

An update on the Batteries Directive and how to stay within the law

by **Bob Mead**

### 45 DESIGN

### 47 PRODUCTS

### 50 LAST NOTE

Cover supplied by

**LeCroy**

more about

**WaveAce oscilloscopes**

on pages

14 & 15

*Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry – particularly as regards electric shock, fire hazards and explosions.*

Electronics World is published monthly by

**Saint John Patrick Publishers Ltd**,

6 Laurence Pountney Hill, London, EC4R 0BL

**QUASAR**

electronics

The Electronic Kit Specialists Since 1993

**Quasar Electronics Limited**

PO Box 6935, Bishops Stortford

CM23 4WP, United Kingdom

Tel: 01279 467799

Fax: 01279 267799

E-mail: sales@quasarelectronics.com

Web: www.quasarelectronics.com

**Postage & Packing Options** (Up to 0.5Kg gross weight): UK Standard 3-7 Day Delivery - £4.95; UK Mainland Next Day Delivery - £9.95; Europe (EU) - £8.95; Rest of World - £12.95 (up to 0.5Kg)

**Order online** for reduced price UK Postage!

We accept all major credit/debit cards. Make cheques/PO's payable to Quasar Electronics. Prices include 15.0% VAT.

Please visit our online shop now for details of over 500 kits, projects, modules and publications. Discounts for bulk quantities.

**01279**

Credit Card

Sales

**467799**

## Motor Drivers/Controllers

Here are just a few of our controller and driver modules for AC, DC, Unipolar/Bipolar stepper motors and servo motors. See website for full range and details.

### Computer Controlled / Standalone Unipolar Stepper Motor Driver

Drives any 5-35Vdc 5, 6 or 8-lead unipolar stepper motor rated up to 6 Amps. Provides speed and direction control. Operates in stand-alone or PC-controlled mode for CNC use. Connect up to six 3179 driver boards to a single parallel port. Board supply: 9Vdc. PCB: 80x50mm. Kit Order Code: 3179KT - £15.95 Assembled Order Code: AS3179 - £22.95

### Computer Controlled Bi-Polar Stepper Motor Driver

Drive any 5-50Vdc, 5 Amp bi-polar stepper motor using externally supplied 5V levels for STEP and DIRECTION control. Opto-isolated inputs make it ideal for CNC applications using a PC running suitable software. Board supply: 8-30Vdc. PCB: 75x85mm. Kit Order Code: 3158KT - £23.95 Assembled Order Code: AS3158 - £33.95

### Bi-Directional DC Motor Controller (v2)

Controls the speed of most common DC motors (rated up to 32Vdc, 10A) in both the forward and reverse direction. The range of control is from fully OFF to fully ON in both directions. The direction and speed are controlled using a single potentiometer. Screw terminal block for connections. Kit Order Code: 3166V2KT - £22.95 Assembled Order Code: AS3166V2 - £32.95

### DC Motor Speed Controller (100V/7.5A)

Control the speed of almost any common DC motor rated up to 100V/7.5A. Pulse width modulation output for maximum motor torque at all speeds. Supply: 5-15Vdc. Box supplied. Dimensions (mm): 60Wx100Lx60H. Kit Order Code: 3067KT - £17.95 Assembled Order Code: AS3067 - £24.95

Most items are available in kit form (KT suffix) or assembled and ready for use (AS prefix).

## Controllers & Loggers

Here are just a few of the controller and data acquisition and control units we have. See website for full details. Suitable PSU for all units: Order Code PSU445 £7.95

### 8-Ch Serial Isolated I/O Relay Module

Computer controlled 8-channel relay board. 5A mains rated relay outputs. 4 isolated digital inputs. Useful in a variety of control and sensing applications. Controlled via serial port for programming (using our new Windows interface, terminal emulator or batch files). Includes plastic case 130x100x30mm. Power Supply: 12Vdc/500mA. Kit Order Code: 3108KT - £64.95 Assembled Order Code: AS3108 - £79.95

### Computer Temperature Data Logger

4-channel temperature logger for serial port. °C or °F. Continuously logs up to 4 separate sensors located 200m+ from board. Wide range of free software applications for storing/using data. PCB just 45x45mm. Powered by PC. Includes one DS1820 sensor. Kit Order Code: 3145KT - £19.95 Assembled Order Code: AS3145 - £26.95 Additional DS1820 Sensors - £3.95 each

### Rolling Code 4-Channel UHF Remote

State-of-the-Art. High security. 4 channels. Momentary or latching relay output. Range up to 40m. Up to 15 Tx's can be learnt by one Rx (kit includes one Tx but more available separately). 4 indicator LED's. Rx: PCB 77x85mm, 12Vdc/6mA (standby). Two and Ten channel versions also available. Kit Order Code: 3180KT - £49.95 Assembled Order Code: AS3180 - £59.95

### DTMF Telephone Relay Switcher

Call your phone number using a DTMF phone from anywhere in the world and remotely turn on/off any of the 4 relays as desired. User settable Security Password, Anti-Tamper, Rings to Answer, Auto Hang-up and Lockout. Includes plastic case. Not BT approved. 130x110x30mm. Power: 12Vdc. Kit Order Code: 3140KT - £74.95 Assembled Order Code: AS3140 - £89.95

### Infrared RC Relay Board

Individually control 12 on-board relays with included infrared remote control unit. Toggle or momentary. 15m+ range. 112x122mm. Supply: 12Vdc/0.5A. Kit Order Code: 3142KT - £59.95 Assembled Order Code: AS3142 - £69.95

### New! 4-Channel Serial Port Temperature Monitor & Controller Relay Board

4 channel computer serial port temperature monitor and relay controller with four inputs for Dallas DS18S20 or DS18B20 digital thermometer sensors (£3.95 each). Four 5A rated relay channels provide output control. Relays are independent of sensor channels, allowing flexibility to setup the linkage in any way you choose. Commands for reading temperature and relay control sent via the RS232 interface using simple text strings. Control using a simple terminal / comms program (Windows HyperTerminal) or our free Windows application software. Kit Order Code: 3190KT - £69.95

## PIC & ATMEL Programmers

We have a wide range of low cost PIC and ATMEL Programmers. Complete range and documentation available from our web site.

### Programmer Accessories:

40-pin Wide ZIF socket (ZIF40W) £14.95

18Vdc Power supply (PSU120) £19.95

Leads: Serial (LDC441) £3.95 / USB (LDC644) £2.95

### USB & Serial Port PIC Programmer

USB/Serial connection. Header cable for ICSP. Free Windows XP software. Wide range of supported PICs - see website for complete listing. ZIF Socket/USB lead not included. Supply: 16-18Vdc. Kit Order Code: 3149EKT - £49.95 Assembled Order Code: AS3149E - £59.95

### USB 'All-Flash' PIC Programmer

USB PIC programmer for all 'Flash' devices. No external power supply making it truly portable. Supplied with box and Windows Software. ZIF Socket and USB lead not included. Assembled Order Code: AS3128 - £49.95

See website for full range of PIC & ATMEL Programmers and development tools.

[www.quasarelectronics.com](http://www.quasarelectronics.com)

Secure Online Ordering Facilities • Full Product Listing, Descriptions & Photos • Kit Documentation & Software Downloads

**No.1**

KITS

# OPTICAL COMMS: TOP FIVE TRENDS AND AREAS TO WATCH IN 2010

What this piece states is that there are several issues to watch out for in optical communications in 2010

## 1. Continued Consolidation and Economic Recovery

BY SINCLAIR VASS

In 2010, it will be widely accepted that economic recovery is well underway across the world. And while there is significantly more life in the optical communications marketplace, the intense cost-reduction focus that occurred during the recession has resulted in even lower inventory levels and shorter lead-times requirements, making it even more challenging for NEMs and component suppliers to meet the volatile end carrier demand.

Optical vendors will, therefore, continue to optimise lean manufacturing practices and operations to support unpredictable fluctuations in market requirements. There will be industry consolidation as the large number of smaller players look to partner in their core segments, acquire or divest.

### 2. The Asia Effect

As large Asian NEMs rapidly gain traction in the worldwide market with low-cost system offerings, European and American NEMs will continue to feel the pressure. Some Asian NEMs have a business model that focuses on buying components at lower levels of integration and building systems in-house with cheap labour; often with support of local government subsidy. For other NEMs the opposite approach may work best, outsourcing the integration of optical hardware solutions at the circuit pack level, whilst focusing internally on core strengths. It is hard to predict whether both models can co-exist, but the winners will obviously be the companies with the best product portfolio and cost structure.

### 3. Evolution in the Supply Chain

In the wireless industry, there have been significant changes to the operating model, with service providers outsourcing network management to the NEMs. This trend may also reach the wireline business over the next five years. In this scenario, service providers would focus on creating new applications that drive more revenue over their networks. NEMs would become less component-focused and take on the responsibility of managing and optimising the network. This in turn would allow optical vendors to focus on building and testing critical solutions. Many players believe that the converged network will be a future reality and the boundaries between wireless and wireline networks will disappear.

### 4. 40G – 100G

The industry continues to deal with fragmentation in the 40G space and cost challenges for the development of both 40G and 100G products. Both markets will likely ramp over the next 2-4 years, but these current challenges need to be addressed in order to move forward. Standards bodies need to quicken the pace on ratifying new standards to curb the implementation of multiple proprietary products that support several different modulation schemes. 40G will in the future likely be supported by three dominant modulation formats superseding the current ODB scheme. These new modulation schemes will co-exist in the network but over time the most powerful coherent receiver intradyne solution will dominate.

During 2010, the advanced development functions within the larger NEMs will turn their focus towards even faster transmission rates to 400Gb/s and beyond.

### 5. Increased Use of WSS Solutions and Tunable Transceivers

WSS modules will see significant uptake over the next five years. Solutions will include growth in a broad range of WSS products.

Particularly over the next two years, solutions for directionless and colourless, meshed network designs will be vital. This will drive a range of new reconfigurable, colourless and non-blocking modules that will provide the necessary functionality to support this architecture. Particularly new WSS switching modules, flexible amplifiers and integrated tunable XFP transceivers solutions will emerge.

**Sinclair Vass is Senior Director of Communication Sales for EMEA at JDSU**

/// **MANY PLAYERS BELIEVE THAT THE CONVERGED NETWORK WILL BE A FUTURE REALITY AND THE BOUNDARIES BETWEEN WIRELESS AND WIRELINE NETWORKS WILL DISAPPEAR** //

**EDITOR:** Svetlana Josifovska

Email: svetlanaj@stjohnpatrick.com

**PRODUCTION MANAGER:** Tania King

Email: taniak@stjohnpatrick.com

**DISPLAY SALES:** Neil Coshan

Tel: +44 (0) 20 7933 8977

Email: neilc@stjohnpatrick.com

**PUBLISHING DIRECTOR:** Chris Cooke

**PUBLISHER:** John Owen

**SUBSCRIPTIONS:**

Saint John Patrick Publishers

PO Box 6009, Thatcham,

Berkshire, RG19 4QB

Tel: 01635 879361

Fax: 01635 868594

Email: electronicsworld@circdata.com

**SUBSCRIPTION RATES:**

1 year: £46 (UK); £67.50 (worldwide)

**MISSING ISSUES:**

Email: electronicsworld@circdata.com

**NEWSTRADE:**

Distributed by Seymour Distribution Ltd,

2 East Poultry Avenue, London, EC1A 9PT

Tel: +44 (0) 20 7429 4000

**PRINTER:** William Gibbons Ltd

**ISSN:** 1365-4675

John Patrick Publishers

# Power Efficiency Breakthrough for Mobile Memory Solutions

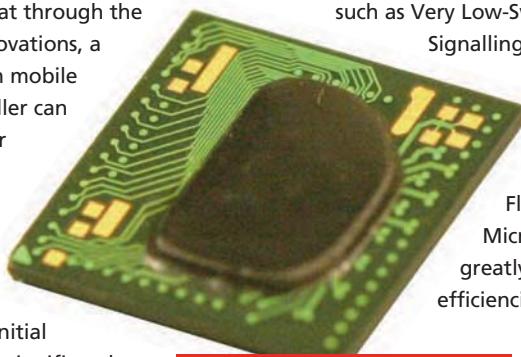

Memory architectures licensing company Rambus announced it has achieved a new breakthrough level of power efficiency with its latest silicon test vehicle developed through its Mobile Memory Initiative (MMI).

The silicon-validated results demonstrate that through the use of MMI innovations, a high-bandwidth mobile memory controller can achieve a power efficiency of 2.2mW/Gbps. This is nearly a one third improvement over the initial MMI silicon and significantly better than the estimated 10mW/Gbps of an LPDDR2 400 memory controller.

"The performance demands of next-generation mobile devices are vastly outstripping the pace of battery technology improvements," said Martin Scott, senior vice president of Research and Technology Development at Rambus. "With the innovations developed through our Mobile

Memory Initiative we can deliver advanced applications and maintain long battery life through our breakthroughs in both, bandwidth performance and power efficiency."

Rambus's MMI encompasses innovations such as Very Low-Swing Differential Signalling, FlexClocking Architecture and Advanced Power State Management. In addition, Rambus's FlexPhase and Microthreading technologies greatly improve the power efficiencies of mobile platforms.

The MMI was launched in February last year, with focus on achieving high bandwidth at extremely low power to enable advanced applications in next-generation smartphones, netbooks, portable gaming and portable media products. Operating at 4.3Gbps, a memory system using MMI innovations can deliver over 17GB/s of memory bandwidth from a single mobile DRAM device.

Rambus's MMI test silicon chip

## New Alchimer Seedless Wet Deposition Technology Eliminates Entire Step From TSV Film Stack Process

Massy, France, based Alchimer, a provider of technology for the deposition of nanometric films used in semiconductor interconnects and 3D through-silicon vias (TSV), announced a groundbreaking advance in TSV formation that eliminates one of the traditional metallization steps.

AquiVia XS is now available for demonstration

Alchimer already offers AquiVia wet deposition processes for isolation, barrier and seed layers in TSV metallization that uses electrografting, a nanotechnology solution based on surface chemistry formulations and processes to grow highly conformal and uniform layers in TSVs with aspect ratios up to and beyond 20:1.

But in its newest solution, AquiVia XS, by eliminating the seed-layer step from the standard isolation-barrier-seed process flow, Alchimer allows bulk fill to take place directly after application of the barrier layer. This is also the first deposition solution to support both nickel and copper metallization.

"The AquiVia XS approach provides a previously impossible combination of film quality, broad applicability and cost benefits," said Alchimer's CEO Steve Lerner.

Companies are slow to take up the innovation challenge that plastic electronics presents, says research from the Advanced Institute of Management Research (AIM Research).

The Plastic Electronics industry is predicted to be worth \$335bn within 20 years, and although plastic electronics products are already being manufactured on a commercial scale, what is lacking, says the research, is involvement by product designers and market-led end users. In addition, companies in the retail, healthcare, transport, electronics and packaging industries have yet to understand the revolution that is taking place.

With Plastic Electronics electronic materials can be formed into circuits using cheap core materials. Products can be printed onto flexible surfaces like paper, film or fabric allowing the manufacture of thin, lightweight devices. The costs are low enough that wallpaper, for example, can be designed with integral lighting, and clothing can be printed with wearable electronics and solar cells.

Cranfield University has developed a new technology that promises to significantly reduce the manufacturing cost of complex micro-mechanical and micro-optical devices.

"Standard micro-fabrication techniques are often incompatible with high quality transducer materials such as shape memory alloys and functional ceramics," said Stephen Wilson, Senior Research Fellow at Cranfield University. "This is one of the major bottlenecks for the development of novel micro-scale systems. The new technology enables multi-material devices to be made that do not conform to the usual silicon MEMS stereotype." The new methods can be used in the manufacture of many components and systems ranging in size from a few millimetres to a few 100s of nanometres. Applications include biomedical devices that can diagnose disease and electronically administer drugs, electronic noses to sniff out explosives or dangerous chemicals and environmental control systems for personal healthcare.

The project is part of a €3.2m research consortium entitled Q2M (Quality to Micro).

Like AquiVia, AquiVia XS enables the use of existing plating equipment for layer deposition and completely eliminates all dry processing techniques from TSV metallization. As a result, cost of ownership of the via stack metallization process is reduced by up to 80%. Both products also result in highly conformal and uniform layers for TSVs with aspect ratios of 20:1 and beyond, even on the highly scalloped etch profiles produced by the DRIE/Bosch process.

AquiVia XS is now available for immediate demonstration and licensing.

# TSMC ANNOUNCES PROCESS TECHNOLOGIES FOR INTEGRATED LED DRIVERS

Taiwan Semiconductor Manufacturing Company unveiled modular BCD (Bipolar, CMOS DMOS) process technologies targeting high voltage integrated LED driver devices.

The new BCD technologies feature a voltage spectrum running from 12 to 60V to support multiple LED applications, including LCD flat panel display backlighting, LED displays, general lighting and automotive lighting. It covers process nodes from 0.6-micron to 0.18-micron with a number of digital core modular options for varying digital control circuit gate densities. The CyberShuttle prototyping service supports the 0.25-micron and 0.18-micron processes for preliminary function verification.

12-inch wafer fab

"The new BCD technologies for LED drivers are very leading edge in driving device integration. The associated PDKs feature highly accurate SPICE models that really enhance the potential for easy single chip design," said George Liu, Director,

Industrial Business Development. "In addition, mismatching models help optimise current mismatching performance in multi-channel LED driver designs."

The DMOS process supports 72mohm per mm<sup>2</sup> at BV > 80V for a specific 60V NLDMOS Rds(on) performance and its high current driving capability optimises device sizes that enhance power efficiency.

A robust safe operating area (SOA) makes it ideal for both power switch and driver design. Fine detailed characterisation also provides a useful reference to optimise the design budget for optimum chip size.

On the CMOS side, a 5V capability supports analogue Pulse Width Modulation (PWM) controller design elements, and the 2.5V and 1.8V logic cores are optional modules for higher-level digital integration. In addition, logic compatible one-time programmable (OTP) and multi-time programmable (MTP) memory options are available for enhanced digital programming design.

The integrated component options include high voltage bipolar transistors, high voltage, high precision capacitors, high resistance poly and Zener diodes to reduce external passive component count and circuit board area.

## ARE YOU LOOKING FOR BACK ARTICLES?

Now you can buy back copies of **Electronics World** from the years 2006, 2007, 2008 & 2009.

Digital editions £4.20 per copy

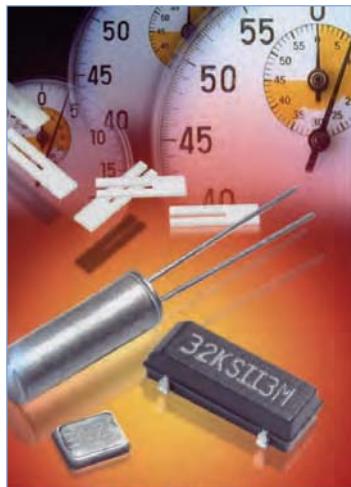

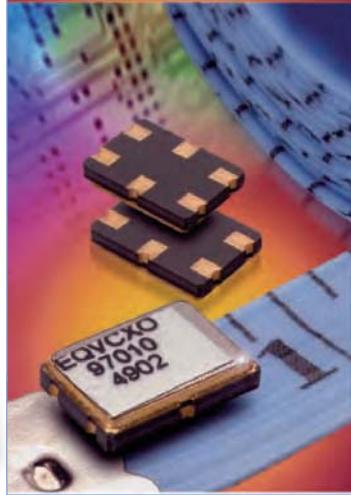

### EXTENSIVE FREQUENCY CONTROL RANGE

Euroquartz high quality frequency control products for aerospace, medical, wireless, communications and telecom applications.

- Quartz crystals

- Oscillators

- VCXOs, TCXOs & OCXOs

- Crystal, SAW & custom filters

- Resonators

On-site production, quick turnaround, custom design, prototypes, up-to-date production and test methods, engineering design and support, 100% product validation. ISO 9001:2000 certified.

### EUROQUARTZ

Euroquartz, Blacknell Lane Industrial Estate, Crewkerne, Somerset, TA18 7HE.

Tel: +44 (0) 1460 230000, Fax: +44 (0) 1460 230001, email: sales@euroquartz.co.uk

Website: [www.euroquartz.co.uk](http://www.euroquartz.co.uk)

# THE GREAT FAB-LITE DELUSION

**Malcolm Penn** is CEO and chairman of market analyst firm Future Horizons, based in the UK

**OVER THE PAST** few years, squeezed by declining ASPs (average selling prices) and a zero-growth market (in value terms), the so-called fab-lite business model was born and unashamedly embraced. Encouraged by the financial community, seized upon by struggling IDMs, driven by the fabless firms' success, edged on by OEM disinterest, firm after firm has signed up to the concept, lauding the benefits and turning a blind eye to the flawed logic reality... if something is seemingly too good to be true, it usually is.

Not so, goes the argument. Wafer fabrication is a service operation, a simple make-buy decision best left to outsourcing. Foundries are fundamentally more efficient than IDMs, meaning they can make wafers much cheaper than in-house production. In any event, the chip industry has been outsourcing back-end manufacturing for decades without any problem and fabless companies have constantly out-performed IDMs' growth with no competitive disadvantage to not having a fab. Contrast that with the IDM corporate liability of owning and operating a fab, tying up cash and management resources; fab-lite elegantly solves these inherent problems, levelling the playing field with the fabless competition.

If only it were that simple. Not only is the justification logic muddled, superficial, flawed and confused, there is no industry consensus on what exactly fab-lite means; witness the fact the term is littered with a variety of alternative colourful euphemisms, such as asset-lite and asset-smart, implying these are something similar to fab-lite but subtly different and implicitly better.

The fact is, unlike fabless or IDM, fab-lite is a chameleon meaning different things to different people, but said with such brash and reassuring gusto that no one questions the strategic reality that fab-lite is nothing more than an illusion ... Emperor's new clothes.

Euphemisms aside, there are two fundamental fab-lite varieties. Option 1: Maintain a small in-house wafer fab to prove out each process node but then outsource to a foundry the bulk of production. This is essentially the current STMicroelectronics approach and has the advantage of keeping up with technology, provided the facility is constantly upgraded for future node transitions.

On the face of it Option 1 seems an elegant solution were it not for the fact a small pilot fab will never be cost-effective versus a foundry. Proponents of this route will thus face

perpetual hostility from investors and shareholders: "Why are you wasting money, tying up capital in expensive assets and depleting shareholder value when your outsource supplier is clearly much cheaper than you?" It would take a strong CEO and board to fend off this criticism, more likely than not they would all be fired and replaced by a more 'investor-compliant' team. In the long-term, Option 1 will likely default to Option 2.

Option 2: Stop building fabs completely at a certain process node and then use a foundry for new wafer production. This is the route NXP and Infineon have taken. This is clearly a bipolar structure; IDM up to a certain node and then fabless thereafter.

Unlike Option 1, this strategy is process-terminal, once you exit a fab node it will be virtually impossible to re-enter the wafer manufacturing business. The more generations missed, the greater the impossibility.

Option 2 thus combines the worst of both worlds. For the legacy fabs it ignores the fundamental reality that today's leading edge is tomorrow's commodity, meaning these fabs will slowly become more and more obsolete and harder to fill.

Firms will thus be subjected to a constant closure and restructuring effort, damaging employee morale and affecting costs and productivity. Finding and keeping good operations personnel will be difficult given this business strategy is an operational dead end.

For the new fabless future, Option 2 sidesteps the fact that simply not having a fab does not make you a fabless firm, just a

## The new PicoScope 4000 Series high-resolution oscilloscopes

### PicoScope 4000 Series

firm without fabs; not the same thing at all. The legacy overhead infrastructure and costs and inefficiency will be much higher than with a truly fabless company and overall competitiveness will continue to erode. In short, restructuring from an IDM to a fabless business model will be both 'operationally challenging' and unlikely to make the organisation more structurally competitive. To the contrary, it will more likely have the totally opposite effect and competitiveness will continue to erode. Option 2 thus represents death by slow strangulation.

Aside from the definition and implementation issues, there is also the fundamental underlying problem that fab-lite is based on the shaky assumption that foundry wafers will always be freely available at ever-cheaper prices. This is the chip industry equivalent of the 'debt is freely available and cheap' corporate business model that came to such an abrupt and catastrophic halt in the recent financial crisis. Just as with cheap debt, ever-reducing prices (and profits) whilst simultaneously investing in new process and production technology cannot be sustained forever; they result would be bankruptcy. Structurally prices must eventually increase.

At the same time the chip world is now staring into the eyes of a wafer fab famine, triggered by two or more years of rampant underinvestment. With no hope of fixing this problem near-term – 2010's capacity is already cast in stone, determined by 2009's (lack of) Cap Ex spend – foundry wafer prices will be hit with supply-and-demand price increases. Worse still, they will also be on allocation. Paying a higher price is one thing; not getting the wafers is another matter entirely. No wafers equals no sales – that is a 100% correlation and a major competitive threat.

Structurally deceitful, operationally faulty, 2010 will see the fab-lite 'model' fall to pieces. The so-called fab-lite option is thus nothing short of deception. Fab-smart therefore remains the only true solution, i.e. continuing to build in-house fabs but outsource a modest amount (say 10-15% maximum) to foundries to both smooth the supply and demand peaks and built external fab demand, high enough to justify equipping the next modular in-house expansion. In this way any expansion in capacity enters production 'fully loaded' from the beginning, whilst simultaneously improving response time to near-term demand fluctuation. The foundries do not like this option, of course, but this is the only real competitive reality.

The final part of the delusion? IDM fabs do not have to be wholly owned; there is no reason at all why a jointly owned fab could not work. ■

The PicoScope 4224 and 4424 High Resolution Oscilloscopes have true 12-bit resolution inputs with a vertical accuracy of 1%. This latest generation of PicoScopes features a deep memory of 32 M samples. When combined with rapid trigger mode, this can capture up to 1000 trigger events at a rate of thousands of waveforms per second.

- **PC-based** - capture, view and use the acquired waveform on your PC, right where you need it

- **Software updates** - free software updates for the life of the product

- **USB powered and connected** - perfect for use in the field or the lab

- **Programmable** - supplied with drivers and example code

|               |                                                                                              |

|---------------|----------------------------------------------------------------------------------------------|

| Resolution    | 12 bits (up to 16 bits with resolution enhancement)                                          |

| Bandwidth     | 20 MHz (for oscilloscope and spectrum modes)                                                 |

| Buffer Size   | 32 M samples shared between active channels                                                  |

| Sample Rate   | 80 MS/s maximum                                                                              |

| Channels      | PicoScope 4224: 2 channels<br>PicoScope 4424: 4 channels                                     |

| Connection    | USB 2.0                                                                                      |

| Trigger Types | Rising edge, falling edge, edge with hysteresis, pulse width, runt pulse, drop out, windowed |

Malcolm Penn can be contacted at

[mail@futurehorizons.com](mailto:mail@futurehorizons.com). Future Horizon's website

can be found at [www.futurehorizons.com](http://www.futurehorizons.com)

[www.picotech.com/scope1058](http://www.picotech.com/scope1058)

01480 396395

# FASTER TIME TO MARKET THROUGH RAPID PROTOTYPING

**THE TERM** 'time to market' is often used when referring to the pressure OEMs face when developing new products, but it can be interpreted in many ways. Some may feel that it is a general expression of the overriding need to reduce development costs, while others may say it is in reference to meeting a window of opportunity; crucial to a product's commercial success. While both of these statements are undoubtedly true, the process of reducing time-to-market is more complex and has greater impact than either of these explanations suggest.

The design phase of any product must mix the freedom to develop new ideas quickly, with the discipline of documenting that process. Once in production, the cost effectiveness of a product comes down to two things; how much it costs to produce and how long it can remain in production. Therefore, it is crucial to reach maximum production volume as quickly as possible and for as long as possible. Meeting the former at the cost of the latter can spell disaster for any company; the impact of a product recall is massive, in any vertical sector. Cutting corners at the development stage, therefore, isn't an option.

The process of turning a proof-of-concept into a production-ready device demands stringent adherence to best engineering practice and quality assurance; design validation isn't something that can be rushed or avoided. However, there are ways to cut time to market at the research stage, without sacrificing quality in development.

While the time needed to carry out stringent design validation is difficult to compress, there are effective methods for reducing the initial phases of a design cycle, particularly in reaching proof-of-concept, and rapid prototyping is one approach that we can look at.

Today's embedded products heavily rely on software to define their functionality; software that, wherever possible, is reused or repurposed. Normally, it will also include software developed by a third party. For new products, it is likely that any or all of these software components will need to be revised for their new target. This requires easy access to software modules, and allowing them to be altered or modified without threatening the 'golden' code base. Increasingly, and in response to the trend towards software defined products, software configuration management (SCM) tools are being used to create this so called 'agile' design environment.

Inherently, people are more creative when they aren't constrained to working within rigid parameters. However engineering, as with all disciplines, imposes certain constraints if efforts are to return results.

By definition, rapid prototyping and proof-of-concept are a means

to an end; something that has been developed to justify further investment is rarely intended to form the foundation of a production model without going through rigorous redesign.

It follows, therefore, that reaching the proof-of-concept stage rapidly should not impose undue restrictions on creativity. SCM tools designed to enable this process include features that allow engineers to create branches in the design line of a code base, to evaluate ideas quickly that could, later, simply be removed from the code repository without repercussion, or equally form part of a product variant. For this reason, SCM must also facilitate simple merging of new code back into the code base.

**"THE PROCESS OF TURNING A PROOF-OF-CONCEPT INTO A PRODUCTION-READY DEVICE DEMANDS STRINGENT ADHERENCE TO BEST ENGINEERING PRACTICE AND QUALITY ASSURANCE"**

This 'branch and merge' process isn't unique to SCM tools, but is significantly enabled and eased by them, particularly in those tools that can record the differences between sets of files at different stages of the development cycle. A proven code base can comprise millions of lines of code, while a variant may only represent a small change, by only recording the 'delta' at the

Market dynamics demand faster response times, but not at the expense of good engineering practices, says **Dave Robertson**, director of European operations at Perforce Software

branch and merge stages, the storage space and search time needed to control both the golden code base and any branches are kept to a minimum. The same isn't true with a 'copy and change' philosophy.

The use of SCM tools to control assets described by software IP isn't restricted to just software components; today, most design elements are created and stored digitally, and SCM tools are equally able to manage any asset described in software.

This asset management process can enable the creation of standard platforms, configured when needed, which may be branched to create completely different families of products. These product variants, where relatively small changes at a low level can propagate

into significant differences at a higher level, could be created – and recreated – much more quickly and efficiently using SCM.

It is a practice already being used throughout the industry. As it takes hold, the concept of rapid prototyping will change; no longer will it be used as a differentiator employed by some, but the norm expected by many.

The definition of time-to-market could once again come under scrutiny. Currently, the ability to create a proof-of-concept rapidly offers a competitive advantage. However, customers may come to expect this faster reaction using SCM, because it is both feasible and, perhaps more significantly, makes good commercial and engineering sense. ■

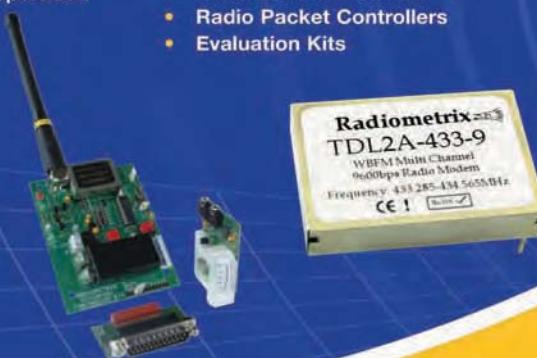

## RADIO MODULES FOR WIRELESS DATALINKS

Radiometrix continues to be recognised as the leading manufacturer of wireless datalinks for a wide variety of applications: it brings to market high-quality yet cost effective VHF & UHF low power radio modules that cater for the needs of OEMs manufacturing for international wireless data transmission industries.

Products available include:

- Narrow Band and Wide Band FM Transmitters, Receivers and Transceivers

- Single Channel and Multi-channel operation

- UHF and VHF ISM bands

- Custom design service

- Encoders and Decoders for RF remote control

- Radio Packet Modems

- Radio Packet Controllers

- Evaluation Kits

Applications include:

- Security & Alarm

- Telecommand or Remote Control

- Telemetry

- Industrial and Commercial

- Data Logging

- Automatic Meter Reading (AMR)

- Tracking

[www.radiometrix.com](http://www.radiometrix.com)

Radiometrix Ltd

Hartcran House

231 Kenton Lane

Harrow, Middlesex

HA3 8RP, UK

Tel: +44 20 8909 9595

Fax: +44 20 8909 2233

sales@radiometrix.com

**RADIOMETRIX**

20 YEARS OF INNOVATION FROM THE PIONEERS IN WIRELESS

# A NEW Year

Myk Dormer

**IT IS TRADITIONAL** around this time of year to optimistically make a list of New Year's resolutions. Maybe we engineers should follow suit?

Here are mine:

- I will always design-in a good, solid ground plane. If it isn't needed it does no harm, but it's really hard to add one later.

- I will think about the aerial at the start of the project. I will not just cram in a roughly quarter wavelength long piece of bell-wire somewhere, as an afterthought.

- I will allow for sufficient shielding at the start. If radiated emissions aren't as high or the circuitry is less sensitive than I thought, then I can always leave the can off in the next version.

- Decoupling is easier to allow for and not fit, than try to squeeze in later or bodge onto early production runs by hand.

- A maximum spec figure is a maximum. It isn't a "Well, I can go a bit over that if I'm careful" figure. It's likewise for minimums.

- Average specifications don't mean very much really. See previous resolution.

- The heat-sink *will* be big enough; under all conditions of airflow and ambient temperature. Just using the ground-plane is not always enough.

- Everyone makes errors. I will allow for one more design/PCB iteration in the project plan than I think I need. (In fact, I think I'll allow for two!)

- Quoted lead times are not there for fun. I will order components well ahead of when they are needed.

- Factory yields are never 100%, so production batches will always have one or two extra units added. (Any excess can always be used as sample stock.)

- I will not use single sourced parts unless I am absolutely certain of the supplier, or there is really and truly no alternative. Even then, I will lay in a plan of action in the event of the critical part going obsolete/unavailable/extended lead-time; even if that plan requires a re-design.

## "I WILL THINK ABOUT THE AERIAL AT THE START OF THE PROJECT. I WILL NOT JUST CRAM IN A ROUGHLY QUARTER WAVELENGTH LONG PIECE OF BELL-WIRE SOMEWHERE, AS AN AFTERTHOUGHT"

- I will only design in components that I know I can source. If the MOQ is three thousand and I'll only ever need fifty, I'll find another part; not just blame the purchasing guy.

- I will not design in the over-hyped, easy-to-use component. I will do the work and design in the right parts, even if it takes more effort.

- I will not mistake my simulator results for real test data.

- I shall hold grudges. I will remember which component suppliers have withdrawn good parts in the past or who have unreliable supply policies, or simply bad quality. I will blacklist them.

- I will not keep a bad design in production. Factory production yield figures matter. I will keep track of build failure rates and if they are unacceptably high, I will do the work and find out why. And then, if necessary, re-design.

- The technical author is not a mind-reader or a psychic. I will write copious notes on which they can base the data sheet, and if they need more information, they'll get it.

- When I write specifications, I will not lie. Not even about maximum radio link range. I will not "just double it, to make it look good" nor will I use free-field calculations for terrestrial links.

- My code will include comments, version control numbers, and will be documented and backed up. Old versions will be archived (just in case my 'upgrade' isn't all I hoped).

Like all New Year resolutions, I imagine most of these will barely last into February. The pressures of real production and design schedules will begin to bite, the number of working hours in the day will move back into two figures and the weekend becomes just two more workdays again ... but there's one resolution that's got to hold:

Test everything! Only real measurements on real hardware are worth anything.

Happy 2010!

*Myk Dormer is Senior RF Design Engineer at Radiometrix Ltd

[www.radiometrix.com](http://www.radiometrix.com)*

# The World's Lowest Sleep Current MCUs: PIC® MCUs with nanoWatt XLP Technology

**Microchip's PIC® Microcontrollers with nanoWatt XLP Technology offer the industry's lowest currents for sleep, where extreme low power applications spend up to 99% of their time.**

- **Extend Battery Life**

- Sleep current down to 20 nA

- Brown-out Reset down to 45 nA

- Watchdog Timer down to 400 nA

- Real time clock down to 500 nA

- **Extreme Flexibility**

- 5 different low power modes to improve power & performance in your application

- Many low-power supervisors, alarms, and wake-up sources

- **Expanded Peripheral Set**

- Integrated USB, LCD, RTCC & touch sensing

- Eliminates costly external components

## GET THE MOST FROM YOUR BATTERY IN YOUR NEXT DESIGN!

1. View the Low Power Comparison demo

2. View free Webinars and Application Notes

3. Download the Low Power Tips 'n Tricks

4. Order samples and development tools

[www.microchip.com/XLP](http://www.microchip.com/XLP)

## Intelligent Electronics start with Microchip

**microchip**

**DIRECT**

[www.microchipdirect.com](http://www.microchipdirect.com)

[www.microchip.com/XLP](http://www.microchip.com/XLP)

**MICROCHIP**

# WaveAce Oscilloscopes

**LeCroy Expands Entry-level Oscilloscope Series to Include 4 Channel and 40 MHz Models from just £550 for Simple and Efficient Debug now from 40 MHz to 300 MHz**

LeCroy® Corporation today announced that it is expanding the popular WaveAce™ oscilloscope line to include 4 channel models from 60 MHz to 300 MHz and adding a new 2 channel, 40 MHz model. The 4 channel models provide 10 kpts/ch memory and up to 2 GS/s sample rate; the 40 MHz model provides 4 kpts/ch and a sample rate of up to 500 MS/s. All models offer long memory, large colour displays, extensive measurement capabilities, and advanced triggering to improve troubleshooting and shorten debug time. With USB host and device ports, plus a LAN connection, the WaveAce oscilloscopes easily connect to a memory stick, PC or printer for saving data or remote control. Combined with the streamlined, time-saving user interface, these features make the WaveAce oscilloscopes the ideal tools for affordable design, debug and troubleshooting from 40 MHz to 300 MHz.

## Deep Feature Set for Better Debug

Available in bandwidths of 60 MHz, 100 MHz, 200 MHz and 300 MHz, the new 4 channel models provide a maximum sample rate of 2 GS/s and up to 10 kpts/ch memory or 20 kpts when interleaved. The long memory allows users to capture full sample rate acquisitions that are two to three times longer than the competition. With 32 built-in automated parameters, including advanced timing parameters for skew, phase and edge-to-edge measurements between channels, the WaveAce oscilloscope broadens the ways a user can understand and analyze waveforms. Additional features such as Pass/Fail testing, user definable digital filters and a waveform sequence recorder simplify and shorten debug time.

## Remote Control via USB and LAN Ports

A new remote control command set has been implemented in the 4 channel models to make the WaveAce even more useful and versatile than ever before. This modern remote control command set provides access to all of the WaveAce controls, functions and

measurements from a remote PC via the rear panel USB or LAN ports. These connections also allow the user to remotely view the waveform display and access a virtual front panel.

## Saving and Documenting Results

Documenting results and saving screenshots, waveforms and setups are easy with the WaveAce. Internal storage can hold up to 20 waveforms and 20 setups. Mass storage can be done by connecting a USB memory device directly to the front panel of the oscilloscope. The rear panel USB port allows for direct printer connection to quickly generate hard copies of the screen image.

## Easy to Use for Faster Debug

The high performance and large feature set of the WaveAce is controlled by an intuitive user interface with 11 different languages and streamlined front panel. All important controls and menus are accessed from the front panel with a single button press. All position and offsets can be reset by simply pressing the knob, pressing the V/Div knob will switch between fixed and variable gain and pressing the T/div knob will toggle between zoom modes. Buttons on the front panel that open and close menus or switch modes are backlit to let the user know exactly what mode the WaveAce is operating in.

## Pricing

The 40 MHz WaveAce 101 price is £550 while prices for the new 4 channel models range from £1,160 to £ 2,210.

# LeCroy

# WaveAce Oscilloscopes

# 40 MHz – 300 MHz

FROM

**£550\***

The New Affordable Oscilloscopes

from the Manufacturer of the

Fastest Oscilloscopes in the World

- 40 MHz – 300 MHz Bandwidth

- 2- and 4-Channel Models

- Up to 2 GS/s Sample Rate

- Up to 20 kpts Memory

- 5.7" Colour Display in all models

- Class Leading Math and Measurements

- Advanced Trigger

- LAN/USB Connectivity

- 3 Years Warranty

[www.lecroy.co.uk](http://www.lecroy.co.uk)

Phone: 01235 - 536973

\*Launch Special Offer valid until 31 March 2010

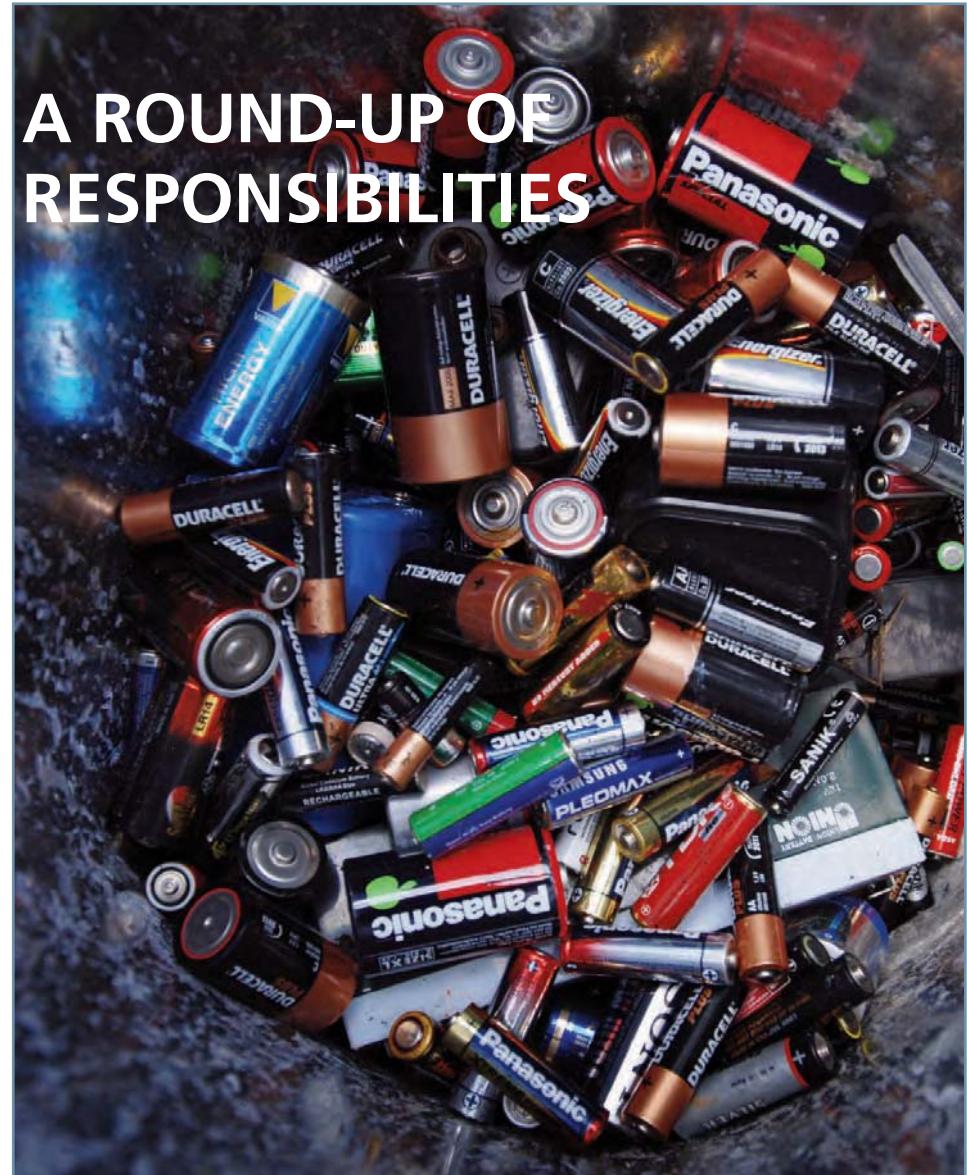

# BATTERIES REGULATIONS: A ROUND-UP OF RESPONSIBILITIES

**Bob Mead, Batteries Implementation Project Manager for the Environment Agency, gives an update on the Batteries Directive and how to ensure stay within the law**

**THE 'NEW'** Batteries Regulations came into force on 5 May 2009 and every producer and distributor must now comply.

It's extremely important to understand the terminology. Vitally, a producer is not necessarily the battery manufacturer. It is whoever places them on the UK market for the first time.

The definition of producer also applies when batteries are included within other products. Many products, from computers to animated toys, contain them. Some are less obvious than others; for example many DVD players and all desktop PCs contain batteries, as does any product with a clock or memory that works when it's unplugged from an electricity supply.

If you incorporate batteries in any product, you need to understand whether they have already been placed on the market. If you purchase them from a wholesaler they probably have, but if you buy them direct from the manufacturer or importer, they may not. This is a particular issue for battery pack manufacturers. If individual battery cells which combine to make up your pack had not already been placed on the market, then you will place them on when you sell the packs, and you are therefore the producer.

The directive seeks to reduce the environmental impact of batteries and

*New regulation applies to batteries*

accumulators. The UK has targets to increase from recycling 3% of portable batteries (2007 figures) to 25% (7,500 tonnes) by 2012 and to at least 45% by 2016.

This must all be in line with existing controls, including Health and Safety, Carriage of Dangerous Goods, Environmental Permitting and Hazardous Waste.

All batteries placed on the UK market must also be compliant with the requirements of 2008's Batteries and Accumulators (Placing on the Market) Regulations. These set limits for levels of cadmium and mercury in new batteries, and impose marking requirements. Visit [www.berr.gov.uk](http://www.berr.gov.uk) for more information.

Every producer must now record the weights and types of batteries they place

on the UK market. In January 2010 figures for 5 May to 31 December 2009 must be reported, broken down by weight of lead-acid, nickel cadmium and 'other'.

If you are responsible for automotive or industrial batteries the rules are slightly different. Again, see [www.berr.co.uk](http://www.berr.co.uk) for information.

The Government distinguishes between 'large' and 'small' producers. 'Large' producers place more than one tonne of portable batteries onto the UK market annually. They must pay for the collection, treatment, recycling and disposal of waste batteries in proportion to their market share. If this applies to you and if you have not already done so, you need to join a Battery Compliance Scheme (BCS) as soon as possible, as the deadline for doing so was 15 October. The BSC will also register

you with the appropriate environment agency (England & Wales; Scotland; or Northern Ireland).

'Small' producers place one tonne or less of portable batteries onto the UK market annually. They do not have to pay for the collection and treatment of waste. If this applies to you, you must, however, register with your relevant environment agency within 28 days of the first date on or after 15 October 2009 on which you place any batteries onto the UK market. You can do

**IN THE CONTEXT OF THE BATTERIES DIRECTIVE, A DISTRIBUTOR IS ANYONE WHO SUPPLIES BATTERIES ON A PROFESSIONAL BASIS TO AN END USER; THIS IS USUALLY A RETAILER BUT IT CAN BE A WHOLESALER FOR ALL OR PART OF THEIR BUSINESS**

Disposable batteries

this quickly and easily online at [www.environment-agency.gov.uk/batteries](http://www.environment-agency.gov.uk/batteries).

Following an assessment period we approved seven BCSs to serve the UK market. You can find details on these at [www.environment-agency.gov.uk/batteries](http://www.environment-agency.gov.uk/batteries). Producers can join whichever approved scheme best suits their needs, regardless of where in the UK they are based.

In the context of the Batteries Directive a distributor is anyone who supplies batteries on a professional basis to an end user. This is usually a retailer but it can be a wholesaler for all or part of their business.

If this applies to you, and you sell over 32kg of portable batteries annually to end

users, you must offer a battery take-back facility from 1 February 2010. Batteries within products do not count when calculating the 32kg. You must accept any portable batteries, not just those you sell, and regardless of any purchase by the depositor. You do not, however, have to pay for their transport and treatment: approved BCSs are obliged to collect them free of charge.

If you sell less than 32kg to end users you do not have to accept waste batteries. BCSs are obliged to accept them from you if you do, but they do not have to collect them. It's advisable to check the situation before deciding to offer take-back facilities. ■

## FURTHER INFORMATION ON THE BATTERIES DIRECTIVE

You can get further information on portable batteries at [www.environment-agency.gov.uk/batteries](http://www.environment-agency.gov.uk/batteries) or by phoning our helpline on 08708 506506.

Contact Defra regarding questions about distributor take-back. Email [portable.batteries@defra.gsi.gov.uk](mailto:portable.batteries@defra.gsi.gov.uk).

For queries on automotive or industrial batteries contact **BIS at [batteryconsultation@berr.gsi.gov.uk](mailto:batteryconsultation@berr.gsi.gov.uk)**

Defra's advice on the regulations are at [www.defra.gov.uk/environment/waste/producer/batteries/documents/0907-advisory-note.pdf](http://www.defra.gov.uk/environment/waste/producer/batteries/documents/0907-advisory-note.pdf)

**Professor Alan Burns** of the Department of Computer Science at the University of York and **Chris Dale**, events co-ordinator for the Safety-Critical Systems Club, explore the scheduling and timing analysis techniques necessary for safety critical, real-time operating systems

# Scheduling and Timing Analysis for SAFETY-CRITICAL REAL-TIME SYSTEMS

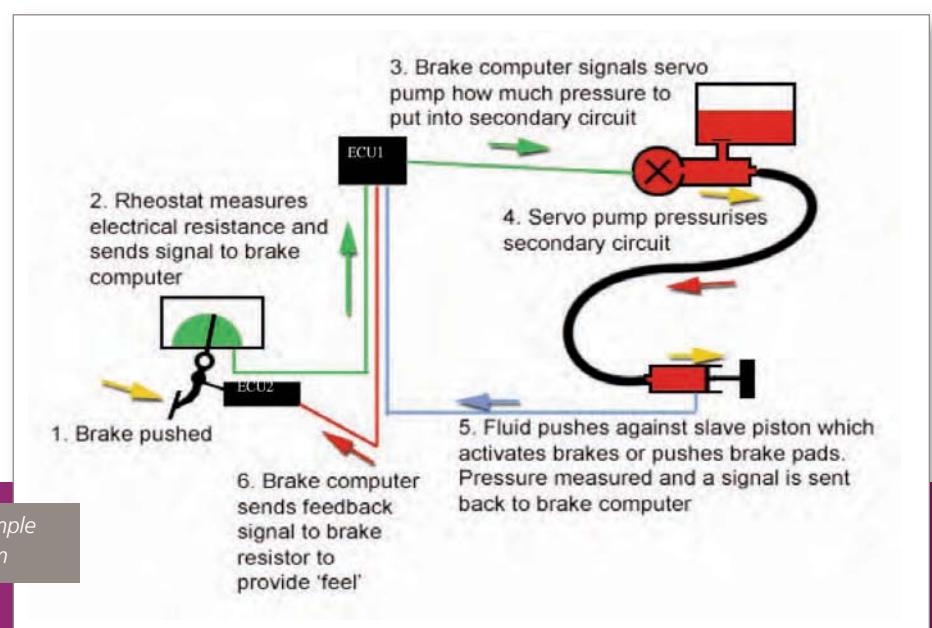

**THE CAR YOU** drive almost certainly depends for its safe operation on concurrent software executing within embedded systems. And as brake-by-wire, steer-by-wire and throttle-by-wire systems become more common-place, your safety will become ever more dependent on the timing properties of these systems.

The diagram in **Figure 1** represents a brake-by-wire system. Its control unit (ECU1) reads the sensors, computes the outputs, writes the outputs to the actuators (e.g. ECU2) and resets the watchdog timer – set to 20ms. This system worked fine, but after a small change in the software the steering mechanism became wobbly. What had happened? The computation task now overran its assumed Worst Case Execution Time (WCET), failing to reset the watchdog timer and resulting in a very frequent full system reset!

This is exactly the kind of problem that scheduling and timing analysis is intended to deal with. And it's easy to see that this problem is a relatively simple one: the car has many more such embedded systems, for engine control, air conditioning, lighting, navigation, etc; fly-by-wire aircraft are even more complex.

Verification of the timing properties of safety-critical real-time systems, and looking

at the standard ways of scheduling and analysing the concurrent software that typically executes within embedded systems, are techniques crucial for safety-critical systems, where there is a need for a high level of assurance that timing constraints will be satisfied in all situations, even those that are very rare.

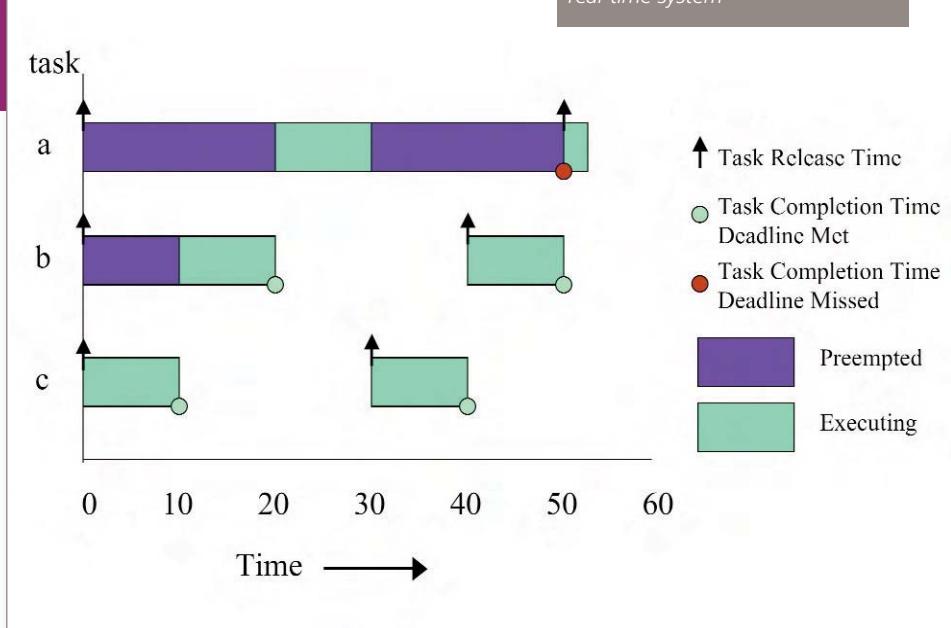

## Scheduling and Timing Analysis

So what are scheduling and timing analysis, and how do they differ? You can think of a real-time application as a collection of concurrent tasks that repeat, either periodically or sporadically, and that are either time-triggered or event-triggered. Timing analysis is concerned with the

temporal behaviour of individual tasks, while scheduling analysis deals with the temporal behaviour of the whole system.

In scheduling analysis, a scheduling scheme has two features: an algorithm that orders the use of system resources (in particular the CPUs), and a means of predicting the worst-case behaviour of the system when the scheduling algorithm is applied.

Many hard real-time systems are implemented as cyclic executives. This means that the application code is produced as a collection of procedures, each procedure is mapped onto a 'minor cycle', and the minor cycles together make up the complete schedule (or 'major cycle') of the application. The main advantage of cyclic executives is

**Figure 1:** Brake-by-wire – an example of a safety-critical, real-time system

**Figure 2:** Time-line for a simple real-time system

that they are fully deterministic: the cycle times are fixed and individual procedures complete within their respective cycles.

However, this determinism comes at a price: each task period has to be a multiple of the minor cycle time; tasks with long periods are difficult to incorporate; and it is just about impossible to accommodate sporadic activities. This means that cyclic executives are difficult to construct and difficult to maintain. In particular, any task with a sizable computation time must be split into a number of fixed sized procedures; this may cut across the structure of the code from a software engineering perspective and, hence, may be error-prone – not what you want in a safety-critical system. So, although the determinism of cyclic executives may be appealing, predictability of worst-case behaviour is more important, and this can be achieved without having to work within the limitations of cyclic executives.

### Non-Deterministic Approach

The most widely used non-deterministic approach is known as Fixed-Priority Scheduling (FPS). Under this scheme, each task has a fixed, static, priority which is computed before run-time, and tasks are executed in the order determined by their respective priorities. In real-time systems, the priority of a task is derived purely from its timing requirements, not from its importance to the correct functioning of the system or its integrity.

But what if a high-priority task is released while a lower-priority one is already

executing? There are two possibilities: in a 'pre-emptive' scheme, there will be an immediate switch to the higher-priority task; with non-pre-emption, the lower-priority task will be allowed to complete before the other can start. Because pre-emptive schemes enable higher-priority tasks to be more reactive, they are preferred.

So how does this work in practice? Suppose, for the moment, that an application is made up of a fixed number of tasks, each with its own known period, each independent of all the others, each with a deadline equal to its period and each with a fixed worst-case execution time. We're also going to ignore all the system overheads. Task priorities are assigned according to Rate Monotonic Priority Assignment – i.e. the shorter the task's period, the higher its priority; this is the optimal way of assigning priorities in an FPS scheme with task deadlines equal to their periods. The utilisation of each task is defined as its computation time divided by its period and is the proportion of the time that the task would be executing, if left uninterrupted by others.

**Table 1** lists the three tasks that make up a simple real-time application. Task 'c' has the shortest period, so it has the highest priority, and thus executes first – as shown in **Figure**

**2**; tasks 'a' and 'b' are also ready to execute at time zero, but they are pre-empted by the higher-priority task. Once task 'c' has completed, task 'b' executes, and only then can task 'a' begin. However, before task 'a' can complete its execution, it is pre-empted again, first by task 'c' and then by task 'b', and thus fails to complete before it is due to recommence at time 50. So, in this example, it is impossible to schedule the tasks within the given constraints.

In general, it is not necessary to analyse tasks to the level of detail given in this example, which would be quite onerous even for a moderately complicated application. Instead, tests based on the utilisation levels of tasks can be applied to show whether a given application can be scheduled: provided the total utilisation of all the tasks is less than a threshold value that depends on the number of tasks, they can be scheduled.

In the example above the total utilisation is 0.82, which is greater than the threshold value of 0.78 for three tasks, so this application fails the test. But these tests are sufficient, not necessary – in other words, while passing the test shows that the application can be scheduled, failing the test does not show that it cannot be scheduled. To overcome this problem, a more complicated response-time analysis can be

applied in cases of doubt, resulting in a necessary and sufficient test for schedulability.

### Classified Tasks

The above description of FPS assumed that the tasks were all periodic, but it can be generalised to include sporadic tasks (those whose arrival times are not regular). However, in many situations the worst-case rates of arrival for sporadic tasks are considerably higher than the averages – e.g. interrupts often arrive in bursts and an abnormal sensor reading may lead to significant additional computation. This means that schedulability calculations made using worst-case figures may lead to very low processor utilizations being observed in the actual running system.

To overcome this, tasks are classified as ‘hard’ or ‘soft’: a hard task is one for which execution after its deadline is of no value (e.g. because it leads directly to system failure), and a soft task is one where missing the deadline can be tolerated, albeit with the possibility of decreased service quality. This leads to two rules that can be used to guide schedulability analysis:

1. All tasks should be schedulable using average execution times and average arrival rates.

2. All hard real-time tasks should be schedulable using worst-case execution times and worst-case arrival rates of all tasks.

Rule 1 means that there may be situations in which it is not possible to meet all current deadlines; this condition is known as a transient overload. Rule 2 ensures, crucially, that no hard real-time task will miss its deadline. If it turns out that rule 2 gives rise to unacceptably low utilizations for ‘normal execution’, then action must be taken to reduce the worst-case execution times (and/or arrival rates).

The above analysis assumed that task deadlines were equal to their periods – i.e. they needed to complete before they were due to restart. In some circumstances, task deadlines may need to be less than their periods, and in these cases a different priority scheme is used: Deadline Monotonic Priority Ordering (DMPO), in which the highest priority

| Task | Period | Computation Time | Priority | Utilisation |

|------|--------|------------------|----------|-------------|

| a    | 50     | 12               | 1        | 0.24        |

| b    | 40     | 10               | 2        | 0.25        |

| c    | 30     | 10               | 3        | 0.33        |

**Table 1:** The list of three tasks that make up a simple real-time application

task is the one with the shortest deadline.

Unfortunately when deadlines are no longer equal to periods, the utilisation-based method of checking for schedulability is no longer effective. Rather, the response-time of each task must be calculated and then compared with the task’s deadline.

In some circumstances, where tasks share resources, it is possible for a task to be suspended waiting for a lower-priority task to complete some required computation. This situation is known as priority inversion and the task waiting on a lower-priority task is said to be blocked. Such a problem nearly led to the loss of the Mars Pathfinder mission: as a shared bus became heavily loaded, critical data was not being transferred; time-out on this data was used as an indication of failure and led to re-boot. In this instance, the problem was resolved through an appropriate patch. In general, response time analysis can be extended to cope with the blocking of resources.

### Timing Analysis

In order to be able to apply the scheduling analysis outlined above, we need some knowledge of the timing of individual tasks. But the time a task takes to execute, even on a fixed hardware platform, is not a fixed quantity – it will vary depending on the system state and on the particular data values being processed. Consider the following:

- Best-Case execution time. This is the shortest possible time taken to execute the task. To use this in a scheduling analysis would be grossly optimistic.

- Average execution time. As we saw above, for soft tasks, it can be acceptable to use the average execution time as the basis of scheduling analysis.

- Maximum observed execution time. It is very unlikely that the worst possible (in terms of timing) set of inputs would be encountered during any particular regime of testing. Thus, it would be unwise, and possibly unsafe, to use the maximum observed execution time in a scheduling analysis for hard real-time tasks.

● Worst Case Execution Time (WCET). For any task running on a particular hardware configuration, there is a worst case execution time, but it may not be practically possible to determine what this is (for reasons such as the complexity of the task). Thus, although this figure would be acceptable and safe to use for scheduling analysis, it may be simply unobtainable.

● WCET Upper Bound. In the absence of perfect knowledge about WCET, some means of obtaining an upper bound on the WCET is needed. This constitutes a pessimistic but safe approach to timing analysis for hard real-time tasks within safety-critical systems.

Detailed guidance about how to obtain WCET Upper Bounds, and further detail on scheduling analysis, can be found in *Real-Time Systems and Programming Languages* by Alan Burns and Andy Wellings (fourth edition, 2009, Addison Wesley).

Among the tools available for worst-case execution time analysis are those of Rapita Systems Ltd ([www.rapitasystems.com](http://www.rapitasystems.com)), a spin-off from the Real-time Systems Research Group at the University of York. ■

**The Safety-Critical Systems Club (SCSC)** exists to raise awareness and facilitate technology transfer in the field of safety-critical systems. It does this through a programme of seminars and tutorials, its annual three-day symposium and a newsletter circulated to its membership.

The Club is a non-profit organisation operated by the Centre for Software Reliability at Newcastle University. More information about SCSC events, publications and membership can be found at [www.scsc.org.uk](http://www.scsc.org.uk).

# ECO-DESIGN A CARBON APPROACH WEBINAR

**17 February 2010 at 10.00

Register Today!**

- A topical and interactive forum for eco design.

- Find out how you could benefit from design in a low carbon economy.

- Live demonstrations will examine low carbon design principles.

- Rob Holdway, our design expert will be on hand to advise on implementing a design strategy.

**Register online today

[www.envirowise.gov.uk/webinar](http://www.envirowise.gov.uk/webinar)**

# Realistic Implementation of GUIDELINES

**Griff Derryberry**, Zuchen Applications Engineer, in this article looks at each of the roles of the engineer and PCB designer; considers the traditional design process and makes suggestions on how the designer can contribute significantly to improving a design's overall signal integrity whilst saving time

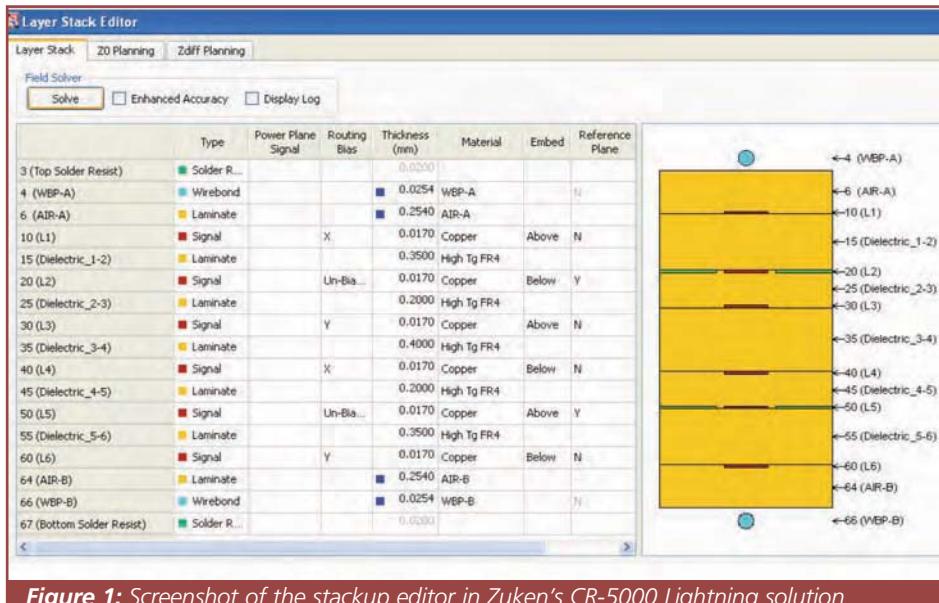

**PICK UP ANY PCB** or electronics design magazine and probably at least one article will be devoted to some aspect of high-speed digital design; be it routing techniques, signal integrity analysis, electromagnetic compatibility or power integrity. This has now become a mainstream design practice.

Being able to achieve successful designs repeatedly suggests that a honed process is in place – one that captures electrical intent, enables design realization and promotes verification to ensure that the product delivered matches the requirements and specifications. However, having in place such a formal process is often more an ideal than a reality.

Realizing products with significant high-speed digital content requires the engineer to operate in different specialties. Besides performing circuit design, he or she needs to

evaluate the design's signal integrity, apply mitigation techniques and all the while keeping in mind the physical limitations of the board. The time an engineer can devote to such activities is usually a fraction of the overall design time, with the majority being spent on researching parts, attending design reviews, testing the design in the lab and participating in numerous meetings. This also usually means that an in-depth, post-layout analysis of the product is compromised.

So what can be done to improve the situation? This article looks at each of the roles of the engineer and PCB designer, considers the traditional design process and makes suggestions on how the designer can contribute significantly to improving a design's overall signal integrity, while simultaneously saving time so that the engineer can focus on more in-depth issues.

## Context

The PCB designer works closely with the engineer who also works under a tight schedule. The designer's role is to physically realize the design as outlined by the engineer vis-à-vis constraints as quickly as possible. Because the engineer often has to manage a constant stream of changes, in turn the PCB designer has to be patient and implement these at whatever point in the design process they are required.

Traditionally, the main urgency to complete the layout is to obtain a prototype so that the engineer can test the product in the lab – getting to this stage is often set as a design process milestone. However, gaining access to probe signals in today's high-speed designs can be difficult, due to component packaging.

One option to help mitigate this issue is to have a signal integrity (SI) analysis tool in the design environment. Yet, having access to an SI analysis tool versus implementing the practice of SI analysis as part of the design process are two entirely different states. Further, performing SI analysis has been perceived historically as a black art, requiring specialist knowledge and skill set. Some companies even have an entire group dedicated to performing this task.

The traditional design schedule does not

Figure 1: Screenshot of the stackup editor in Zuchen's CR-5000 Lightning solution

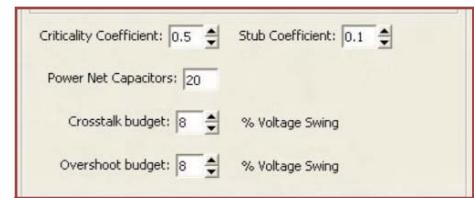

Figure 2: The designer can constrain the design automatically for crosstalk, overshoot and stub length

# Signal Integrity Screening FOR PCB DESIGNERS

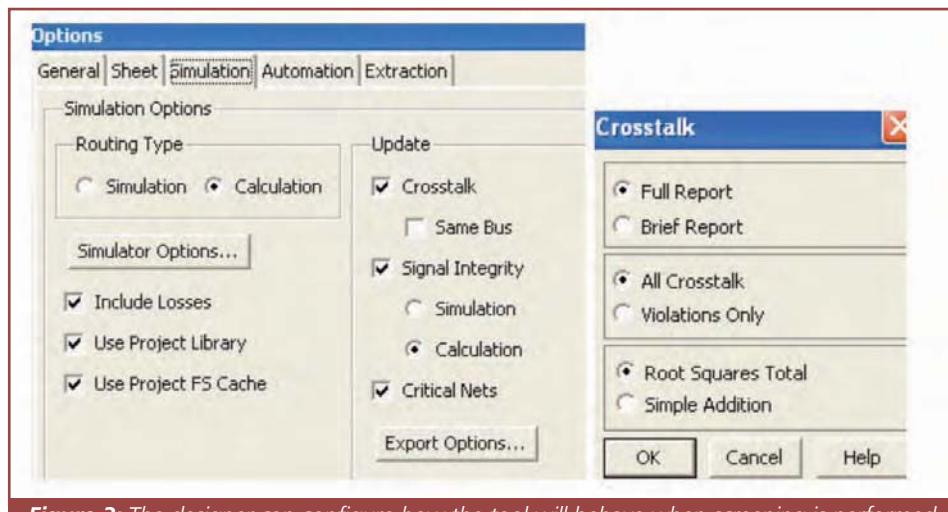

Figure 3: The designer can configure how the tool will behave when screening is performed

promote this activity and to incorporate it now into the schedule does not remove the need for examining the product in the lab. Consequently, the perception could be that adding SI analysis to the design process gives the electrical engineer another job to do, in addition to their already long list of actions. But this can be perceived as a somewhat limited view as the benefits of addressing signal integrity up front can be vast, both in time and money savings – enabling the design team to deliver boards that are going to be right-first-time.

## PCB Designer Best Positioned to Resolve SI Issues Early

In traditional-style development organizations, the engineer does not look at SI issues until the board is completely placed and routed. Any issues the engineer finds are flagged and sent back to the designer. In order to complete the design, several iterations of

this SI review cycle may occur. However, if the design environment includes a PCB design tool that incorporates constraint management with the ability to analyze signal integrity, as in the case of Zuken's CR-5000 Lightning Realize solution, the PCB designer becomes the person best positioned to improve a design from a high-speed design standpoint; as part of the layout process, the designer can perform first-pass signal integrity checking. Through this SI screening, the designer makes the design

process more efficient by greatly reducing the number SI review cycles, thereby saving time and money.

The advanced capabilities of today's design tools that are available to the PCB designer mean that in one application, the designer can realize the placement and routing as guided by physical and electrical rules (constraints), and then screen for crosstalk and signal quality without needing a deep understanding of electrical theory. Solutions such as CR-5000 Lightning from Zuken are so sophisticated that the designer can effectively resolve some lesser issues that were once only solvable by the engineer, therefore reducing the number of actions on the engineer's to-do list.

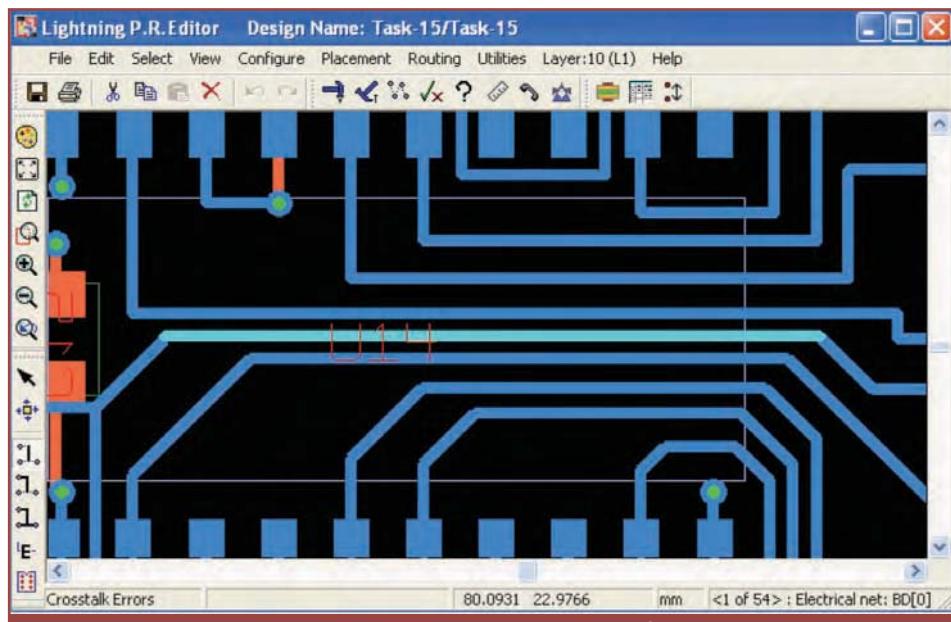

As CR-5000 Lightning is such a powerful environment, the PCB designer is able to perform signal integrity screening as a fluid part of the PCB design process. Issues are presented in a spreadsheet alongside corresponding constraints, and crosstalk hotspots can be highlighted on the PCB design 'canvas'. The designer can then resolve these issues by manual or automated means. In this preliminary look at signal integrity, there is no need to involve the engineer, thereby saving the engineer time that can be used to look at more significant SI issues later in the design cycle.

| All Constraints   Crosstalk   Distortion   Impedance   Delay   Misc   Modeling   Lengthening   Multi-board   Skew |           |                    |                        |                        |                           |                           |                                 |                                 |

|-------------------------------------------------------------------------------------------------------------------|-----------|--------------------|------------------------|------------------------|---------------------------|---------------------------|---------------------------------|---------------------------------|

|                                                                                                                   | Aggressor | Max crosstalk (mV) | Min RSS crosstalk (mV) | Max RSS crosstalk (mV) | Min simple crosstalk (mV) | Max simple crosstalk (mV) | Min crosstalk Contribution (mV) | Max crosstalk Contribution (mV) |