# ELECTRONICS WORLD

THE ESSENTIAL ELECTRONICS ENGINEERING MAGAZINE

Volume 117 • Issue 1900

April 2011 • £4.60

[www.electronicsworld.co.uk](http://www.electronicsworld.co.uk)

## ADDRESSING CLOCK TREE CONSIDERATIONS FOR 4G BASESTATIONS

TECHNOLOGY

LIGHT CAN

CONTROL

GRAPHENE

PRODUCTS

NEW SCOPES,

SENSORS AND

ECOSYSTEMS

USB DESIGN

USB FLASH

DRIVE FOR DATA

DISTRIBUTION

ALSO IN THIS ISSUE: THE TROUBLE WITH RF: GOING TO THE FAIR • LETTERS

# Simply more Oscilloscope

## WaveRunner 6 Zi 400 MHz – 4 GHz Oscilloscopes

The new WaveRunner 6 Zi defines superiority in a test instrument with a powerful feature set including a wide range of application packages, advanced triggering to isolate events, an innovative display concept with a user interface developed for quick and easy navigation, a wide range of probing options, and lightning-fast performance.

- 400 MHz – 4 GHz Bandwidth

- Up to 40 GS/s Sample Rate

- Up to 128 Mpts Analysis Memory

- Rotating 12.1" Widescreen Touchscreen

- Excellent Signal Fidelity

- Low noise fans

- Budget-friendly Prices

- 12-bit Oscilloscopes available from May 2011

[www.lecroy.com/europe](http://www.lecroy.com/europe)

Tel. +44 1753 725371

**LeCroy**

## REGULARS

Dear Readers,

We'd like to inform you that **Electronics World** magazine will no longer be available to purchase through news trade means commensurate from the June 2011 issue. Nevertheless, the magazine will continue to be available to order – as usual – via subscription directly from our publishing house, either in print or digital version, as our commitment to provide a quality product to our readers continues unabated. For further information and pricing please visit our website at [www.electronicsworld.co.uk](http://www.electronicsworld.co.uk)

Svetlana Josifovska, Editor, Electronics World

## FEATURES

06

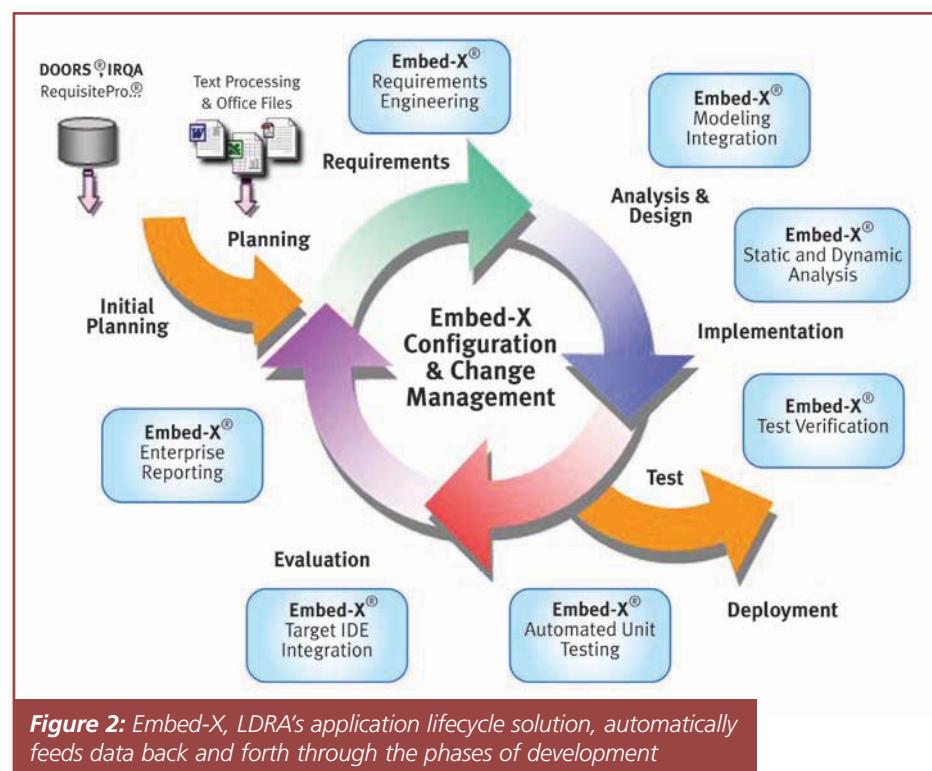

## 16 NEW METHODOLOGIES AND INNOVATIONS FUEL SYSTEM REALIZATION

**Steve Brown** and **Raj Mathur** explain the need for a new system design approach that allows both earlier software development and faster silicon development, along with earlier and more frequent system integration steps

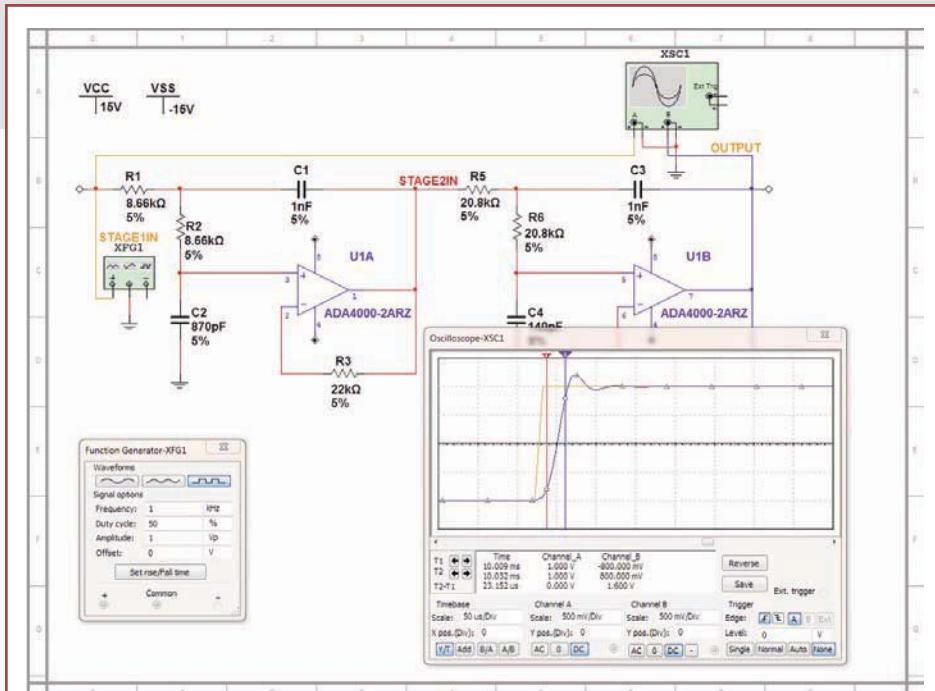

## 20 A RECIPE FOR BETTER SYSTEM BLOCK DESIGN – ADD SPICE

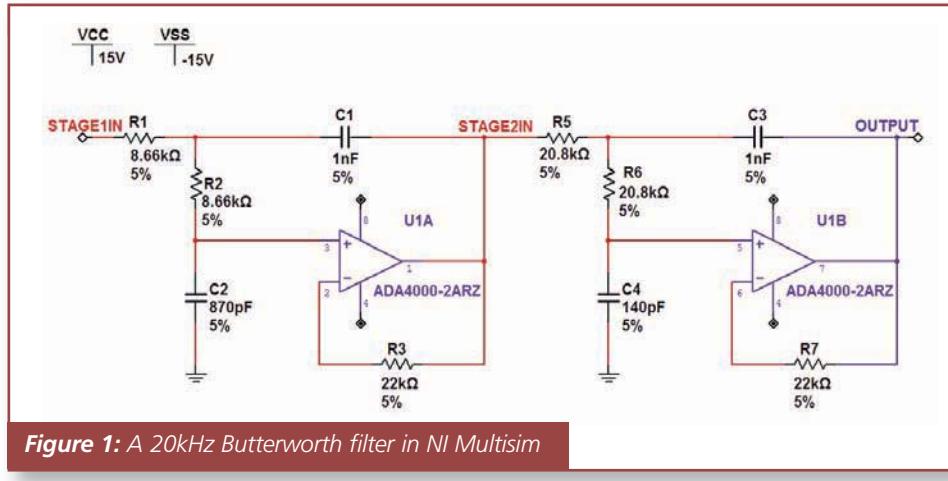

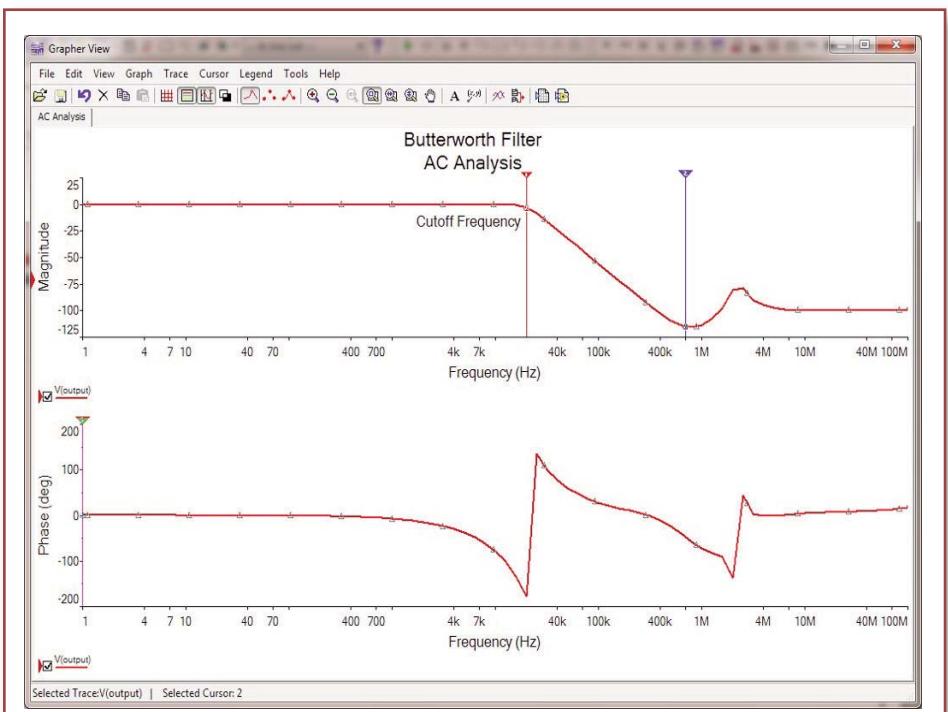

**Reza Moghimi** and **Natasha Baker** explain that new tools provide a holistic approach to circuit design and validation

## 24 ADVANCING THE ART OF SYSTEM DESIGN

**Arun Mulpur** discusses the significant recent advances in modelling, simulation and code generation tools and methods

## 30 INSIGHTS FROM THE COUVERTURE PROJECT'S R&amp;D EXPERIENCE

**Olivier Hainque** charts AdaCore's experience with the French R&D project called Couverture that resulted in two new tools for safety critical applications

## 33 MEDICAL DEVICE SOFTWARE: WHY HAS IT GONE CODE RED?

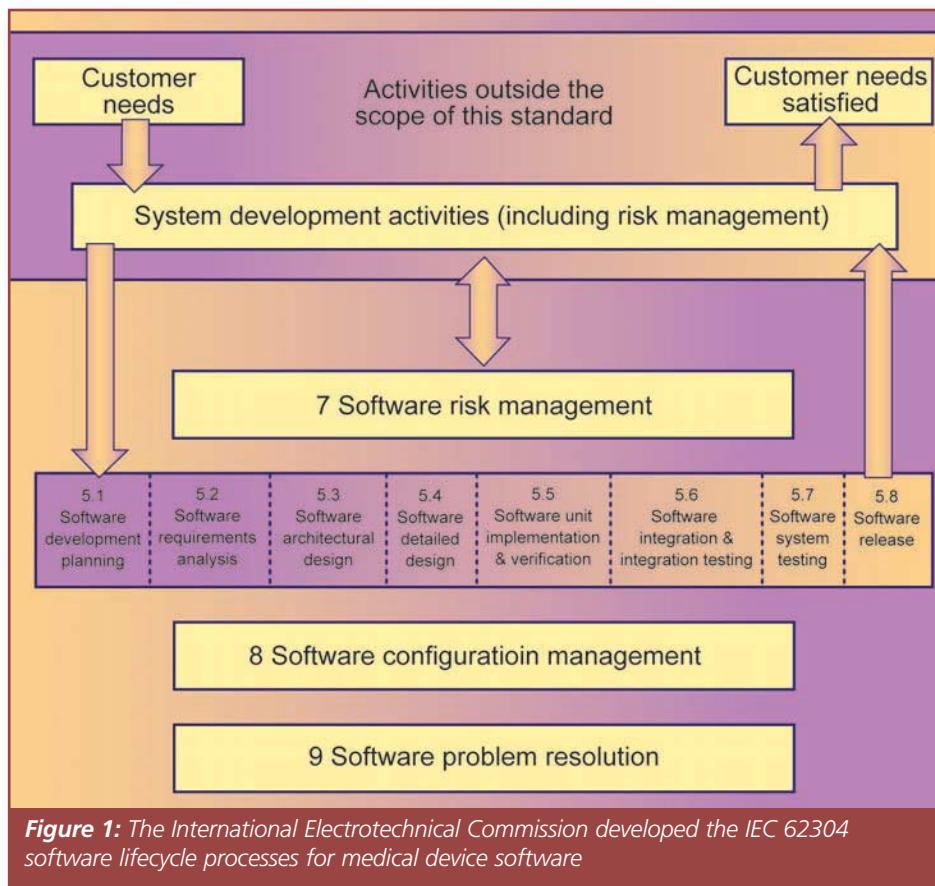

**Nat Hillary** explains that industries such as avionics have shown that seeking certification of a safety-critical software project drives the adoption of repeatable software development processes ; this applies to developers of medical devices too

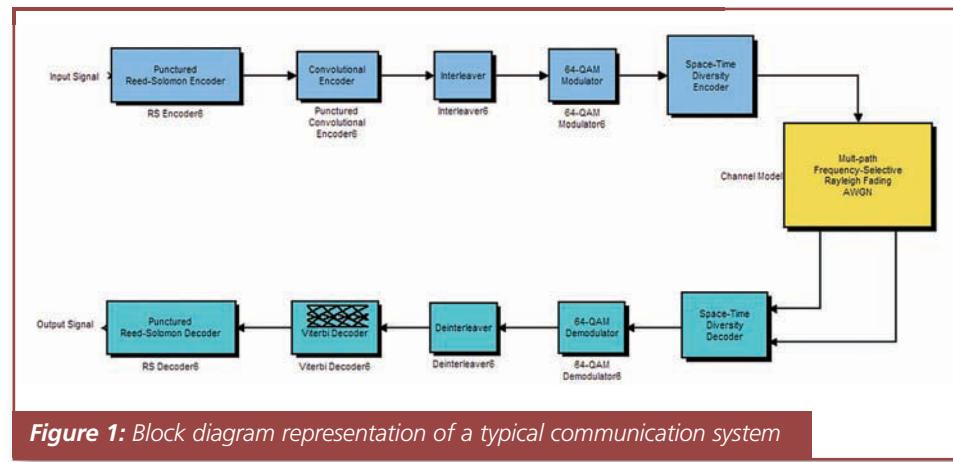

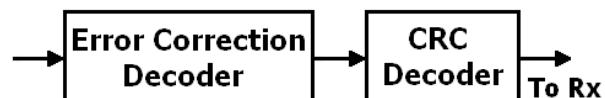

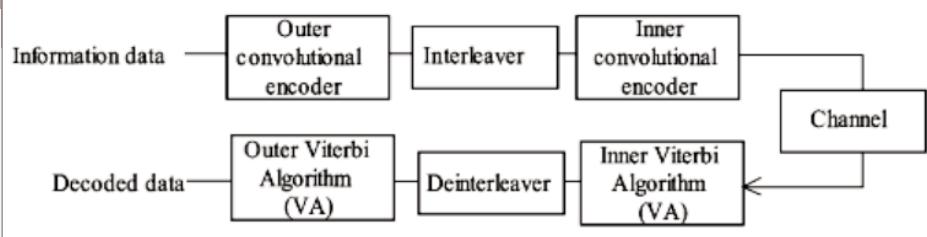

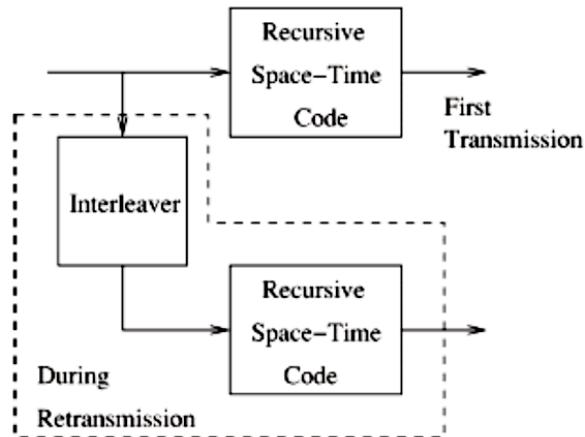

## 36 CHANNEL CODING, DECODING AND PROCESSING USED IN MOBILE SATELLITE COMMUNICATIONS – PART 3

In a series of three articles **Stojce Dimov Ilcev** reviews the basic and state-of-art channel coding, decoding and error correction techniques, as well as channel processing used in Mobile Satellite Communications

## 05 TREND

WHAT TO WATCH IN WIRELESS IN 2011!

## 06 TECHNOLOGY

## 10 FOCUS

SCALING INTRUSION PREVENTION SYSTEMS FOR 10G, 40G AND BEYOND

by **Dan-Joe Barry**

## 14 THE TROUBLE WITH RF...

GOING TO THE FAIR

by **Myk Dormer**

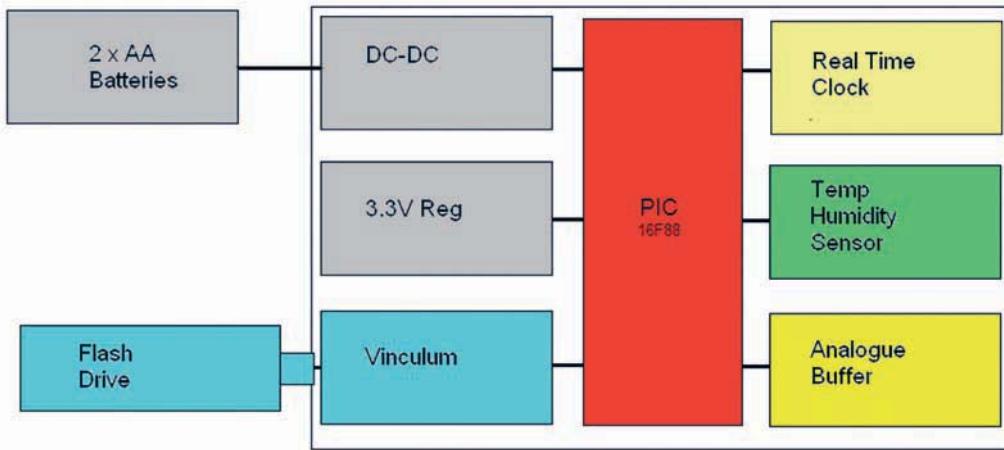

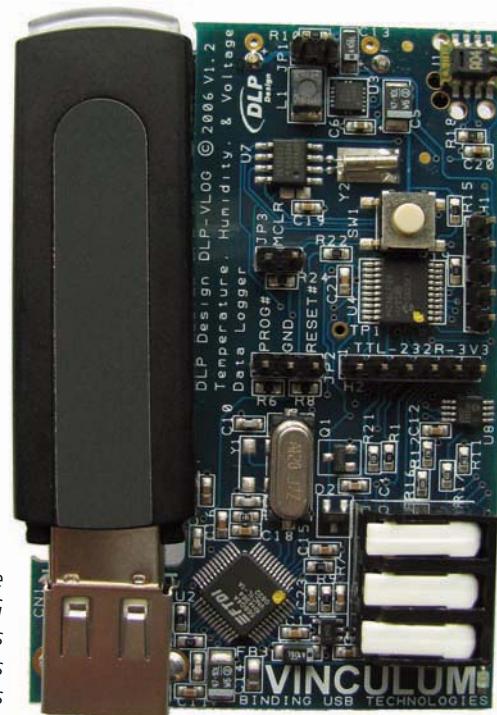

## 40 USB DESIGN PROJECTS

ADDING A USB FLASH DRIVE FOR DATA DISTRIBUTION

by **John Hyde**

## 42 LETTERS

## 43 TIPS AND TRICKS

## 45 EVENT

NATIONAL ELECTRONICS WEEK (NEW)

PRODUCTS REVIEW

## 46 PRODUCTS

## 50 LAST NOTE

Cover supplied by IDT

More about Clock Tree Considerations for Base-Station RF Cards on pages 8-9

*Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry – particularly as regards electric shock, fire hazards and explosions.*

Electronics World is published monthly by

**Saint John Patrick Publishers Ltd.**,

6 Laurence Pountney Hill, London, EC4R 0BL.

**QUASAR**

electronics

The Electronic Kit Specialists Since 1993

**Quasar Electronics Limited**

PO Box 6935, Bishops Stortford

CM23 4WP, United Kingdom

Tel: 01279 467799

Fax: 01279 267799

E-mail: sales@quasarelectronics.com

Web: www.quasarelectronics.com

**Postage & Packing Options** (Up to 0.5Kg gross weight): UK Standard 3-7 Day Delivery - £4.95; UK Mainland Next Day Delivery - £11.95; Europe (EU) - £11.95; Rest of World - £12.95 (up to 0.5Kg)

Order online for reduced price UK Postage!

We accept all major credit/debit cards. Make cheques/PO's payable to Quasar Electronics. Prices include 17.5% VAT.

Please visit our online shop now for details of over 500 kits, projects, modules and publications. Discounts for bulk quantities.

**01279**

**Credit Card

Sales**

**467799**

### **Motor Drivers/Controllers**

Here are just a few of our controller and driver modules for AC, DC, Unipolar/Bipolar stepper motors and servo motors. See website for full range and details.

#### **Computer Controlled / Standalone Unipolar Stepper Motor Driver**

Drives any 5-35Vdc 5, 6 or 8-lead unipolar stepper motor rated up to 6 Amps. Provides speed and direction control. Operates in stand-alone or PC-controlled mode for CNC use. Connect up to six 3179 driver boards to a single parallel port. Board supply: 9Vdc. PCB: 80x50mm. Kit Order Code: 3179KT - £15.95 Assembled Order Code: AS3179 - £22.95

#### **Computer Controlled Bi-Polar Stepper Motor Driver**

Drive any 5-50Vdc, 5 Amp bi-polar stepper motor using externally supplied 5V levels for STEP and DIRECTION control. Opto-isolated inputs make it ideal for CNC applications using a PC running suitable software. Board supply: 8-30Vdc. PCB: 75x85mm. Kit Order Code: 3158KT - £23.95 Assembled Order Code: AS3158 - £33.95

#### **Bi-Directional DC Motor Controller (v2)**

Controls the speed of most common DC motors (rated up to 32Vdc, 10A) in both the forward and reverse direction. The range of control is from fully OFF to fully ON in both directions. The direction and speed are controlled using a single potentiometer. Screw terminal block for connections. Kit Order Code: 3166v2KT - £22.95 Assembled Order Code: AS3166v2 - £32.95

#### **DC Motor Speed Controller (100V/7.5A)**

Control the speed of almost any common DC motor rated up to 100V/7.5A. Pulse width modulation output for maximum motor torque at all speeds. Supply: 5-15Vdc. Box supplied. Dimensions (mm): 60Wx100Lx60H. Kit Order Code: 3067KT - £18.95 Assembled Order Code: AS3067 - £26.95

Most items are available in kit form (KT suffix) or assembled and ready for use (AS prefix).

### **Controllers & Loggers**

Here are just a few of the controller and data acquisition and control units we have. See website for full details. Suitable PSU for all units: Order Code PSU445 £7.95

#### **8-Ch Serial Isolated I/O Relay Module**

Computer controlled 8-channel relay board. 5A mains rated relay outputs. 4 isolated digital inputs. Useful in a variety of control and sensing applications. Controlled via serial port for programming (using our new Windows interface, terminal emulator or batch files). Includes plastic case 130x100x30mm. Power Supply: 12Vdc/500mA. Kit Order Code: 3108KT - £69.95 Assembled Order Code: AS3108 - £84.95

#### **Computer Temperature Data Logger**

4-channel temperature logger for serial port. °C or °F. Continuously logs up to 4 separate sensors located 200m+ from board. Wide range of free software applications for storing/using data. PCB just 45x45mm. Powered by PC. Includes one DS1820 sensor. Kit Order Code: 3145KT - £19.95 Assembled Order Code: AS3145 - £26.95 Additional DS1820 Sensors - £3.95 each

#### **Rolling Code 4-Channel UHF Remote**

State-of-the-Art. High security. 4 channels. Momentary or latching relay output. Range up to 40m. Up to 15 Tx's can be learnt by one Rx (kit includes one Tx but more available separately). 4 indicator LED's. Rx: PCB 77x85mm, 12Vdc/6mA (standby). Two and Ten channel versions also available. Kit Order Code: 3180KT - £49.95 Assembled Order Code: AS3180 - £59.95

#### **DTMF Telephone Relay Switcher**

Call your phone number using a DTMF phone from anywhere in the world and remotely turn on/off any of the 4 relays as desired. User settable Security Password, Anti-Tamper, Rings to Answer, Auto Hang-up and Lockout. Includes plastic case. Not BT approved. 130x110x30mm. Power: 12Vdc. Kit Order Code: 3140KT - £74.95 Assembled Order Code: AS3140 - £89.95

#### **Infrared RC Relay Board**

Individually control 12 on-board relays with included infrared remote control unit. Toggle or momentary. 15m+ range. 112x122mm. Supply: 12Vdc/0.5A Kit Order Code: 3142KT - £59.95 Assembled Order Code: AS3142 - £69.95

#### **New! 4-Channel Serial Port Temperature Monitor & Controller Relay Board**

4 channel computer serial port temperature monitor and relay controller with four inputs for Dallas DS18S20 or DS18B20 digital thermometer sensors (£3.95 each). Four 5A rated relay channels provide output control. Relays are independent of sensor channels, allowing flexibility to setup the linkage in any way you choose. Commands for reading temperature and relay control sent via the RS232 interface using simple text strings. Control using a simple terminal / comms program (Windows HyperTerminal) or our free Windows application software. Kit Order Code: 3190KT - £69.95

### **PIC & ATMEL Programmers**

We have a wide range of low cost PIC and ATMEL Programmers. Complete range and documentation available from our web site.

#### **Programmer Accessories:**

40-pin Wide ZIF socket (ZIF40W) £14.95

18Vdc Power supply (PSU120) £19.95

Leads: Serial (LDC441) £3.95 / USB (LDC644) £2.95

#### **USB & Serial Port PIC Programmer**

USB/Serial connection. Header cable for ICSP. Free Windows XP software. Wide range of supported PICs - see website for complete listing. ZIF Socket/USB lead not included. Supply: 16-18Vdc. Kit Order Code: 3149EKT - £49.95 Assembled Order Code: AS3149E - £59.95

#### **USB 'All-Flash' PIC Programmer**

USB PIC programmer for all 'Flash' devices. No external power supply making it truly portable. Supplied with box and Windows Software. ZIF Socket and USB lead not included. Assembled Order Code: AS3128 - £49.95

See website for full range of PIC & ATMEL Programmers and development tools.

[www.quasarelectronics.com](http://www.quasarelectronics.com)

Secure Online Ordering Facilities • Full Product Listing, Descriptions & Photos • Kit Documentation & Software Downloads

# WHAT TO WATCH IN WIRELESS IN 2011! BY FILOME

BY FILOMENA BERARDI

# What will happen in 2011...

- NFC will finally come good. Aided by companies such as Samsung, Nokia, Google and Apple, over 40 million NFC-enabled handsets are projected to be sold in 2011. The long-deferred commercial volumes will finally be shipped.

- Over 85 million IEEE 802.15.4 ICs will be shipped. Driving factors include: the uptake of RF4CE in consumer electronics, displacing IR control; the growth of ZigBee in smart metering and factory automation; and the growing use of 802.15.4 ICs with proprietary software for a wide range of applications, ranging from commercial building automation to agricultural monitoring.

- 802.11 enters the peer-to-peer market in force. For the first time more than one million Wi-Fi-Direct devices are forecast to be sold. Bluetooth high-speed devices will also ramp up in 2H 2011, though many will only be 'Bluetooth high-speed ready' and will not be able to transfer data at true high speed.

- Smartphones will account for over 20% of mobile handsets sold worldwide. Consumer demand will lead handset manufacturers and operators to offer more entry-level smartphone models, using popular open operating systems such as Android. Shipments of this price tier (typically \$199 - \$299) will grow fastest, to pass 80 million.

- Machine-to-Machine (M2M) communications will grow quickly with nearly 43 million modules being shipped. Market drivers include the near-ubiquitous availability of cellular networks, government regulations, falling hardware prices and lower connectivity tariffs. Despite this, M2M modules will still account for only 3% of all cellular devices sold in 2011.

And what will take longer...

- ☐ Volume shipments of devices using Bluetooth low energy. This will happen only in 2012, when a million are forecast to be shipped, ramping up to over 100 million forecast for 2015.

- ☐ LTE accounting for much of the cellular installed base. Of course, long-term it will be huge, but look to 2014 before even 1% of the world's cellular installed base uses it. In the meantime, most carriers will seek to recoup their existing investments in the W-CDMA (UMTS) & HSPA networks to meet increased consumer demand for data.

Filomena Berardi is a Senior Analyst at IMS Research ([www.imsresearch.com](http://www.imsresearch.com))

AIDED BY COMPANIES SUCH AS SAMSUNG, NOKIA, GOOGLE AND APPLE, OVER 40 MILLION NFC-ENABLED HANDSETS ARE PROJECTED TO BE SOLD IN 2011

**EW will soon not be available through news trade, but don't miss out, order your copy directly from [www.electronicsworld.co.uk](http://www.electronicsworld.co.uk)**

**EDITOR: Svetlana Josifovska**

Email: svetlanaj@stjohnpatrick.com

**PRODUCTION MANAGER: Tania King**

Email: taniak@stjohnpatrick.com

**DISPLAY SALES: John Steward**

T: 1-416-207-0232, 207-1

Tel: +44 (0) 20 7933 8974

Email: [john@tichystrick.com](mailto:john@tichystrick.com)

**PUBLISHER:** Wayne Darroch

#### SUBSCRIPTIONS:

**SUBSCRIPTIONS:**

Saint John Patrick Publishers

PO Box 6009, Thatcham,

Berkshire, RG19 4QB

Tel: 01635 879361 Fax: 01635 868594

Email: [electronicsworld@circdata.com](mailto:electronicsworld@circdata.com)

**SUBSCRIPTION RATES:**

1 year: £16 (UK); £47.50 (worldwide)

## MISSING ISSUES:

Email: [electronicsworld@circdata.com](mailto:electronicsworld@circdata.com)

Email: [electronicsworld@circdata.com](mailto:electronicsworld@circdata.com)

**NEWSTRADE:**

Distributed by Seymour Distribution Ltd.

Distributed by Symco Distribution

2 East Poultry Avenue, London, EC1

Tel: +44 (0) 20 742

St

St John Patrick Publishers

# New research shows how light can control electrical properties of graphene

New research carried out by a team of scientists from the National Physical Laboratory (UK), Chalmers University of Technology (Sweden), University of

A light-sensitive graphene/polymer heterostructure

Copenhagen (Denmark), University of California Berkeley (US), Linköping University (Sweden) and Lancaster University (UK) has shown how light can be used to control the electrical properties of graphene, paving the way for graphene-based optoelectronic devices and highly sensitive sensors.

When graphene is combined with particular polymers, its electrical properties can be precisely controlled by light and exploited in a new generation of optoelectronic devices. The polymers keep memory of light and therefore the graphene device retains its modified properties until the memory is erased by heating.

Light-modified graphene chips have already been used at NPL in ultra-precision experiments to measure the quantum of the electrical resistance. In the future, similar polymers could be

used to effectively 'translate' information from their surroundings and influence how graphene behaves. This effect could be exploited to develop robust reliable sensors for smoke, poisonous gases, or any targeted molecule.

Graphene is a two-dimensional material made of a single atomic layer of carbon atoms. It is the thinnest material known to man and yet is one of the strongest ever tested. It does not have volume, only surface – its entire structure is exposed to its environment and responds to any molecule that touches it. This makes it in principle a very exciting material for super-sensors capable of detecting single molecules of toxic gases. Polymers can make graphene respond to specific molecules and ignore all others at the same time, which also protects it from contamination.

## INITIATIVE LAUNCHED TO ACCELERATE THE DEVELOPMENT OF EMERGING TECHNOLOGIES UTILISING GOLD

The World Gold Council announced that it is to play a pivotal role in the transition of new gold-based innovations from 'lab' to 'market'. There has been an explosion of interest in the use of gold in science and technology, mainly driven by the emergence of nanotechnology, yet breakthroughs in research are slow to achieve commercial success due to lack of further targeted investment and support.

The World Gold Council's initiative will help bridge the gap between government-funded early stage research and venture

capital-backed commercialisation through investing in gold-related technology in the fields of medical diagnosis and treatment, protecting the environment and renewable energy.

This announcement is accompanied by a new report, *Gold: The hidden element in innovation*, which details how the use of gold has led to the development of groundbreaking advances. As technology continues to progress, gold will be used in a multitude of new products and processes, and the World Gold Council expects these innovations will help address critical needs in medicine and the protection of the environment.

"The role of gold at the heart of many scientific advances is an untold story of innovation. Although little heralded, gold is the hidden element that has increased the efficiency, accuracy and effectiveness of many technologies," said Dr Richard Holliday, Director of Technology at the World Gold Council.

■ STMicroelectronics (ST) and Bluechip Limited are to cooperate in the manufacturing of unique MEMS-based tracking tags aimed at a range of different markets, including healthcare.

As the bluechip tracking tag is a mechanical device, it has the unique ability to both survive and read the ID of samples in extremely high and low temperatures, in addition to its immunity to gamma irradiation. This robustness provides significant advantages over more traditional identification or tracking solutions, such as labels, barcodes or RFID technologies, and provides the necessary high levels of data safety in the rapidly growing and labour-intensive healthcare markets, especially in biobanking.

■ The not-for-profit organisation NMI has announced it is to take the next developmental steps to enhance support for its members and encourage broader engagement with the electronic systems community. Building on its accomplishments for the semiconductor sector, the advance represents a natural evolution for the organisation as it seeks to create a more inclusive network across a wider spectrum. Speaking about the change, Derek Boyd, NMI's CEO said: "We're formally announcing our long term interest to bring closer interaction between chip and electronic systems companies and continue to reach out into key application areas of greatest interest to UK business and R&D operations."

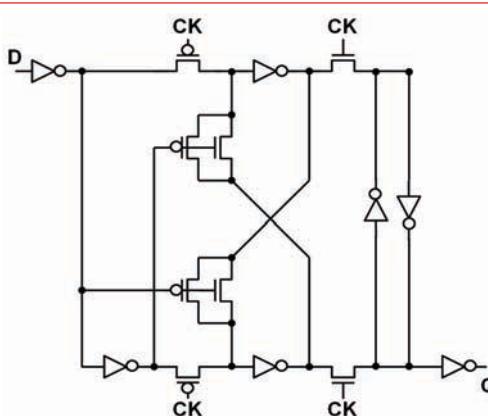

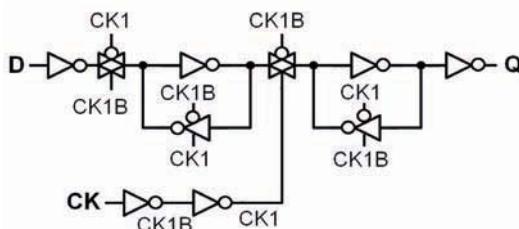

# Toshiba Develops New Energy-Saving Flip-Flop Circuit

Toshiba said that it has developed a new flip-flop circuit using 40nm CMOS process that will reduce power consumption in mobile devices. Measured data verifies that the power dissipation of the new flip-flop is up to 77% less than that of a typical conventional flip-flop and that it achieves a 24% reduction in total power consumption when applied to a wireless LAN chip.

A flip-flop is a circuit that temporarily stores one bit of data during arithmetic processing by a digital system-on-a-chip (SoC) incorporated in mobile devices and other digital equipment. As a typical SoC uses 100,000 to 10 million flip-flops they are an essential part of SoC designs.

A typical flip-flop incorporates a clock buffer to produce a clock inverted signal required for the circuit's operation. When triggered by a signal from the clock, the clock buffer consumes power, even when the data is unchanged. In order to reduce this power dissipation, a power-saving design technique called clock gating is widely used to cut delivery of the clock signal to unused blocks. However, after applying the clock gating, the flip-flop active rate, a measure of data change rate per clock, is only 5-15%, indicating that there is still plenty of room for further power reduction.

In order to save power, Toshiba changed the structure of the typical flip-flop and eliminated the power-consuming clock buffer. This approach brings with it the problem of data collision between the data writing circuitry and the state holding circuitry in the flip-flop, which Toshiba overcame by adding adaptive coupling circuitry to the flip-flop. With a specific combination of nMOS and pMOS transistors, this circuitry adaptively weakens state-retention coupling and prevents collisions. Despite the addition of the adaptive coupling circuitry, overall simplification of the basic flip-flop configuration reduces the transistor count from 24 to 22, and the cell area is less than that of the conventional flip-flop.

### **Conventional circuit configuration (above) vs circuit configuration of the new technique (below)**

## I wish my scope could give me logic and protocol views when I need them

To see a demo of an Agilent 9000 oscilloscope visit us at National Electronic Week, stand N331.

**Wish granted.**

The new Agilent Infiniium 9000 Series 600 MHz to 4 GHz oscilloscopes are engineered for broadest measurement capability.

You never know what your next project will require. That's why we designed the new Infiniium 9000 Series to be as versatile as you need to be.

**Three instruments in one.** Superior scope specs. Built-in logic and protocol analysis.

**Widest range of debug and compliance application software.** More than 25 apps, including RS232/UART, I<sup>2</sup>C/SPI, CAN, FlexRay, USB and USB2.0, PCIe 1.1 and DDR.

**Sized to fit your environment.** 15" XGA display, thin 12.9" H x 16.8" W x 9" D form factor.

See for yourself!

View our online demo at

[www.agilent.com/find/9000ad](http://www.agilent.com/find/9000ad)

UK 0118-927 6201 Ireland 1890-924 204

© Agilent Technologies, Inc. 200

Agilent Technologies

# Clock Tree Considerations for Base-Station RF Cards

Ian Dobson, Director of System Architecture, Integrated Device Technology

## INTRODUCTION

There are a number of issues that need to be addressed by a clock tree for a fourth-generation (4G) Long-Term Evolution (LTE) or WiMax wireless base station radio card. In addition to the constraints imposed by the Orthogonal Frequency-Division Multiplexing (OFDM) protocols themselves, there are critical aliasing and filtering concerns for ADCs, DACs and RF mixers. These challenges around the modulation elements provide the focus of this article.

## **SIMPLIFICATION OF NETWORK DEPLOYMENTS AND UPGRADES**

In order to support the simplification and economy of network deployments and upgrades, OEMs will look for radio card components that support software reconfiguration and can be re-used on multiple similar designs.

Because of the occasional need to support radio cards within a Remote Radio Head, most radio cards will be designed with a single input clock that may be recovered from the link to the base-station. These single input clocks may be poor in quality and significant jitter cleanup may be required in order to adequately generate other clocks on the radio card.

Thus, the core of a radio card clock tree must be a jitter attenuator with programmable output frequencies. The remainder of this article will discuss the performance attributes and why they are required, along with other clock tree requirements.

# RADIO CARD ARCHITECTURAL CONSIDERATIONS

Most radio card designs in base-stations today perform many of the manipulations required to build-up or tear-down the signal for a protocol like LTE or Multi-carrier GSM in the digital domain. It is much simpler to

**handle error-correction, channel-mapping and splitting the I & Q streams digitally.**

The complex data stream of this composite signal also requires very careful filtering / signal processing in both the transmit and receive directions. Doing this in the digital domain avoids the expense of things like precise component-value matching.

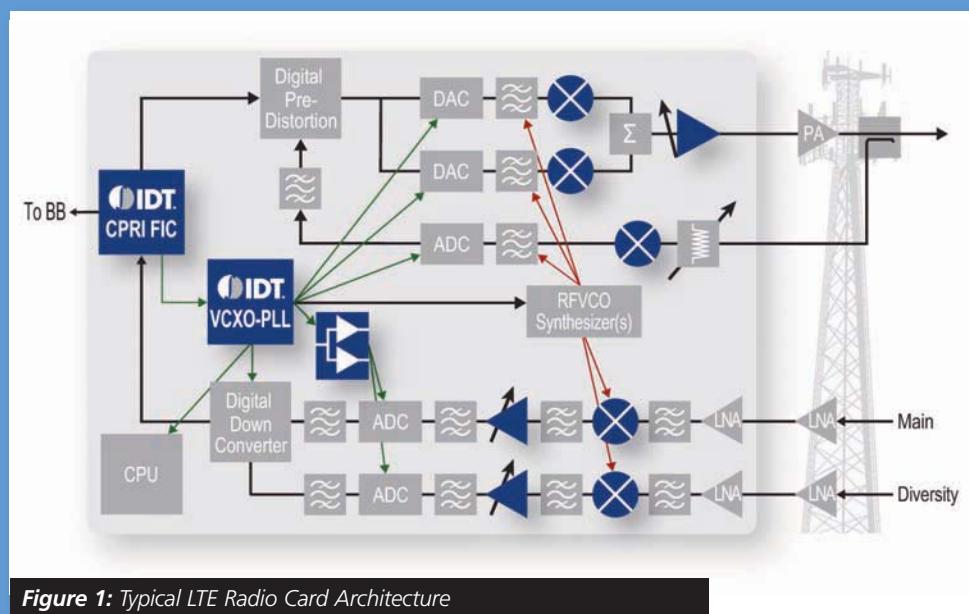

Despite the extensive digital manipulations, at some point, the signal must be modulated onto a carrier that can range from 824MHz – 2.62GHz and transmitted as an analog signal. Most base-station architectures that address multi-channel protocols including LTE, WiMax and multi-carrier GSM use a single stage analog conversion approach as shown in Fig 1.

On the transmit side, the individual sub-carriers are combined into a single stream digitally without being modulated first. This baseband signal is then converted to phase-offset analog I & Q streams by DACs and then up-converted to the transmission frequency via quadrature analog mixers. Variable and fixed gain amplifiers and a duplex filter are used along the path to boost the desired signal to the required strength in its transmission band while adding only a small amount of noise & distortion and simultaneously minimizing energy outside the transmission band to prevent interference with other RF channels.

On the receive side, the RF signal is usually amplified, filtered, and then converted via a mixer to a much lower intermediate frequency (IF) in the 75MHz – 250MHz range where it is further amplified by a variable amount, filtered and finally sampled by a pipeline ADC in accordance with the Nyquist criterion. Down conversion and demodulation of the sub-carriers are then handled in the digital domain. The goal with the receiver is to accomplish this signal conditioning prior to the ADC with a minimum of added noise and intermodulation distortion while avoiding exceeding ADC full scale.

Radio card architects prefer that the clock tree be as integrated as possible. Not only for the reasons described, but because each clock tree component comes with its own jitter contribution that can push the clock signal out of spec. With this integration comes the need to generate not just the RF & IF clocks for modulation, but the sampling clocks for the ADCs & DACs and the clocks for the other digital components such as CPUs, ASICs and FPGAs.

The clocks for these digital components usually have quite lax specifications in comparison to the clocks involved in the RF signal path; period jitter is most often the primary concern. When generating these clocks on the same chip as the more sensitive clocks, there are two issues. First of all, the digital clocks are rarely integer multiples of the incoming clock signal to the radio card and so must be generated with fractional feedback or fractional output divider

**Figure 1:** Typical LTE Radio Card Architecture

techniques. Both these techniques however, introduce significant spur content within the clock chip and onto the clock outputs. Secondly, digital-chip clocks (or any spurs produced while generating them) that fall near the RF, IF or sampling frequencies can't be filtered out easily and so must be avoided. Even frequency components outside those regions of interest may degrade the SNR either as wideband noise or, if they are not filtered, by aliasing into the critical frequency ranges.

### FREQUENCY EFFECTS OF MIXERS, ADCS AND DACS

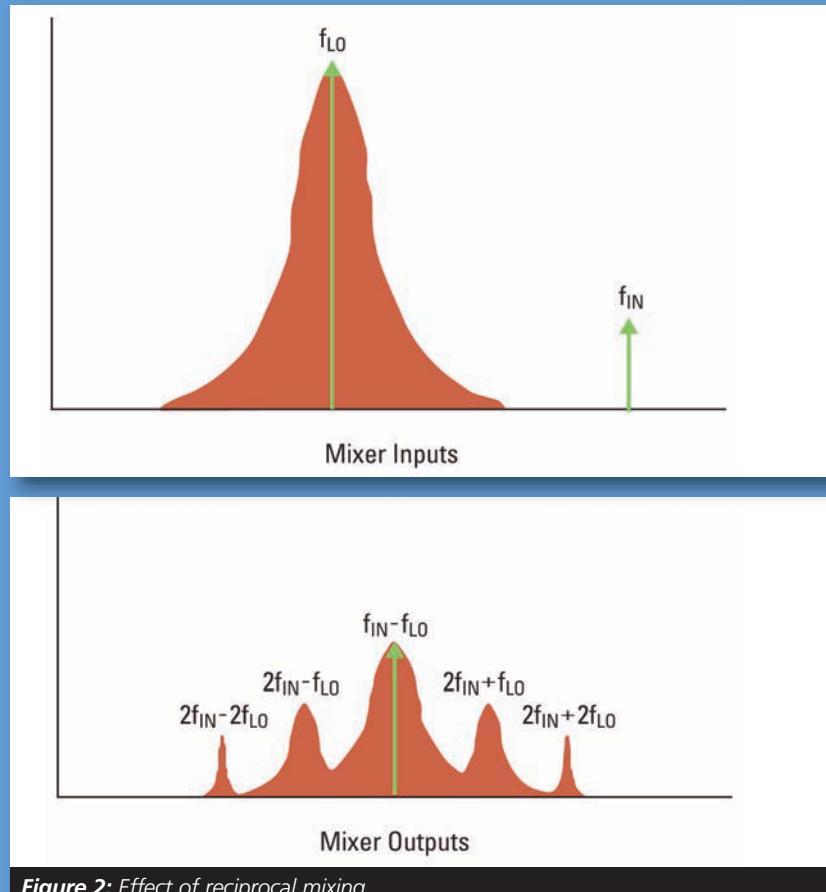

Mixers are the analog components used to convert a higher frequency signal to a lower frequency signal or vice-versa. In most base-station radio card designs they currently convert the signal from RF->IF or from Baseband->RF. The main issue of concern with respect to a clock tree design is the issue of frequency aliasing. When multiple frequencies pass through a non-linear device, those frequencies will interact with each other. These interactions are called inter-modulation products.

The function of a mixer is to take two input frequencies and produce an output frequency that is either the sum (up-conversion) or difference (down-conversion) of the two frequencies.

Present-day radio cards are designed to recover signals that are multi-carrier in nature. So, rather than a single tone line of desired signal, the ideal signal consists of a whole series of tone lines evenly spaced throughout the frequency band of interest. These lines represent the individual channels being recovered. Unfortunately as this multi-carrier signal proceeds through a non-linear element like a mixer, each of those channels will inter-modulate each other. The regular spacing of the channels will cause the odd order products to fall almost exactly on top of the channels being recovered. Filters placed before a mixer will be used to attenuate noise that will contribute to even-order products. Filters after the mixer will remove inter-modulation products that fall outside the frequency band of interest, however little can be done about the in-band odd-order products because they fall too close to the wanted signals.

While a band pass filter after the mixer can remove the undesired clean tone lines fairly well, any jitter on the sampling clock will turn those clean tone lines into a skirt as shown in Fig 2. The tails of the skirts from every undesired product will have some contribution within the pass band of the filter; this is referred to as wideband noise. Any clocks generated for the mixers (or ADCs or DACs) must have a very low noise floor in order to minimize their wideband noise contribution.

Unwanted signals called 'interferers' or 'blockers' that get into the mixer's input will have an effect on the specifications of clock signals. They can include other signals received by the antenna or signals internal to the system that get coupled into the receive signal path. While blockers that are widely separated in frequency from the desired signal can be significantly attenuated by the pre-filter, ones close to the desired signal's frequency will pass through. Furthermore, in a protocol like LTE where the wanted signal has a low average power, even a blocker attenuated by the filter may still contain enough energy to compete with the desired signal.

Figure 2: Effect of reciprocal mixing

This effect is why the phase noise skirt of the clocks into the mixers must be kept as 'narrow' as possible. The spread of the reciprocally mixed phase noise on the blockers must be kept to a minimum. One of the main challenges in the radio card design is the selection of frequencies on the card with an eye to maximizing the separation of blockers and their inter-modulation products from the frequencies of the wanted signals.

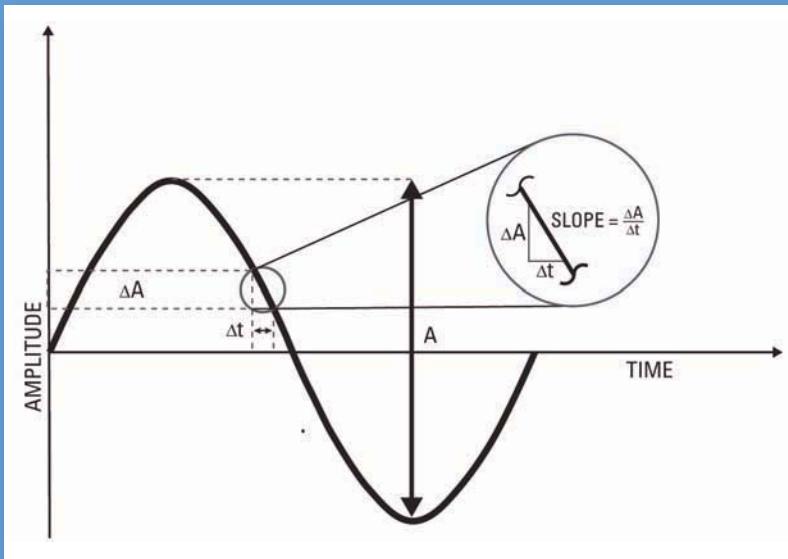

### ADDITIONAL EFFECTS OF JITTER ON ADCS

Because ADCs are sampled data systems and are not perfectly linear in their translations, they too will suffer all the same effects of inter-modulation products between desired input signals, unwanted (blocker) signals and the sampling clock.

However, there is another effect driving the specifications of the sampling clock for the ADC. This is the aperture jitter effect illustrated in Fig 3.

The basic concept is that any uncertainty in the time that a sample is taken can be translated by trigonometry into an uncertainty in the amplitude for that sample. Uncertainty in amplitude results in degradation in the SNR of the ADC. Once the frequency of the input signal is known, a RMS jitter target can be determined for the desired SNR of the ADC. Once that target is arrived at then the intrinsic jitter of the clock tree within the ADC can be factored-out to determine the target RMS jitter spec for the sampling clock.

### EFFECTS OF CLOCK JITTER ON DACS

Digital-Analog Converters (DACs) are used in the transmit path to turn a digital representation of the baseband signal into an analog one for

Figure 3: Aperture jitter in an ADC

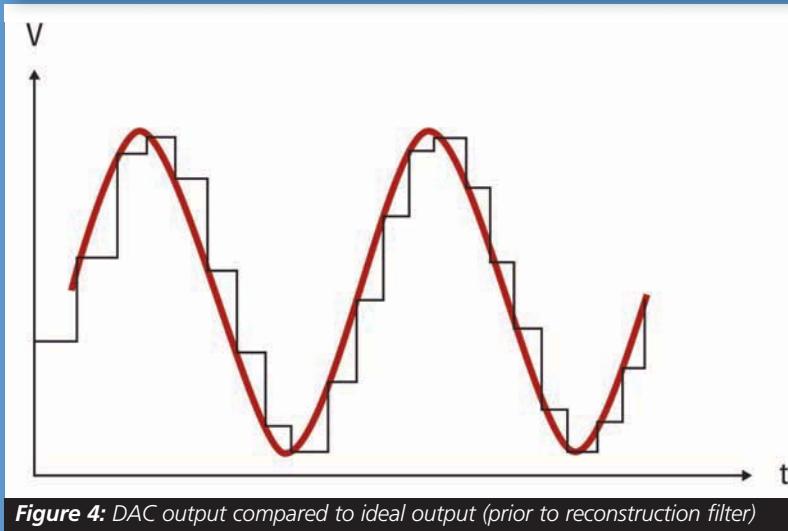

Figure 4: DAC output compared to ideal output (prior to reconstruction filter)

subsequent conversion to the RF frequency and amplification to the desired transmit power. The radio card designer will take care in fixing the card's frequency plan to ensure that the sampling frequency of the DAC does not overlap critical frequency bands on the receive side of the card. This is important because DACs suffer from the generation of image frequencies from two potential mechanisms.

The first mechanism is identical to what happens in ADCs and mixers, the convolution of the sampling clock ( $f_{LO}$ ) and the input signal ( $f_{IN}$ ) to produce frequencies at  $N \cdot f_{LO} + M \cdot f_{IN}$ . This convolution results from non-linearities in the converter. The effects on the requirements for the sampling clock jitter are similar to the ADC.

The second mechanism is an unavoidable result of the way most DACs operate. As shown in Fig 4, at every edge of the sampling clock the DAC's output will switch very quickly to a new voltage level as represented by the digital sample value. This value will be held until the next sampling clock edge. The output only matches the desired waveform once per sample clock.

This results in error energy being introduced. Additionally, most DACs will suffer from some level of clock feed-through, resulting in further spikes at  $N \cdot f_{LO}$ . For this reason, the sampling clock frequency will often be considerably higher than required by Nyquist so that the

feed-through spikes are well beyond the frequency of interest and so can be easily filtered.

The DAC output waveform will be passed through an analog reconstruction filter to remove as many of these unwanted frequencies as possible. Design of the filter will be easier and implementation will be less costly if the clock jitter and phase noise skirt are well controlled.

In addition to requirements for specific phase noise levels at specific offsets on the sampling clock, there will also be a specification for RMS jitter integrated over a range of frequencies. This is due to clock jitter causing distortion on the output waveform from the ideal. This will degrade the Total Harmonic Distortion (THD) or Signal-to-Noise-plus-Distortion (SINAD) of the DAC and must be kept within specification to prevent degradation of the radio card's Error Vector Magnitude (EVM). On the transmit side, lower clock jitter can either directly contribute to better EVM or be used to relax the design constraints for Crest Factor / Peak-Average Power Ratio reduction circuitry.

## REQUIREMENTS FOR PHASE ALIGNMENT WITHIN A RADIO CARD

In addition to basic voice and data transmission services, many mobile users are demanding additional services. One example is precise location of the user via triangulation from a set of cell towers. Precise determination of location by radio triangulation is best achieved when all the antennas are transmitting and receiving signals in close phase alignment with each other. Some such services such as requiring separate base-stations to operate with less than 50 nsec of phase discrepancy between them. A radio card will be given a budget of how much phase discrepancy it may introduce relative to other radio cards in the same system. This is another reason why each radio card generates all its frequencies internally from a single clock input signal. It ensures that there is at least a common starting point for phase alignment for all the clocks on the card.

## SUMMARY

RF cards need to generate a variety of clocks from a single, often noisy, input clock. Several of these output clocks will not have an integer relationship to the input clock. All clocks must pay attention to their total noise contribution in order to prevent noise coupling into critical circuitry. Clocks specifically for mixing functions including ADCs and DACs will have tight specs on their RMS jitter as well as on their 'noise skirt' to avoid generating blocker signals in the RF signal paths. The frequencies for these clocks will be carefully planned for the specific implementation details of the card and so are usually unique to each design. Also, a variety of phase delay adjustments must be possible for many of those same clocks. The result of this is a need for a very high-performance clock tree whose specs are essentially custom for each card, ideally implemented in a single component. Devices such as IDT's Netcom timing devices are uniquely positioned to provide those very high-performance devices tailored to the individual RF card design requirements.

# Scaling Intrusion Prevention Systems for 10G, 40G and Beyond

Dan-Joe Barry, Napatech's vice president of marketing, takes a look at the distinctive features of Intrusion Prevention Systems (IPS) and how the performance of these systems can be increased to keep up with the relentless development on the bandwidth front

**THE INTERNET IS** still growing, as we make the transition from Intrusion Detection Systems (IDS) to Intrusion Prevention Systems (IPS) – driven in part by the fact that IPS technology can scale to meet users' needs in the future.

Against this backdrop, we take a look at the distinctive features of IPS and how the performance of these systems can be increased to keep up with the relentless development on the bandwidth front.

Whilst many IT security professionals regard IPS to be a natural extension of IDS technology, the real answer is that IPS is actually another type of access control mechanism, rather than purely a sister IT security platform to IDS.

It may surprise you to know that the term IPS is actually a lot younger than IDS, and is a colloquial term first used by Andrew Plato, a technical consultant with a major IT security vendor that, way back in the late 1990s, developed the industry's first IDS platform.

In its purest form, an IPS makes a number of access control decisions based on the content of the application, rather than taking a traditional firewall approach of monitoring IP addresses, ports and other connective links.

Back in 1998, Andrew Plato opined that a good IPS should feature a sophisticated analytical engine, but one that generates as few false positives as possible. Provided this is the case, he said at the time, then a good IPS has a number of advantages over IDS, since it can sit in line with an IP traffic flow and analyse the data stream in real time.

In addition, most modern IPS solutions also have the ability to analyse Layer 7 protocols such as FTP, HTTP and SMTP, and make decisions on whether to allow – or quarantine – the IP packets as required, even if the data is encrypted.

But are today's IPS platforms up to the task of scanning IP traffic at the high speeds needed in a modern IT environment?

The problem facing IT professionals is that, with the Internet growing at between 40 and 60% a year (source: Atlas Internet

Observatory) – and against the backdrop of a mobile data explosion – it's important that IPS technology can keep up with this data bandwidth growth and not become the bottleneck in the network.

It's also becoming clear that, on a typical network of today, users are placing a very load on each port of a multi-10G port system and, whilst there are IPS products available that are capable of supporting a multiple 10Gbps port topology, providing continuous 10Gbps throughput on these ports is a something of a challenge.

The most worrying part of this development is how IPS platforms can be scaled to meet the needs of 40G and 100G IPS technologies, which are set to be introduced to the IT/networking mix in the next few years.

Until a few years ago, it could be argued that IPS platforms were up to the task, especially since most IPS platforms adopted a

address validation, typically by applying a number of automated checks to verify whether the message comes from a source previously known to be dangerous.

The fourth stage involves applying an anti-malware and anti-hacking analysis engine for anything suspicious that has passed the first three analysis stages but does not pass muster.

The fifth stage, typically involves using the analysis engine to weed out anything that still looks suspicious for later, manual, analysis by the IT security staff concerned.

However, the increasing sophistication of malware, together with the recursive and obfuscated coding approach taken by an increasingly criminal hacking fraternity – and, of course, the higher network speeds seen on today's networking systems – means that IPS systems are under pressure to keep up, both in terms of handling the amount of data, but

## "THE MAJORITY OF [IT HACKING] ATTACKS TODAY ARE CARRIED OUT BY HIGHLY SOPHISTICATED CRIMINAL ORGANISATIONS ATTEMPTING TO STEAL DATA OR HIJACK COMPUTING RESOURCES FOR THEIR OWN ILLEGAL USE"

core five-stage real-time analysis process that steps through a number of stages as various IT threats are encountered when monitoring an organisation's data streams that flow both in and out of the IT resource.

The first stage is to bandwidth throttle any suspicious IP traffic to give the organisation's IT security software a chance to analyse the data stream – let's take the example of an email message stream – and deal with suspect messages and/or attachments in real time.

If the data is found to be suspect, but does not conform to known infection signatures, then the second stage is for the message's header to be analysed and, if an infection etc., is found, the data can be quarantined.

The third stage in the analysis process involves performing user management and

also in having the raw horsepower to run more sophisticated algorithms.

### How Serious is the Threat of an Intrusion?

A recent online poll carried out by Napatech found that a quarter of respondent firms have suffered a network intrusion.

The interactive poll amongst more than 300 attendees at one of our online events, found that 25% of respondents had experienced an intrusion incident, with 44% of these incidents occurring within the last 12 months.

The important thing to realise here is that network intrusion events are not just an irritation – as they were back in the early days of IT networking – but they can be commercially damaging. This is because,

A typical error page

unlike the altruistic 1980s – when the ‘hackers’ of yore tended to be fellow engineers who also had access to the dial-up modems, expertise and other IT resources that were required to gain access to other businesses’ online assets – the majority of attacks today are carried out by highly sophisticated criminal organisations attempting to steal data or hijack computing resources for their own illegal use.

These Napatech online poll results were confirmed by a PricewaterhouseCooper-sponsored survey, details of which were announced at the recent Infosecurity Europe show in London. That survey showed that 83% of smaller organisations had experienced a security incident in the last year, compared with 45% two years earlier.

The PwC/Infosecurity survey also revealed that 90% of all organisations had increased their expenditure on IT security technology, whilst smaller businesses are now spending 10% of their IT budget on security issues, compared to 7% two years ago.

The report attributes the rise partly on the increasing use of cloud computing and social networks within enterprises. Delving into the study reveals that 15% of large companies noted IPS systems are under pressure to keep up, both in terms of handling the amount of data, but also in having the raw horsepower to run more sophisticated algorithms that their IT resources had been accessed by an unauthorised outsider in the last 12 months, and 25% had suffered a denial-of-service attack – double the number logged in the last survey carried out two years earlier.

The report also found that the rate of adoption of newer technologies has accelerated over the last two years, with most respondents now using wireless networking, remote access and VoIP technologies. In addition, the number of organisations allowing staff to have remote access to their systems has also increased with around 90% of large companies now offering this facility.

These figures confirm that our Napatech online poll is on track and that the number of intrusion incidents is definitely on the rise. This, in turn, is also forcing most organisations to increase the proportion of their IT budget they spend on security technologies.

#### Raising the Security Game

Businesses are not just increasing their IT security budgets, however, they are also raising their game when it comes to security strategies. Given this scenario, the key challenge now is scaling these systems to keep up with the increasing bandwidth generated by richer content in emails and on Web sites, more video and teleconferencing and the transition to cloud computing already taking place.

The important thing to realise is that all these innovative services provide a new and high-speed avenue of attack for hackers. And because of this, network security systems need to react in real-time to contain the problem.

To keep up with these high-speed, real-time demands, the traditional approach of network security appliance vendors has been to invest in the development of customized, proprietary

EW will soon not be available through news trade, but don't miss out, order your copy directly from [www.electronicsworld.co.uk](http://www.electronicsworld.co.uk)

hardware. But, a new approach is emerging where off-the-shelf standard PC server hardware is being used negating the need for hardware development.

The Napatech poll revealed that the majority of network security appliances being used are still based on proprietary hardware, but for every three proprietary systems, there are now two systems based on standard PC server hardware.

In the past, PC servers have not been powerful enough to meet the demands of security applications like IPS, but the latest generation of PC servers provide significant processing power and a strong roadmap of increased performance to come.

Our researchers have discovered it has now become more economical to build network security appliances based on standard PC server hardware using Napatech’s intelligent real-time network analysis adapters to ensure high levels of performance. But, one of the most compelling reasons for considering this approach is the ability to scale performance.

At various key IT events throughout this year, Napatech has demonstrated a full-throughput 10Gbps IPS system based on eight instances of a standard SNORT application running in parallel.

This technique takes advantage of the multiple CPU cores available in modern PC servers. Napatech can support up to 32 CPU cores, so as the number of cores increases and the power of each core ramps up, the ability to scale performance increases.

Indeed, it’s worth noting that CPU chipmakers such as Intel and AMD are increasing the performance of their chips by as much as 50% on an annual basis. Can the vendors of proprietary network security appliances keep up with this kind of performance roadmap? Does it even make sense to try? If you ask us here at Napatech, we will tell you that the time has come to reconsider. ■

A recording of the online Napatech webinar referenced in this article can be found online at: <http://bit.ly/9CmM6M> (registration required)

**HP8563E SPECTRUM ANALYSER**

9KHZ - 26.5GHZ Synthesised..... £POA

**HP33120A FUNCTION GENERATOR**

100 MicroHZ - 15MHz

Unused Boxed £595

Used, No Moulding, No Handle £395

**MARCONI 2955 RADIO

COMMUNICATION TEST SET**

ONLY £625

Also available Marconi 2955A & 2955B

**ENI 3200L RF POWER AMPLIFIER**

250KHZ-150MHZ 200W 55Db

**AGILENT E4402B** Spectrum Analyser

100HZ - 3GHZ with Option 1DN Tracking

Gen; 1 DR Narrow Res; A4H GPIB,

UKB.....£5800

**HP 35670A** FFT Dynamic Signal Analyser

2 Channel. Unused in original box...£4000

**AGILENT 83752B** Synthesised Sweeper

0.01-20GHZ.....£6000

**HP83711B** Synthesised 1-20GHZ with

Opt IEI Attenuator.....£5000

**AGILENT/HP E4431B** Signal Generator

250KHZ-2GHZ Digital Modulation...£2750

**MARCONI 2024** Signal Generator 9KHZ-

2.4GHZ Opt 04.....£1250

**MARCONI/IFR 2030** Signal Generator

10KHZ-1.35 GHZ .....£995

**MARCONI 2022E** Synthesised AM/FM

Signal Generator 10KHZ-1.01GHZ ...£5000

**HP8566A** Spectrum Analyser 100HZ-

22GHZ.....£1950

**HP8568A** Spectrum Analyser 100HZ-

1500MHZ.....£1250

**AVCOM PSA-37D** Spectrum Analyser

1MHZ-4.2GHZ.....£-

**IFR 1200S** Service Communication

Monitor.....£1500

**HP6624A** Power Supply 0-20V 0-2A

Twice, 0-7V 0-5A; 0-50V 0.8A

Special price.....350

**AVO/MEGGAR FT6/12** AC/DC

breakdown tester.....£-

**MARCONI/IFR/AEROFLEX 2025** Signal

Gen 9KHZ-2.51GHZ Opt 04 High Stab

Opt 11 High Power etc As New....£2500

**SOLARTRON 1250** Frequency Response

Analyser 10uHZ-65KHZ.....£995

**HP3324A** Synthesised Function

Generator 21MHZ.....£500

**HP41800A** Active Probe 5HZ-500MHZ

.....£750

**ANRITSU MS2601A** Spectrum Analyser

10KHZ-2.2GHZ 50ohm.....£750

**AGILENT E4421B** 250KHZ-3GHZ

Signal Generator £2500

**HP53131A** Universal Counter Opt 001

Unused Boxed 3GHZ.....£850

Unused Boxed 225MHZ.....£595

Used 225MHZ.....£495

**HP8569B** Spectrum Analyser 0.01-

22GHZ.....£1000

**HP54616C** Oscilloscope Dual Trace

500MHZ 2GS/S Colour.....£1250

**QUART LOCK 10A R** Rubidium

Frequency Standard.....£1000

**PENDULUM CNT90** Timer/Counter

/Analyser 20GHZ.....£1950

**ADVANTEST R3465** Spectrum

Analyser 9KHZ-8GHZ.....£-

**HP Programmable Attenuators** £300

each

**3320H DC-18GHZ** 11db

**3321G DC-18GHZ** 70db

Many others available

**AGILENT E3610A** Power Supply 0-8V

0-3A/0-15v 0-2A Unused

**AGILENT E3611A** Power Supply 0-20V

0-1.5A/0-35V 0-0.8V Unused

**CIRRUS CRL254** Sound Level Meter

with Calibrator.....£95

**CEL328** Digital Sound Level Meter with

CEL284/2 Acoustical Calibrator.....

**CEL 269** Digital Sound Level Meter with

CEL282 Acoustical Calibrator

**FLUKE SCOPEMETERS**

**99B** Series II 2Ch 100MHZ 5GS/G from

£325

**97** 2Ch 50MHZ 25MS/S from £225

**MARCONI 2945 RADIO

COMMUNICATION TEST

SET with....**

Opt 01 - 600 ohm Matching Unit

Opt 03 - High Stability OCXO

Opt 06 - Memory Card Drive with Real

Time Clock Opt 08 - SSB Demodulator

Opt 21 Demodulation Filters

Opt 22 POCSAG Decode

Only £3,000

**HP 8569B**

Spectrum Analyser 0.01-22GHZ

£995

**HP6269B** Power Supply

0-40V 0-50A £400

**AMPLIFIER RESEARCH

POWER AMPLIFIER 1000LAM8** £POA

**Designed in the UK,

Made in the UK.**

Tel. 01298 70012

[www.peakelec.co.uk](http://www.peakelec.co.uk)

[sales@peakelec.co.uk](mailto:sales@peakelec.co.uk)

West Road House

West Road

Buxton

Derbyshire

SK17 6HF

**PEAK**®

electronic design ltd

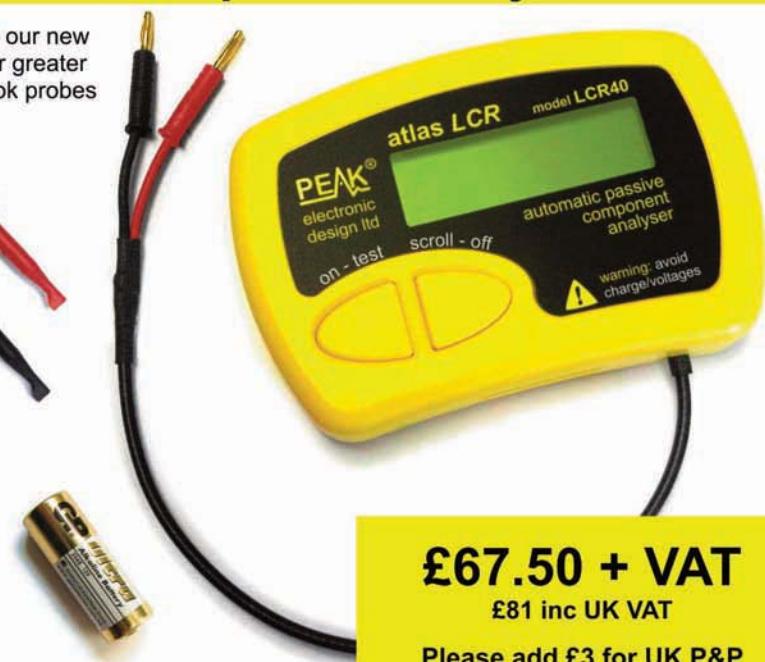

## Atlas LCR - Passive Component Analyser

The Atlas LCR (Model LCR40) is now supplied with our new premium quality 2mm plugs and sockets to allow for greater testing flexibility. Supplied with 2mm compatible hook probes as standard, others available as an option.

Test inductors (from 1uH to 10H), capacitors (1pF-10,000uF) and resistors (1Ω to 2MΩ). Auto-range and auto component selection.

Basic accuracy of 1.5%. Battery and user guide included.

Optional Probes

**£67.50 + VAT**

£81 inc UK VAT

Please add £3 for UK P&P

# Going to the Fair

Myk Dormer

**INDUSTRY SHOWS**, from the small regional or niche market events to the biggest international spectacles, have been a part of engineering life for decades – arguably since the great national exhibitions of the nineteenth century.

Most engineers have attended at least one such event as a visitor, wandering about for days from one interesting display to the next, but exhibiting at an industry show, organizing and manning a company stand is considerably more involved than just a "day at the fair".

The bare mechanics of running a booth are pretty obvious: hire the floor space and the furniture, arrange staff accommodation and travel arrangements, print promotional literature, turn up and watch the orders come rolling in. Easy?

In principle, yes, but in practice things are never quite so straightforward. While I cannot claim to be a world-class expert – some big companies employ staff who do nothing but organize events – I have attended and organised enough company booths to know what some of the pitfalls are:

**1. Investment.** It is vital to assign sufficient resources. A company presence at an event is a living advertisement. It provides a potential customer's first impressions, which can permanently colour their opinion of your organisation. So make sure it looks good.

Plan ahead: be prepared to spend some money to get a big enough space, with the right furnishings. Make sure that documentation is professionally printed, that display models are well presented and that demonstrations are tried, tested and working beforehand. Assign sufficient staff to the event, so that rest-breaks can be had and the set-up and break-down tasks don't fall to one or two overworked people.

**2. Purpose.** Remember why you are there. Staff on a booth must be motivated, happy and focused, with a good spread of technical, commercial and interpersonal

skills. It is definitely a place for 'volunteers only'. Understand that 'running the stand' is real full-time work and never attempt to combine a show with staff meetings or customer conferences. Such things can precede or follow an event, but they should never compete with it for time; your customers are at the event to see more than just you.

There is no room to do other jobs, like answering emails or telephone queries, and no point assigning someone to an exhibition who really doesn't want to be there: it will show through their face and leave a bad image. A group of disinterested salesmen, standing with their backs to the customers, muttering about the cricket scores, or fiddling with a laptop, makes a bad impression that no amount of subsequent work will erase.

**3. Clutter.** No matter how many square meters have been rented, a stand is still a relatively small space. There is no place for any extraneous items: coats, personal luggage and packaging materials need to be stored elsewhere, litter must be rigorously collected and the displays and demonstrations must be kept in good order.

There is never room for personal laptops and no-one should be eating their (greasy, crumb-making) meals on-stand. A half eaten kebab is never a good advert. There must be sufficient manpower that meal breaks and rest breaks can be properly allowed for without leaving an empty booth, while staff not 'on duty' need to find somewhere else to gather and chat.

**4. Focus!** Remember why the company is attending the event: to make contacts and to be seen. There needs to be plenty of promotional literature to hand out, ranging from lightweight flyers and cards to dense catalogues and datasheets; displays need to be clear, interesting and eye-catching; and the company name and website need to be written on everything – even free-gift pens.

Staff on the stand need to be able to gather contact details easily (business card scanners are impressive, but an abundant supply of notepads can often do as well) and there needs to be a post-event debriefing/follow-up process planned in ahead of time. No potentially valuable customers can be allowed to "go missing".

**5. Clarity.** Everyone in a company will or should have a good idea of what the products or services it offers actually are and what they are for. The same cannot be said for a potential new customer, so the displays and demonstration models need to be informative, accessible and simple. It is possible to get "too clever" with advertising imagery and it is all too easy to vanish behind a smokescreen of industry- niche specific jargon.

A company selling bolts probably needs some big pictures of bolts, not a stylized image of a wolf surrounded by lightning, or a display of flashing purple lights. Use simple language and avoid management or technical jargon. That can come later, when the customer is reading the datasheets.

**6. Fun.** The preceding comments make an industry show sound like a military boot-camp crossed with a submarine-cruise. It isn't. If properly organised it is a chance to make contact with customers and suppliers in a dynamic, positive environment. The 'feel' of a big show is unique and intoxicating, while the co-operation and hard work necessary to make a show "work" is better than any trendy "team building exercise".

Furthermore, many of the events are in fascinating parts of the world, which you might otherwise never think to visit. An industry show is a valuable experience and, like many things in life, will yield rewards proportionate to the effort you put in.

Enjoy it! ■

Myk Dormer is Senior RF Design Engineer at Radiometrix Ltd [www.radiometrix.com](http://www.radiometrix.com)

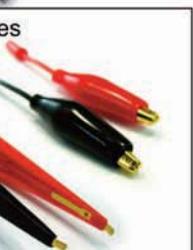

# Driving LED Lighting Adoption

**Author: Alistair Winning, Farnell**

LED-based lamps consume around a quarter of the power of a conventional incandescent bulb for comparable light output, and are gaining acceptance from homeowners and businesses seeking to cut their energy bills as well as their carbon footprint. LEDs can also last up to 50,000 hours or beyond, depending on operating temperature, thereby delivering longer-term advantages such as lower replacement costs and reduced waste.

Multi-LED replacement bulbs in standard form factors such as MR16 provide immediate and cost-effective access to the new technology. In addition the small dimensions and relatively low operating voltages of power LEDs, which are available in several shades of white light as well as standard colours and colour-mix versions, allow lighting designers to create new styles and develop ever-more versatile and controllable applications.

## BACKWARDS COMPATIBILITY

The lighting industry knows that LED lamps must be easily implemented as direct replacements for conventional types to ensure rapid uptake, particularly by consumer markets. As end users and installers demand replacements that will interoperate with existing installed equipment; in particular, with triac-based phase-cut dimmers. These are already installed in many houses and commercial premises, for use with incandescent lamps, to save energy and improve end-user comfort.

The triac-based dimmer is designed for operation with a resistive load such as incandescent or halogen bulbs. Dimming is achieved by delaying the firing angle of the triac using an RC circuit, hence reducing the average power delivered to the load. An LC filter is used to reduce conducted EMI resulting from the sharp voltage rise at triac turn-on. The lamp's resistive load provides damping for this filter and also helps maintain a holding current to ensure the triac remains conductive, even at light loads.

The phase-cut waveform is not a suitable dimming signal for a conventional LED driver. Effects such as the sudden voltage rise and the reduced average voltage over the complete cycle can result in flickering of the LED lamp. The effective dimming range is also restricted.

A number of LED drivers capable of operating with conventional wall dimmers have emerged to overcome this challenge. Among these, the National Semiconductor LM3445 has internal angle-detect and dim-decoder circuits, which help translate the incoming phase-cut waveform into a constant-current signal to drive the LEDs at the desired brightness. The device also implements a bleeder circuit, which operates in conjunction with an external resistor, to ensure proper triac operation by emulating the ability of an incandescent load to maintain the triac holding current. A passive PFC circuit maintains a high power factor and minimises harmonic distortion by drawing current directly from the line for most of the cycle. This allows drivers built with the LM3445 to meet IEC 61000-3-2.

Other triac-dimmable devices such as the NXP SSL210X are also available, which integrate comparable functions to ensure correct operation of the triac while also improving power factor, distortion performance and efficiency.

## THERMAL MANAGEMENT

The light output from a power LED is known to decrease with increasing temperature and, since the power LED is a semiconductor device, its reliability is directly related to operating temperature. The component can also be destroyed by excessive internally generated temperatures. In practice, the lower the temperature, the more reliable and long-lasting the LED will be.

Over its lifetime, the light produced by a power LED shows a gradually diminishing trend. The device's end of life can be defined as the point at which the light output falls below a usable level, according to the application. This reduction in light output is termed lumen maintenance, and is described in manufacturer datasheets or application notes as a curve plotting light output against time. A number of curves may be presented, showing lumen maintenance at several operating temperatures. Using these curves, the designer can target a specified lifetime by determining the drive level for the required light output and then ensuring the operating temperature does not exceed that of the target lumen maintenance curve. This requires careful attention to thermal management.

Power LED packages are designed to minimise thermal resistance between the die and the edge of the package. In many cases the LED die is mounted on a large metallic heat spreader that is exposed on the outside of the package to allow soldering to the PCB.

PCB materials featuring an Insulated Metal Substrate (IMS) have high thermal capacity, and are effective in removing heat from the LED via the soldered-down heat spreader. In some applications this may be sufficient to maintain the LED temperature within acceptable limits. On the other hand, additional heatsinking may be necessary.

In general, the larger the heatsink, the lower the operating temperature will be. Heatsinks from manufacturers such as Lamina, Tyco and Wakefield are designed to provide the maximum possible surface area for cooling, within small form factors suitable for use in applications such as bulb replacement or original LED-based lamp designs.

# New Methodologies and Innovations Fuel System Realization

**Steve Brown** and **Raj Mathur** from Cadence explain the need for a new system design approach that allows both earlier software development and faster silicon development, along with earlier and more frequent system integration steps

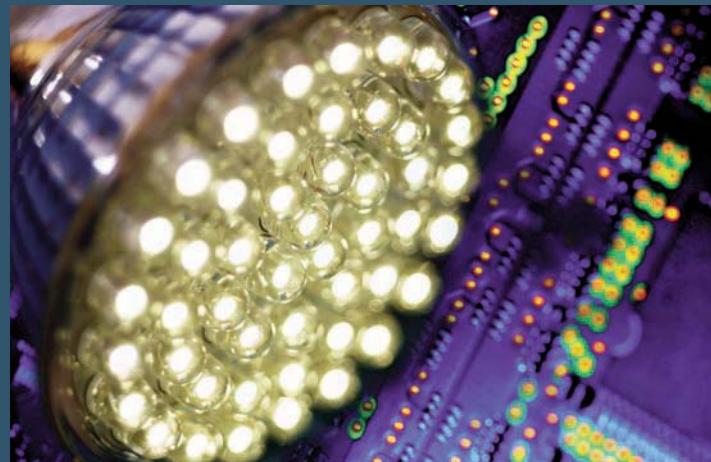

**Figure 1:** SoC development costs have soared from \$20m at 90nm to nearly \$100m at 32nm. Software is the fastest growing part of the cost [source: IBS Inc.]

**FUELLED BY MASSIVE** functional capacity, high performance and low-power silicon processes, and exploding software application content, the pace and scope of electronics innovation is accelerating. The challenges of bringing together increasingly complex systems are also growing, confronting traditional approaches with out-of-control verification costs and missed market windows. What's needed is a new system design approach that allows both earlier software development and faster silicon development, along with earlier and more frequent system integration steps.

This new methodology must enable a unified hardware/software development and verification environment, and allow the specification, analysis and verification of constraints such as timing and power in the context of the software and the system. This article highlights recent advances in system design, transaction-level verification and software development that support this kind of unified environment. The article discusses the role of standards and explains the productivity gains behind a transaction level modelling (TLM)-to-GDSII design and verification flow.

Specifically, this article looks at the challenges and emerging methodologies behind System Realization, which is defined in the EDA360 vision paper as the development of a complete hardware/software platform that provides all necessary support for end-user applications. System Realization recognizes that the value and differentiation of new devices lies increasingly in the application software. The article concludes by noting some practical innovations, available now, that will help design teams build an effective System Realization flow.

## System Realization Productivity Challenges

The economy is motivating consumers to be more selective in their electronic product choices. Manufacturers must satisfy demands to increase application capabilities, provide longer battery operating lifetimes and hit a narrow consumer shopping season. Electronic system developers are coping with the consequences of exponential growth in software and are facing a need to accelerate all aspects of system development.

## Shortening Project Schedules

Short project schedules do not represent a new challenge, but the problem is becoming worse with rising complexity. With more and more software content in chips – whether embedded or application – RTL design and verification are no longer the main cost bottlenecks as a system-on-chip (SoC) goes to tapeout. System development, embedded software development and verification are rapidly becoming the key cost components of the electronic design process. As the cost rises, the need to shorten project schedules with methodologies that leverage trusted RTL simulation tools becomes paramount.

## Increasing Task Complexities

With software increasingly driving hardware content, verification teams are searching for ways to revise, or preferably augment, their current verification strategies. This is because current verification strategies are running out of steam. Current verification strategies lack a consistent verification methodology from ESL to GDS-II, lack interoperability of the different tools used in the entire flow, lack re-usability of the same or similar testbench to drive verification at different abstraction levels through the entire flow, and lack a common dashboard to monitor and capture key metrics from all verification tools used in the entire flow.

## Growing Importance of Design for Power

Power consumption has direct impact on product usage, heat, form-factor and economics. Battery life is a key differentiator for almost all mobile devices and can be as important as some of the functionality. Power consumption correlates with generated heat and can make a device expensive to cool, or too hot to operate. Lower power consumption can also enable miniaturization of devices such as hearing aids or other space-sensitive considerations. And power consumption costs money in wired or battery energy expenses.

The challenge is that power consumption has been an outcome of the design process, one that can't be measured until late in the project. What is

needed is a way to assess the power consumed by the device under different operating conditions, running different software application stacks, before building silicon. Even more valuable is the capability to use power estimates to make architectural choices early in the project, before a significant effort is expended.

### System Realization Methodology Trends

In order to meet the expectations and requirements of today's rapidly evolving electronics markets, devices must be designed from the perspective of the user applications, with all components designed to meet the required function, form-factor and performance characteristics. This is a dramatic change from the past where semiconductor innovations drove device design. The change in orientation of the design relationship is demanding changes from the design tools and methodologies used in the past. An emphasis is now being placed on the decomposition of the system at each level into sub-components, refining requirements for each sub-component, rapid creation and verification of each sub-component, re-integration of the sub-components and, finally, verification of the integrated capabilities. Several necessary innovations have emerged to enable the next wave of design methodologies and tools that automate these processes.

### Earlier Software Development and Integration Testing

Formerly it was possible to develop software by using early silicon device samples from the manufacturer. Early pressures on system development have led to a widespread use of pre-silicon emulation to perform the integration validation and support early software development. The significant growth in applying FPGA prototype boards for software development is another form of hardware-assisted verification using the design before samples from an ASIC process are available. Still, this stage is primarily only possible after RTL design is completed. In today's rapidly evolving electronics marketplace this doesn't advance software development early enough in the project schedule.

Some system developers today are using virtual prototypes of the system to enable even earlier software development. The idea is to model the device or board with a collection of executable models that are created much earlier than the silicon, and provide enough accuracy and performance to develop software and perform some verification. Different approaches are being applied using service-based modelling approaches, proprietary modelling languages and technologies, and standard SystemC.

Virtual prototype models are mostly used only for software development, and the creation of RTL remains a separate, duplicate modelling effort. High-level synthesis of C/C++/SystemC is emerging as a way to unify virtual prototype models with the silicon design flow. Most would agree it remains difficult to create such models early enough, economically enough and with enough performance and accuracy to feed into the RTL-based design flow.

### Expanding Virtual System Model Opportunities

Even project teams that are successfully using virtual prototypes are

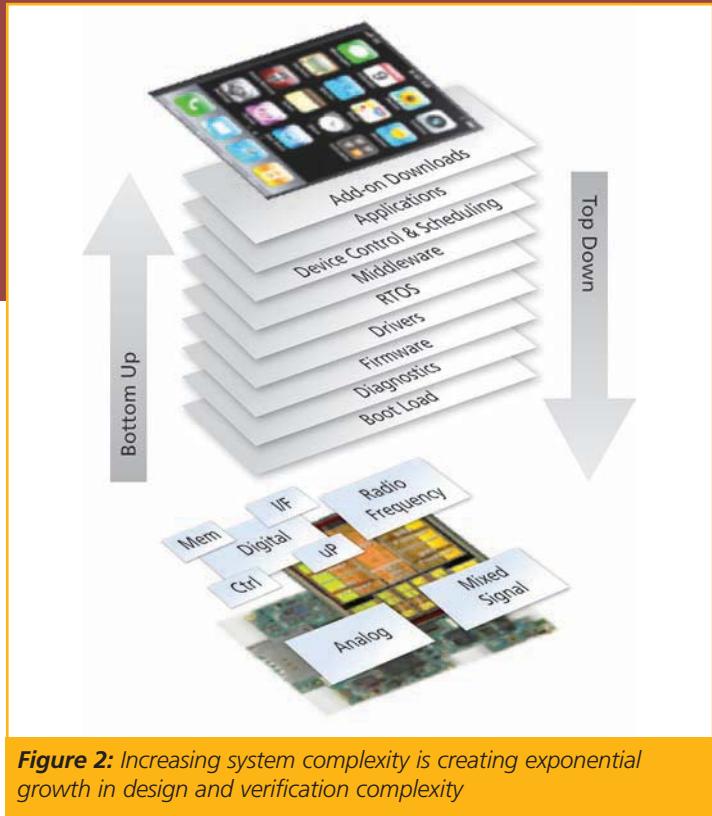

**Figure 2:** Increasing system complexity is creating exponential growth in design and verification complexity

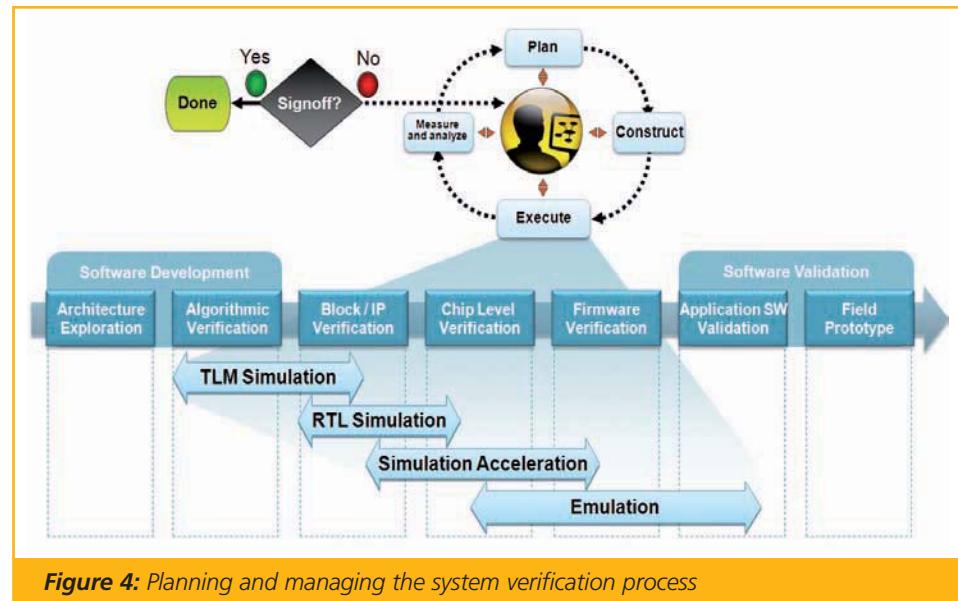

spending a great deal of effort to do so. In addition, they are often also utilizing an emulation approach, as well as building FPGA-based prototypes. Each of these systems provides different benefits in software development (see **Figure 3**).

In order to fully develop software and hardware in parallel, each of the solutions needs to enable early software development, find bugs earlier in the project and ensure high quality system validation.

### Mixing of Multiple Abstractions for Verification

Very few design teams can afford to start their designs from scratch. Derivative designs increasingly consist of components at multiple levels of abstraction. While some components may be new and can be defined initially at the ESL abstraction in a high-level language for fast model efficiency, other components may be available only in RTL form, while others may be available as gate-level descriptions with some pre-existing qualifications. These are all models of the system at different abstraction levels with varying degrees of model accuracy and pre-qualification.

A single verification environment that can accept the different model representations is required for application-driven system level verification. Driving the multi-abstraction 'design-under-test' with automated testbenches and that can be applied within a multi-abstraction verification environment will accelerate system level verification. If a single verification environment isn't readily available, then the next best option is a hybrid of verification engines coupled together cohesively with tool interoperability. The tools can include TLM simulation, RTL simulation and hardware-assisted verification.

### Standardization of Design and Verification for Increased Reusability

Increasing design reuse presents both opportunities and demands to define standards. RTL design code has been notoriously difficult to integrate into new SoCs. Reusability involves far more than a common structured

|                           | Execution Speed | Timing Accuracy | Bring-up/Debug |

|---------------------------|-----------------|-----------------|----------------|

| Virtual Prototype         | ●               | ●               | ●              |

| FPGA-based Prototype      | ●               | ●               | ●              |

| Emulation-based Prototype | ●               | ●               | ●              |

**Figure 3: Virtualization capabilities by technology**

approach to microarchitecture. As virtual platform methodology becomes more common, the ability to reuse models from different sources becomes an imperative, placing demands on modelling techniques, abstractions and coding styles. Enabling high-level synthesis flows also places standards requirements on the design methodology.

Design modelling standards such as SystemC, TLM1, TLM2 and the SystemC synthesizable subset are being driven by the Open SystemC Initiative (OSCI). Using multiple verification engines with testbench automation requires the Unified Verification Methodology (UVM) and Standard Co-Emulation Modelling Interface (SCE-MI) standards.

### Expanding Use of Transaction-Based Methodologies

One of the most important standardization trends is the use of transaction level modelling as the basic architectural concept for design and verification methodologies. Transaction level modelling is the core methodology that enables interoperability between virtual prototyping, high level synthesis, transaction-based acceleration and the integration into existing RTL design and verification approaches. This transition in methodology is needed to enable the modern technologies required for system design and verification.

The transaction modelling concept is required by virtual prototyping to enable quick model creation and fast simulation speeds needed for software development. Recent high-level synthesis tools and methodology enable direct use of those models for rapid creation of RTL designs. And transaction-level modelling is the underlying principle in the Unified Verification Methodology (UVM), enabling a single verification environment to be applied to TLM design simulation, RTL simulation and RTL acceleration.

Transaction-based acceleration is a technology that accelerates simulation using specialized hardware to speed the computation of instructions compiled by a simulator. Traditionally, the hardware has been driven with Verilog, VHDL, SystemVerilog or e based testbenches, but there is an increasing demand for the hardware to be directly driven from SystemC or C/C++ based testbenches, enabling software and firmware developers to accelerate their code verification. The utilization of hardware-assisted verification is further expanded as the industry embraces high-performance Universal Verification Methodology (UVM) and Metric Driven Verification (MDV) built on transaction based acceleration technology.

### Moving to TLM Abstraction for Design and Verification

The industry is moving to a higher TLM abstraction to increase productivity for creating new hardware IP. The reduction in lines of code speeds IP creation time, reduces the number of bugs that are inserted and speeds verification performance and turnaround time. Cadence Incisive Enterprise Simulator SystemC functional verification throughput can be as high as 10 times over RTL, enabling more exhaustive UVM-based verification of the device functionality before committing to RTL.

Designer productivity is increased by the faster creation of SystemC

designs, as well as automated high-level synthesis with Cadence C-to-Silicon Compiler to produce the RTL. Describing IP at a higher level of abstraction also increases IP reusability and implementation in different process nodes. Design teams can leverage the synthesis tool to create optimal microarchitectures for different system specifications, rather than coding RTL by hand each time.

A comprehensive methodology guide is available from Cadence to lead engineers and teams through key decisions for modelling, UVM functional verification environment creation, IP reusability and synthesizability. The guide comes with examples that help with learning as well as a book, "TLM-driven Design and Verification Methodology".

The unique integration of C-to-Silicon Compiler with Cadence Encounter RTL Compiler enables automated closure on a microarchitecture that meets Quality of Results (area, timing, power) constraints. C-to-Silicon Compiler is built with a database that enables efficient ECO implementation and is integrated with the RTL Compiler ECO flow. This enables minimal netlist changes to be introduced even when functionality at the SystemC input is changed. This same database enables Incisive Enterprise RTL simulations to support SystemC source level debugging that is tightly synchronized with the RTL debugging and simulation.

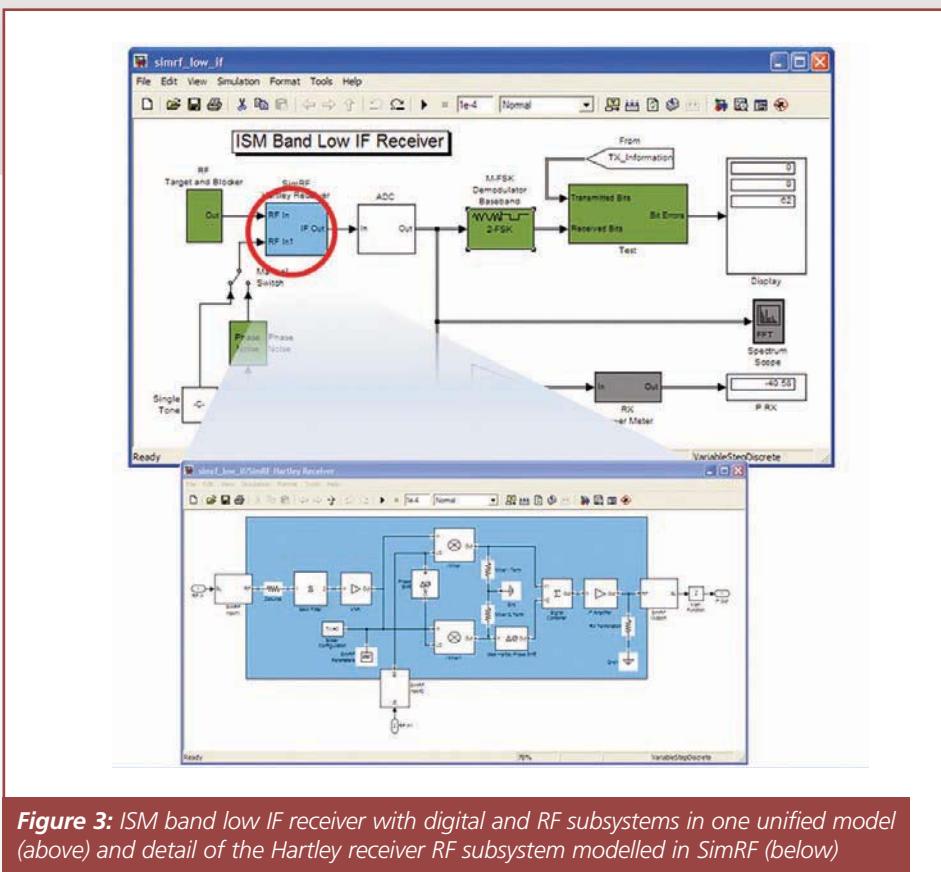

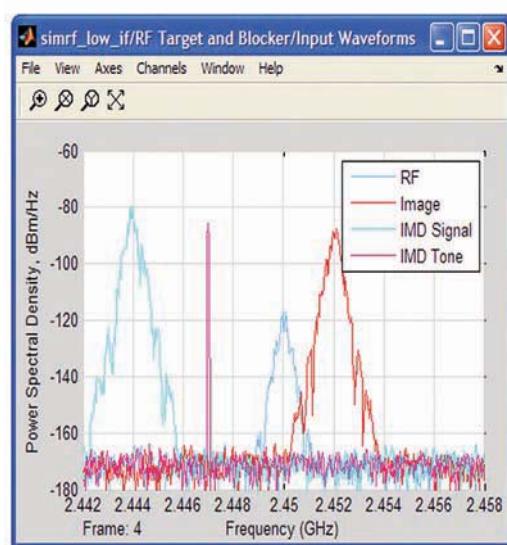

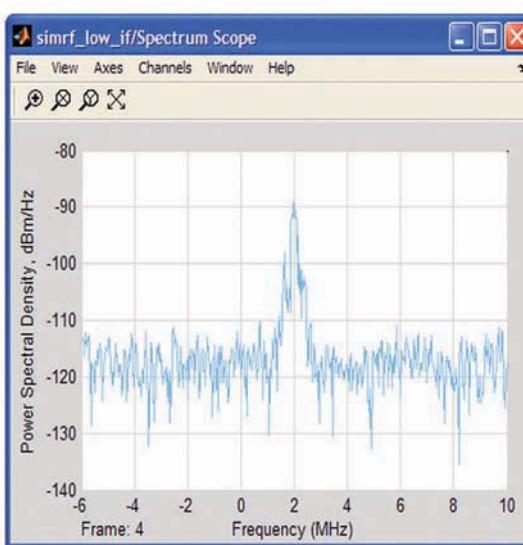

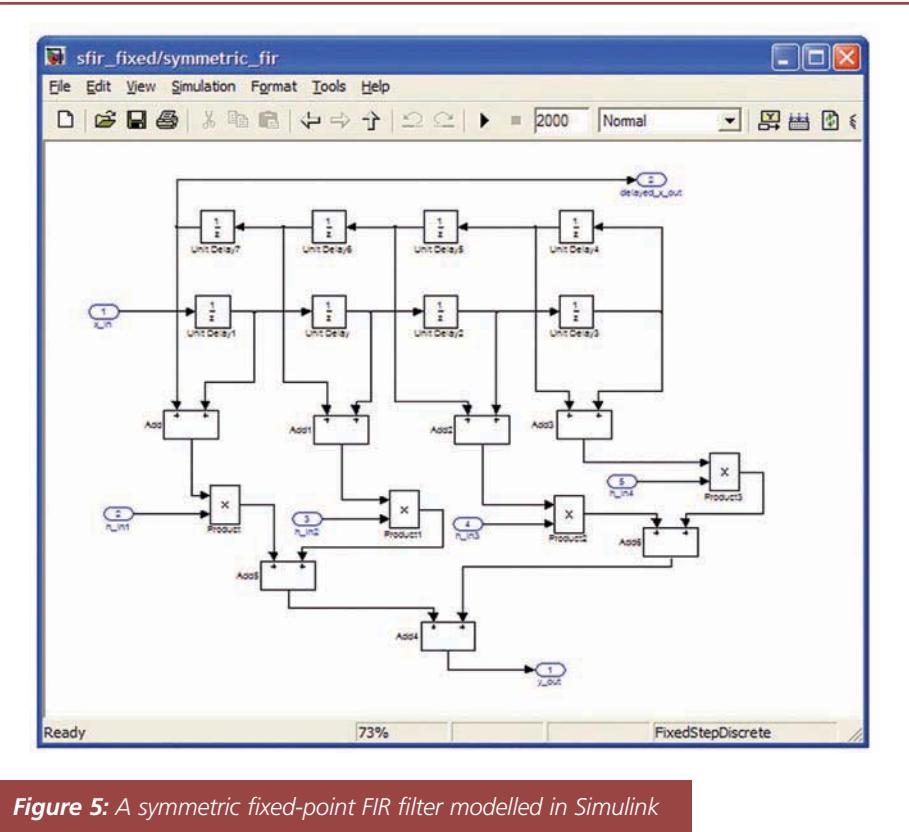

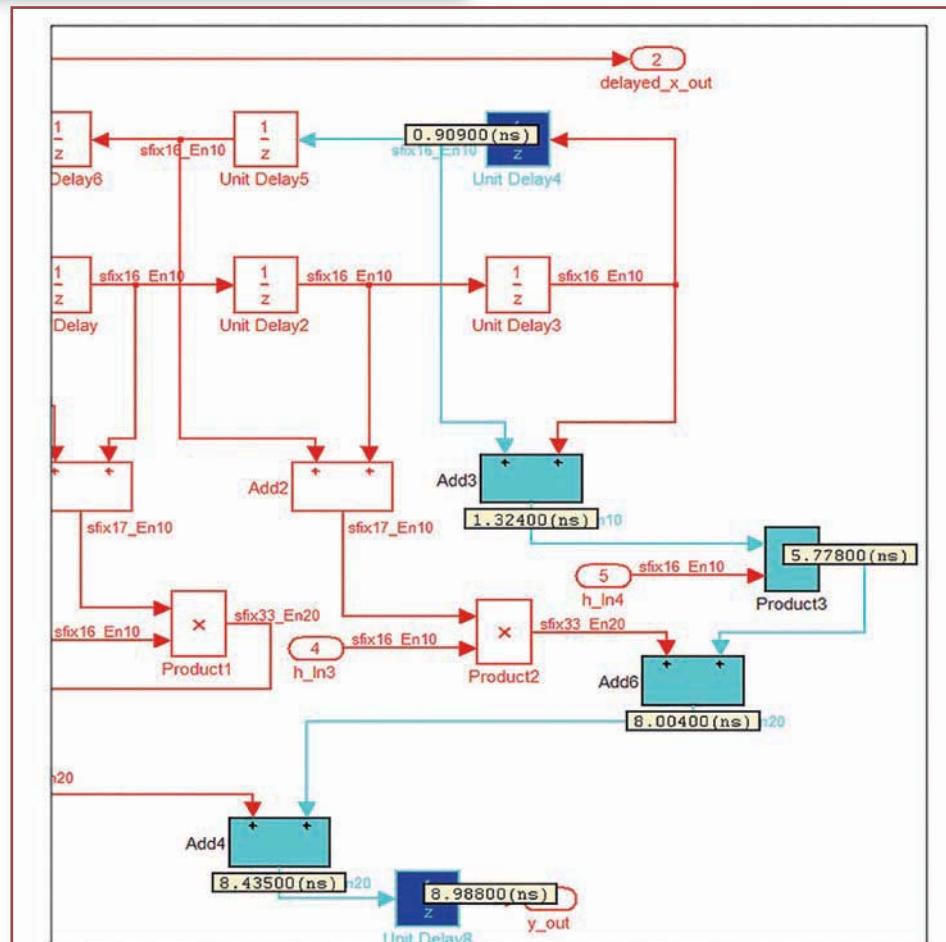

### Utilizing a Continuum of System Platforms