July 2012 Volume 118 Issue 1915 £5.10

www.electronicsworld.co.uk

## Electronics WORLD THE ESSENTIAL ELECTRONICS ENGINEERING MAGAZINE

a tti company

01494-467490 | uk@mouser.com

Distributing the Most Advanced Embedded Solutions from the Worlds Top Manufacturers.

Technology Fast-acting electronic nose uses QTC material

Special report Embedded design

**Products** Various PCB hardware products

# **Any Questions?**

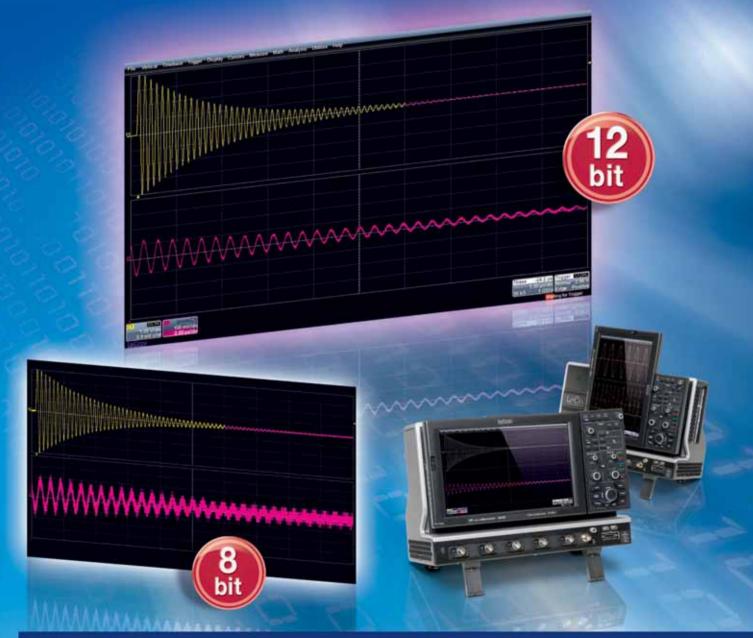

Unmatched Signal Fidelity and Excellent Measurement Precision WaveRunner High-Resolution Oscilloscopes

- 12-bit ADC Resolution, 15-bit with ERES

- ± 0.5 % DC Accuracy

- Complete Analysis Capabilities incl. Spectrum Analysis Package

- 1 mV/Div at full Bandwidth

- 1.95 µV Smallest Voltage Step

- 400 V maximum Offset

- 36 Ch. Mixed Signal Solution

Phone: 01753 725371 www.lecroy.co.uk

Cover supplied by **MOUSER ELECTRONICS**

Make us part of your electronics line-up. FIND IT. DESIGN IT. BUY IT.

customers and suppliers, and with safety practices relating to working with electrical/ electronic circuitry - particularly as regards electric shock, fire hazards and explosions.

rswww.com/electronics

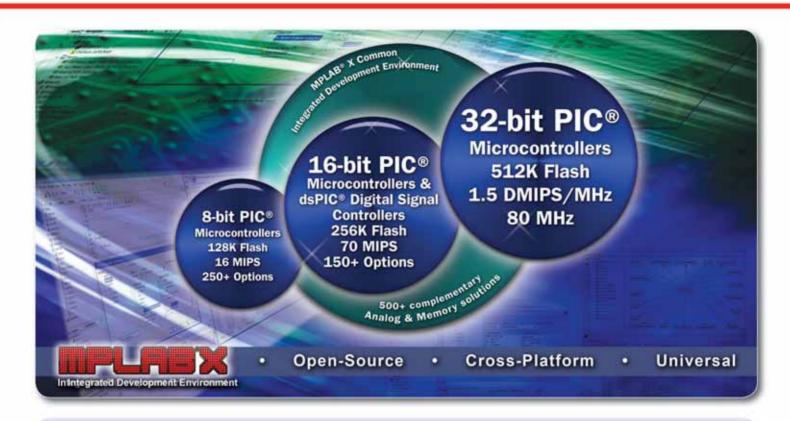

### One platform for 8-, 16- and 32-bit development - with Microchip's MPLAB® X IDE

MPLAB® X IDE is the free, integrated toolset for all of Microchip's 900+ 8-, 16- and 32-bit PIC® Microcontrollers, dsPIC® Digital Signal Controllers, and memory devices. Based on the open-source NetBeans platform, MPLAB X runs on Windows® OS,MAC® OS and Linux, supports many third-party tools, and is compatible with many NetBeans plug-ins.

MPLAB XC compilers help increase code speed of any PIC<sup>®</sup> Microcontroller or dsPIC<sup>®</sup> digital signal controller by 30%, whilst also cutting code size by 35%. These new compilers give designers the choice of Free, Standard or Pro code optimisation levels for 8-bit, 16- or 32-bit development, or a single C compiler suite to support all Microchip Microcontrollers and digital signal controllers.

Microchip's tool chain of compatible compilers and debugger/programmers operate seamlessly within the universal, cross platform and open-source MPLAB\* X integrated development environment, reducing both learning curves and tool investments.

#### START DEVELOPING TODAY

Download a free copy of MPLAB X and choose from a choice of new C compilers:

- MPLAB XC8 for 8-bit MCUs

- MPLAB XC16 for 16-bit MCUs and DSCs

- MPLAB XC32 for 32-bit MCUs

- MPLAB XC Suite for all 900+ PIC MCUs and dsPIC DSCs.

### Evaluate MPLAB X today! www.microchip.com/get/eumplabx

Microcontrollers • Digital Signal Controllers • Analog • Memory • Wireless

TREND • 05

### DESIGNING THE NETWORK FOR BIG DATA

The tidal wave of Big Data is washing over today's businesses. Big Data is not only measured in the quantity of data traversing the network, but according to Forrester Research, it is defined as the techniques and technologies that make handling data at extreme scale economical.

Global data volume is increasing 40% annually, much of this generated by the growth in mobile traffic. The value to public and private organisations is enormous; global management consulting firm McKinsey estimates that in the European public sector alone, Big Data will contribute €250bn.

How can today's networks cost-effectively handle the high volume of interactive, multimedia traffic? Just adding more bandwidth will not solve the problem. The value chain of network providers spanning mobile backhaul, through carrier transport, to the data centre must reconsider networking to make it more costeffective and efficient to accommodate Big Data.

#### **Big Data Requires Big Changes in the Network**

How much data are we actually talking about with Big Data? The size of the datasets varies by sector, but they range from a few dozen terabytes to multiple petabytes. Moreover, Big Data introduces new technologies such as Hadoop and MapReduce. Unlike previous data transfer technologies that moved gigabytes of data in a single job, MapReduce can move multi-petabytes of data.

Big Data requires that the networking industry accelerates change, moving from legacy technologies in data transport such as SONET/SDH to high-value-per-bit and lower-cost-per-bit technologies such as Carrier Ethernet. In the data centre, networking switching is moving rapidly to 10-40Gbps and Ethernet is rapidly replacing older Storage Area Networking (SAN) technologies.

#### **Big Data Requires Flatter Data Centre Networks**

Migrating to Ethernet as an underlying transport will benefit all aspects of the transmission of Big Data. However, Ethernet on its own is not sufficient to handle the torrent of Big Data.

Network architectures also need to change to become flatter and more flexible. For example, in today's typical data centre, the

EDITOR: Svetlana Josifovska +44 (0)845 4790343 Email: svetlanaj@stjohnpatrick.com DISPLAY SALES: John Steward Tel: +44 (0) 20 7933 8974 Email: johns@stjohnpatrick.com DESIGN: Tania King Email: taniak@stjohnpatrick.com PUBLISHER: Wayne Darroch ISSN: 1365-4675 PRINTER: Pensord Magazines & Periodicals Migrating to Ethernet as an underlying transport will benefit all aspects of the transmission of Big Data. However, Ethernet on its own is not sufficient to handle the torrent of Big Data

network architecture consists of one or more L3 core routers, multiple L3 access routers, L2 aggregation switches, load balancers, as well as top-of-the-rack switches. A hierarchical network forces data centre operators to oversubscribe network resources up to 200:1. Taking advantage of new 10Gbps and 40Gbps Ethernet and higher performance silicon will help drive the price performance up. Taking advantages of new innovations in network virtualisation enable flatter and better performing networks.

#### The Future of Big Data Networking is Software

The key to delivering higher performance, more optimised networks is a software-defined networking architecture using a centralised control plane and fast forwarding data planes based on merchant silicon. The Open Networking Foundation (ONF) is championing the standardisation of this approach, along with OpenFlow, a protocol to enable distributed control plane implementations.

Key software networking vendors have been offering modular, portable routing/switching software for more than a decade to leading network equipment manufacturers. By leveraging innovations and the ONF standards, network equipment providers can optimise the price-performance of Ethernet networks.

Software Defined Networking is in its infancy, but the growing demands of Big Data will continue to drive new innovations in networking. Today, service providers and data centre operators can exploit Ethernet to offer more economically-attractive mobile and Big Data transport services. In the near future, the network equipment industry will accelerate the adoption of SDN to support Big Data. The successful companies will ride the wave of Big Data, transform their networks and capitalise on new business opportunities.

Sandy Orlando is Vice President for Worldwide Marketing at IP Infusion

SUBSCRIPTIONS: Tel/Fax +44 (0)1635 879361/868594 Email: electronicsworld@circdata.com SUBSCRIPTION RATES: 1 year: £51 (UK); £74.50 (worldwide)

St John Patrick Publishers

in

Follow us on Twitter @electrowo

Join us on LinkedIn http://linkd.in/xH2HNx

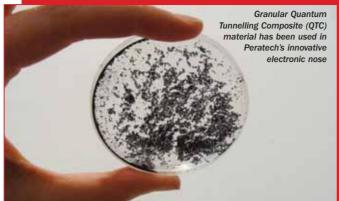

### PERATECH CREATES FAST-ACTING ELECTRONIC NOSE USING QTC TECHNOLOGY

Touch technology innovator Peratech is developing an 'electronic nose' using its award-winning Quantum Tunnelling Composite (QTC) material. This new sensor technology detects the presence of Volatile Organic Compounds (VOCs) very rapidly and can recover in a matter of seconds – beating all other techniques currently available.

QTC materials change their resistance when a force is applied and, in this case, the polymer content of the composite swells when exposed to VOCs. One form of Peratech's sensor uses a granular type of QTC material that provides a high surface area for absorption, enabling it to detect levels of VOCs in the region of 10-100ppm. The sensor rapidly recovers once the VOCs have gone from the surrounding atmosphere - and it is the speed of sensing and recovery that marks the difference between QTC sensors and those using other sensing technologies. An additional feature of the QTC technology is that it has very low power requirements.

The conductive particles used in the QTC electronic nose have nano-sized features and are distributed in a nonconductive polymer. When a force is applied or swelling occurs, the particles move close enough for the electron flow between the particles to alter due to an effect called quantum tunnelling. The polymer used is selected for its response to the particular VOCs to be monitored. The company believes licensing the technology will lead to a variety of products.

"The electronic nose application was developed in conjunction with the Quantum Tunnelling Composite research group at the University of Durham," said David Lussey, CTO of Peratech. "We are now looking for companies who are interested in licensing the technology from us to develop products."

### **DuPont Novel Formulation Brings Greater** Efficiency to Solar Cells

DuPont Solamet PV17x photovoltaic metallization paste raises efficiency in standard solar cell constructions and its unique properties enable Lightly Doped Emitter (LDE) cell designs, says the firm.

LDE is a strong differentiator for solar cell producers as it can boost efficiency by up to 0.4%. "This product has a two-stage advantage, since on its own it can raise efficiency by up to 0.2%, and when used to enable LDE, it can raise efficiency by up to 0.4%,"

DuPont Solamet photovoltaic metallizations boost the efficiency of photovoltaic solar cells

said Peter Brenner, photovoltaics global marketing manager at DuPont Microcircuit Materials. "Solamet PV17x series continues to advance technology to help meet the industry's goal of 20% efficiency by 2012."

DuPont says that Solamet PV17x is the most advanced composition in the market, allowing contact to be made to the most lightly doped junctions. Doping diffusion optimization is a key area of experimental study in the photovoltaic industry for the design of high efficiency cells. Diffusion optimization has been significantly limited by the inability of traditional frontside photovoltaic silver pastes to contact lightly surface-doped emitters. Prior to Solamet PV17x being released, the industry had no real commercially available option for making a screen printed frontside metallization that could economically and practically enable an LDE.

Extensive testing is underway within DuPont and in collaboration with several research organizations as well as in customer trials to fully characterize and continue to advance this technology. RWTH-Aachen University recently published a comparative study involving Solamet PV17x and four competing metallization pastes. Solamet PV17x outperformed four competing products, demonstrating its ability to contact 100 Ohm/sq emitters on multicrystalline cells - the first time this had been achieved - with lightly doped phosphorous surface concentration. This enabled an efficiency increase of one full percent versus the homogenous emitter base line and 0.4% higher efficiency was confirmed versus laser doped selective emitter technologies.

"We presented a characterization of POCI3 parameters influencing the electrically active phosphorus concentration profiles by electrochemical capacitance voltage measurements," said Ali Safiei, PhD researcher at the Institute of Semiconductor Electronics at RWTH Aachen University. "For the first time we could demonstrate a successful

direct contacting of an optimized high sheet resistance emitter at  $100\Omega/sq$ by increasing the n++ layer and at the same time reducing the dead laver. Multicrystalline silicon solar cells were fabricated using five different silver pastes resulting in an absolute efficiency gain of  $\Delta \eta = 1\%$ in comparison to a standard  $55\Omega/sq$ emitter. Based on these investigations we evaluated a  $160\Omega/sq$  emitter and could successfully demonstrate by laser doping that a n++ layer of up to 25nm depth (a Lightly Doped Emitter) leads to high FF and an absolute efficiency gain of  $\Delta \eta >$ 0.6%."

The breakthrough formulation of Solamet PV17x also enables cell makers to use up to 15% less material, in line with the company's intent to accelerate product developments that help the photovoltaic industry reduce its dependence on silver metals and offset some of the impact that rising silver prices have on the cost of producing solar cells and modules.

### **Research Projects Combine to "End the Segregation Between Control, System and Software Engineers**"

The research efforts "Project "P" and "Hi-MoCo" (High-Integrity Model Compiler) have combined to provide an open-source, tunable and qualifiable code generation framework for domain-specific modeling languages.

The key idea is to allow control engineers, system engineers and software engineers to easily collaborate for system-level model integration, verification and final optimized code generation targeting the Ada 2012, C/C++ and VHDL languages. Typically, control engineers use Simulink, Stateflow and Scicos/XCos; system engineers use SysML/MARTE and AADL; and software engineers use UML.

"The ultimate goal of these projects is to end the segregation between the control, system and software engineers," said Franco Gasperoni, Managing Director of

AdaCore, one of the project's participating companies and technical coordinator.

AdaCore is working closely with the IB Krates team and members from IRIT (Institut de Recherche en Informatique de Toulouse), the principal architects of the ITEA GeneAuto project and technology on which "Project P" and Hi-MoCo are based. The three companies will play a major role in the crossdomain qualification effort spanning the avionics, space and automotive sectors.

"A major bottleneck in the model-driven development of software for avionics, space and automotive systems is the integration of heterogeneous models and the lack of comprehensive verification and code generation technologies," said Gasperoni.

The current state-of-the-art is to

#### **Project P**

Project P is a three-year research project financially supported within the French FUI 2011 funding framework. Headed by Continental Automotive France, it involves the collaboration of 19 partners including major industrial users from the avionics, automotive and space sectors that count Airbus, Astrium, Continental Automotive, Rockwell Collins, Safran, Thales Alenia Space and Thales Avionics among its ranks, as well as technology providers such as AdaCore, Altair, STInformatique and Scilab Enterprise; service companies ACG Solutions, Aboard Engineering and Atos Origins; and research centres ENPC, IRIT-INPT/CNRS, INRIA, ONERA, Lab-STICC/Université de Bretagne Sud. To find out more go to http://www.open-do.org/projects/p.

#### **Project Hi-MoCo**

Hi-MoCo P is a two-year research project financially supported within the Eurostar 2011 funding framework. It supports the collaboration of IB Krates (Estonia), IRIT and AdaCore (France).

perform integration on generated sources. The trio are proposing to do this at the model level to verify integration issues well before models are mature enough for code generation.

"Project "P" and Hi-MoCo are open-source research efforts, which are supported and partly funded by the French and Estonian national governments and the European EUREKA agency.

### MOUSER ELECTRONICS: DISTRIBUTING THE MOST ADVANCED EMBEDDED PRODUCTS FROM THE WORLD'S TOP MANUFACTURERS

he creation of every new smartphone, portable medical device, or automotive driver assist feature serves as a constant reminder of how technology never stands still. "Quickly innovate or risk being left behind" is the industry maxim heard everywhere. And nowhere is this cry more prevalent than among design engineers faced with complex task of delivering the next technological wonder or "it" item.

As the convergence of communications and computing functions within components continues to advance, embedded systems are transforming into complex systems. Major components of embedded systems are microcontrollers (MCUs), digital signal processors (DSPs), analog, real-time operating systems (RTOS), industry-specific protocols and interfaces. Embedded systems also span digital and analog, sensors and actuators, software,

mechanical items and other components.

Ever present are new opportunities to develop and build more powerful, energy-efficient solutions around minimization of size and low cost. mportant design characteristics at work are low power, real-time responsiveness, low thermal dissipation, small physical form factor, memory, regulatory concerns, ruggedness in

design and other factors. All of this creates a major design challenge for engineers when it comes to the selection of processors, operating systems, etc., as demands for functionality increase with rising time-to-market pressures.

"In today's world, convenience means portable, which in turn means low power systems running on batteries for sleep mode," explains Kevin Hess, Mouser Vice President Technical Marketing. "Although low power has always been a goal, the trend towards microcontrollers with ultra-low-power consumption has accelerated in recent years."

Mouser Electronics stands at the forefront in embedded processors and development tools, stocking and quickly shipping the latest, leading-edge solutions that are smarter, greener and more convenient. With its eight Customer Support Centers across Europe's largest technology hubs, it's not surprising to learn that Mouser has rapidly grown into a global engineering resource and leading worldwide distributor for advanced semiconductors and electronic components among design engineers across Europe.

Being green doesn't necessarily mean low power, Hess adds. To reduce the carbon footprint, engineers need to make the most efficient use of power consumed. Embedded system engineers also face the need to update their programming, debugging and testing skills to draw the best out of designs. Thus, many semiconductor companies are aligning with third-party development tool manufacturers for their expertise. Hess says open source technology is greatly influencing the design of low-cost, highly functional and adaptable solutions.

Mouser has established itself as the go-to source for the latest MCU and embedded products from the world's leading manufacturers, including Texas Instruments, Microchip Technologies and Freescale Semiconductor, to name a few. Mouser also stocks the newest embedded products from Laird Technologies, Olimex, Digi Int'l, Lantronix, Netburner and Roving Networks, carrying a full suite of development tools, including starter kits, evaluation boards, programmers, debuggers and emulators for rapid evaluation and testing of designs. Product numbers are updated daily on www.mouser.com and labeled as new technology or flagged NRND (Not Recommended for New Design) and/or EOL (End of Life) and made available via online, catalogue or mobile.

"With the requirements of both the end consumer and electronics industry need for embedded design increasing so rapidly, every link in the chain – from semiconductor manufacturer to development tool maker to distributor – must constantly be on the cutting edge," explains Hess. "Our goal is to help design engineers around the world get their products to market faster. We do that by supplying the most advanced products from the top suppliers. Therefore, customers can count on Mouser to deliver What's Next in authorized embedded processors and development tools."

Mouser Electronics UK Suite C, First Floor, Artisan Building Hillbottom Road, High Wycombe, Bucks. HP12 4HJ, United Kingdom Tel: 01494 467490 Email: uk@mouser.com

**Міскосні**р

<sup>1</sup> Uk.mouser.com Distributing semiconductors and electronic components for design engineers.

#### Authorised Distributor

## Distributor for Semiconductors and Electronic Components

Purchase all the brands design engineers want and trust. Come to Mouser for what's next from these industry leaders.

Suite C, First Floor Artisan Building Hillbotteen Road High Wycombe Bucks, HP12 4HJ +44 (0) 1494-467490 uk@mouser.com

a in company

Mouse and Mouse Declarate as regulared Indexarts of Mouse Declarate, Nr. Other products, type, and torgony haves method heads, may be trademarts of their respective series

## The Design Engineer's Perspective on the Supply Chain

WHERE DO ENGINEERS GO FOR MORE INFORMATION ABOUT THEIR PRODUCTS AND PROJECTS? **CHRIS SULLIVAN**, HEAD OF GLOBAL SOLUTIONS MARKETING AT PREMIER FARNELL FOR ELEMENT14 HAS SOME ANSWERS FOLLOWING A SURVEY

he electronics industry's key focus in the past decade has been on the supply chain: globalizing it, reducing its costs and risk, optimizing it and auditing it for ethical conduct. As important as these issues are, this intense focus on suppliers has overshadowed perhaps the most important determinant of a successful supply chain: the design phase.

Like captains of huge ships, electronics design engineers make hourly and daily decisions that steer their companies' supply chains toward new technologies, divergent regions, lead-time factors, environmental sustainability and competitiveness. But it's easier said than done.

The four stages of design – concept, designing, prototyping and preproduction – all have their challenges for electronics engineers. Today, electronics design engineers are burdened with lengthy and disparate processes comprising dozens of Like captains of huge ships, electronics design engineers make hourly and daily decisions that steer their companies' supply chains toward new technologies, divergent regions, lead-time factors, environmental sustainability and competitiveness

technical documents, design tools, product searches, evaluations, regulatory requirements and promises of availability.

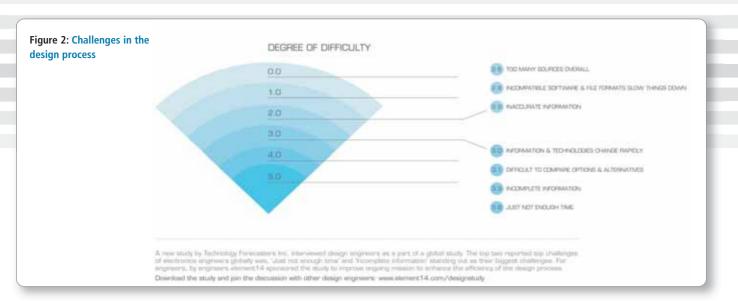

In a recent survey, element14, Premier Farnell's online community for electronic design engineers, teamed up with Technology Forecasters Inc (TFI) to ask 328 design engineers around the world how they think about their design process. An overwhelming majority of respondents voiced similar top three concerns in the design process:

- 1. Increased time pressures: Initial design stages before prototype assembly and testing typically require the most time and effort to gather all the necessary information. There is never enough time to properly utilise every relevant source.

- 2. Incomplete or inaccurate information from relevant sources: Information overload is not as much an issue, as is it's quality and completeness. This prolongs the design process further.

- 3. Difficulty comparing options and alternatives: While top-level information about component characteristics is easily available, the more detailed, sophisticated and time-specific information and tools can be very difficult to locate. Naturally, the Internet has become a

critical tool in the engineering design process.

| Design stage                        | Average percentage of time spent<br>finding and aggregating information,<br>data, and tools | Average degree of difficulty in finding<br>and aggregating the information,<br>data, and tools<br>(1 = extremely easy,<br>5 = extremely difficult) |                                                         |

|-------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Concept Development                 | 41%                                                                                         | 3.0                                                                                                                                                |                                                         |

| Detailed Design                     | 45%                                                                                         | 3.0                                                                                                                                                | ]                                                       |

| Prototype Testing and<br>Evaluation | 36%                                                                                         | 2.7                                                                                                                                                | Figure 1: Time<br>spent and the<br>degree of difficulty |

| Pre-Production                      | 25%                                                                                         | 2.5                                                                                                                                                | by stage in the design process                          |

Engineers rely most heavily on four primary sources of information: search engines, manufacturers' websites, distributors' websites and increasingly on professional social media tools.

#### Making Sense of the Information Overload

An Internet search is typically the first step in seeking out information. However, contrary to the general perception, search engines do not always present unbiased results. It's important to be aware of the bias that search engine optimisation can create. Nonetheless, to overcome the design challenges, engineers spend 50% of their time looking for information and tools online, coupled with the remaining time spent talking with vendors, customers and using internal tools.

A majority of respondents cited that

the earlier stages of design are the most challenging, with an average of 41% of design time spent on concept development. For the earlier stages of the design process, designers may use up to a few dozen sites, while the final two stages usually require fewer than 10. The range of online sources consulted is highly variable, based upon the requirements of the design as well as the habits of an individual engineer.

#### **ELEMENT14**

#### LAUNCHED IN 2009, ELEMENT 14 IS THE FIRST COLLABORATIVE COMMUNITY AND ELECTRONICS STORE FOR DESIGN ENGINEERS AND ELECTRONICS

ENTHUSIASTS. It distributes technology products and solutions for electronic system design, maintenance and repair and in the process brings together the latest products, services and development software. In addition, it is an innovative online engineering community where purchasers and engineers can access peers and experts, a wide range of independent technical information and helpful hints and tools.

Created by engineers for engineers, the Knode on element14 is an intelligent online search and knowledge tool that helps to select and buy the right solutions for a design, right from the start. Whether researching a new technology, designing an electronic product, or looking for parts to repair an existing system, element14 promises to find the answers and parts needed to keep a project on the fast track from the beginning.

The element14 community and the Knode address many of the top challenges facing engineers globally, helping save hundreds of hours in the design process.

Furthermore, specialised information as well as performance failure rates and component lifecycle data are particularly difficult to collect. The four toughest types of information to get are: (1) Reference designs;

(2) Application notes/technical papers;

(3) Simulation models: and

(4) Component pricing and availability. The challenge of finding regulatory information is also becoming more and more critical. Regulations concerning hazardous materials, energy use and other environmental considerations are increasing in number and differ greatly by country. Increasingly design engineers are expected to have some

competence in sorting through the complicated set of applicable regulations.

#### The Promise of **Social Media**

With so much information at now essential for the electronics hand, credibility of design process, but engineers are the information challenged to integrate all this source assumes significant importance in the design process. In the survey, more than 70% of design engineers said they relied heavily on online forums, blogs and engineering communities to collaborate with peers and share insight on

components and design processes. Technical forums, blogs and engineering communities offer the potential to provide a useful new dimension to how engineers find, aggregate and utilise

critical information for their designs. They provide a direct link between engineers, including those working at different stages of the design cycle and across different industries. They especially appeal to the younger generation of engineers who prefer social media over other forms of communication in general.

It is evident that the Internet provides a vast quantity of information and tools that are now essential for the electronics design process, but engineers are challenged to integrate all this data effectively within the short time-frame they have to complete projects. A lack of consolidated online

tools and databases hinder

"14 is evident that the Internet provides a vast quantity of information and tools that are

data effectively within the

short time-frame they have

to complete projects"

their ability to make accurate comparisons. Some 80% of design engineers said they would prefer online resources that: (1) cover multiple stages of the design cycle and (2)

provide consolidated information across

vendors, distributors, publications and other players in the supply chain.

#### The Silver Lining for Design **Engineers**

The study underscores design engineers' unrestrained call-to-action for better ways to access the

information they need. The design process can be enhanced by giving engineers consolidated design resources, increased collaboration with peers worldwide who are working on similar stages of the product design lifecycle and access to reliable search sources.

"I'd like to search by function of the component, or to a lesser degree by application," said one engineer in the survey. "I don't like application searches, because they assume that only particular functional devices pertain to a given application, and it's too restrictive of my ability to use my imagination and creativity. They might say 'only this memory is appropriate for automotive'. Instead, I'd like to see the parameters: size and type of memory, package type, cost, DRAM, SRAM, etc., with check boxes to select the parameters that I'm interested in. By searching for parameters, you can zero in on what you want."

#### Intelligent Consolidation of Information

It may not be soon that a single resource aggregates all component information, design tools, regulatory data, parts availability, pricing and other relevant data that the engineers report they need to ensure a successful start to the supply chain. In fact, from studying engineers' processes around the world across a variety of company types and sizes, it is clear that engineers would not want to start and end their search with only one resource; some engineers explicitly stated that they would not trust a single "go to" entity. But by consolidating necessary and even "nice to have" information in a few objective, well-run search communities, engineers' processes will be more efficient and decisions more exact. The end result will be better products going to market, faster cycle times, fewer design changes and fewer surprises about cost, availability and regulatory compliance.

## Pulling Up the Ladder

**MYK DORMER** IS SENIOR RF DESIGN ENGINEER AT RADIOMETRIX LTD WWW.RADIOMETRIX.COM

he loss of analogue TV broadcasting in the UK is no longer news. It is an established fact and, with the availability

of low-cost receiving equipment for the digital terrestrial and subscription-free satellite services, this loss is little mourned.

The issue I wish to highlight here relates to the analogous switch-off of the analogue radio broadcasting services, as DAB and internet radio services become more widely adopted. This cut-off has been mooted several times in recent years, with service end dates ranging from 2015 to "after 2019", depending on the particular political mouthpiece or industry pundit speaking.

In my opinion the current digital audio broadcast service is a valuable addition to the existing spectrum of radio services we currently enjoy in the UK, but the idea that it could replace analogue broadcasting fills me with horror. My reason for this is not related to the already widely discussed issues of coverage, cost of receiving equipment or the fundamental quality of the received audio signal; my concerns are related to education.

Let me explain: I am an electronics engineer, specialising in radio frequency circuitry. I design radios and have done so for a very long time. The skills necessary to follow my career cannot be learned purely from the theory, in a classroom. There is a huge amount of practical, on the bench tinkering, which can only be learned by years of practical experimentation.

To follow this path, it is not enough to make a decision in the final year of, usually mostly theoretical, electronics degree "to be an RF engineer". You already need to be an enthusiast, an "amateur", an experimenter, and that is something that starts in childhood.

Like most engineers of my type, I started early with "crystal sets" and simple discrete transistor circuits, slowly increasing the sophistication of my receivers until (long before the GCSE examinations loomed) I had a good practical grounding in the practicalities of "radio circuits". My childhood knowledge was by no means cutting edge, and much of the time I had spent was applied to re-inventing things which would have looked old-fashioned in the 1940s, but it was fascinating and it gave me a fundamental interest in, and grasp of, the subject. There is a unique satisfaction to be enjoyed when listening to a radio station on a receiver that you have constructed yourself, from basic components.

Without analogue broadcasting (medium wave and later band II FM) such simple juvenile experimentation is quite simply impossible. An AM crystal set can be built with less than ten (mostly home made or improvised) parts, while a simple FM receiver kit might include less than thirty simple components. The complex digital coded OFDM transmissions of the DAB system cannot be received by such elementary, even "primitive", circuitry at all. There is no "entry level" to this sort of receiver design: even the simplest digital receivers are built around highly complex custom made integrated circuits, not available to the general public. Even with a complete, fully trained, engineer's knowledge the task of putting together a bench-prototype of a DAB radio is daunting. Without access to very specialised parts, I would need at least the processing power of a desktop PC to even decode the signal into audio. Even then, the specific "codec" algorithms used in the decoders are not public domain - they are "owned" by specific corporations.

By taking away analogue broadcasting, you take away the mechanism by which future radio engineers (and military signallers, and amateur radio operators) first encounter the technologies we need them to master, if the future generations of engineers our society needs are to thrive.

To find an analogy: it is as if we were to prohibit children from riding bicycles, while still expecting those same children to grow up into professional motorcycle-racers.

By taking away analogue broadcasting, you take away the mechanism by which future radio engineers first encounter the technologies we need them to master, if the future generations of engineers our society needs are to thrive

### EMBEDDED INSTRUMENTATION - CLOSING THE T&M GAP FOR BREAKTHROUGH TECHNOLOGIES

EMBEDDED INSTRUMENTATION IS FILLING A GAP IN TEST AND MEASUREMENT THE ELECTRONICS INDUSTRY HAS HAD FOR SOME TIME. BY **REG WALLER**, EUROPEAN REGIONAL DIRECTOR AT ASSET INTERTECH

ince the dawn of the electronics industry there's been a gap between technological advancement and the test and measurement (T&M) equipment needed to test it. This gap is finally closing, thanks to embedded

instrumentation.

Typically, technology advances by becoming faster, more complex, more integrated and capable of performing a wider range of tasks. Processors have become smaller and denser, chip-to-chip buses faster, and circuit board design and fabrication techniques much more complex.

The recent rise of embedded instrumentation has shown that certain segments of the industry are realizing that T&M requirements should be considered an integral part of any breakthrough in technology. Doing so accelerates the adoption of new technology by reducing the risks and speeding up return on investment associated with it.

#### **Embedding T&M**

Embedded instrumentation can be defined as the logic designed into semiconductors, used for design validation, test, debug, yield analysis and other T&M activities.

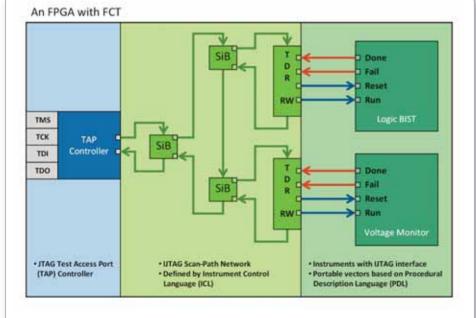

By its very nature, embedded instrumentation is a non-intrusive technology. Instead of physically placing a probe on a PCB test-pad or a chip pin, embedded instruments are able to launch test or validation routines from within a chip. When test results are reported, the embedded instrumentation typically accesses an external validation/test platform through a bus. In most cases today, this access technology is usually the boundary-scan interface as defined by the IEEE 1149.1 Boundary-Scan

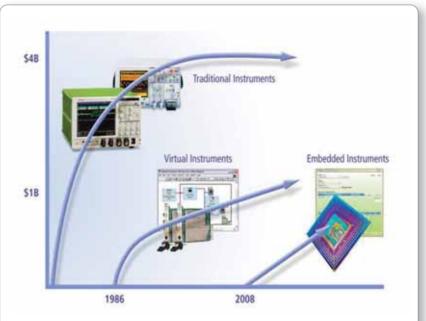

Figure 1: T&M is moving away from external probe-based instruments toward non-intrusive instruments embedded in chips and on circuit boards

Standard, also known as JTAG.

Until recently much of this embedded instrumentation was intended for a narrow task or purpose. For example, a chip vendor might decide to embed an instrument to debug the device during manufacturing and then render the instrument inaccessible to the board designer or manufacturing test engineer. Or an instrument designed into an ASIC for board test purposes might be abandoned once the board was deployed in the field where support personnel might be interested in employing it in troubleshooting applications.

Such a limited view of embedded instrumentation is changing today as the industry is realizing that it is much more effective and cost-efficient to migrate validation, test and debug routines from chips to circuit boards and eventually into systems in the field, than it is to develop new tests at each phase in the life-cycle.

The benefits of embedded instrumentations are cumulative. That is, they accrue over the entire life-cycle of a system, beginning with the initial stages of chip design and culminating in the field.

### Why is Embedded Instrumentation Needed?

Embedded instrumentation has become critically important in the industry as intrusive external or modular testers which rely on probing a device or a circuit board are losing their effectiveness. They simply can't provide the results they once did.

Software-based embedded instrumentation which tests from the inside out rather than from the outside in is much more cost-effective, efficient, agile and better suited to a wide range of today's emerging computer and communications technologies. A few examples best illustrate the increasing inadequacies of traditional external testers.

The rapidly accelerating speeds of PCI Express, Fibre Channel, 100Gb Ethernet, InfiniBand, Intel's Quick Path Interconnect (QPI) and other high-speed serial buses can wreak havoc on the accuracy of results obtained by an oscilloscope. When a scope's probe is placed on a test pad on one of these high-speed buses, the probe itself introduces capacitance anomalies onto the bus. The validation or test engineer can't tell the difference between an instrument-induced anomaly and a fault in the design or manufactured assembly. To further exacerbate the problem, semiconductor vendors are designing in signaling enhancements such as pre-conditioning, pre-emphasis and equalization to help move signals at higher frequencies. Unfortunately, these techniques make accurate measurements even more difficult for traditional instruments such as oscilloscopes and logic analyzers.

Embedded instrumentation is able to provide validation, test and diagnostic data that traditional intrusive instruments cannot. For example, Intel has developed embedded instrumentation methodology called Interconnect Built In Self Test (IBIST). Tools that make use of IBIST are able to stress and, therefore, test highspeed I/O buses well beyond the capabilities of traditional OS-based testing. In addition, at any one time, traditional measurement techniques typically only measure signal integrity margins on one or a few of the high-speed serial lanes on chip-to-chip interconnect buses on a PCB.

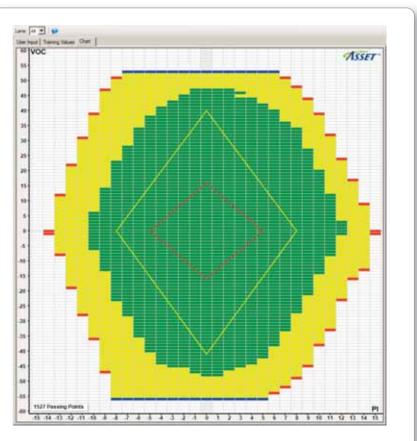

Because it is embedded into chips and onto circuit boards with those chips, IBIST can test and measure all lanes on all buses concurrently. This makes the test more robust and complete, and it drastically reduces the amount of time required to validate a system design. Validating the signal integrity of the high-speed buses on a circuit board could involve several tools, such as pattern generation and checking, bit error rate testing (BERT), and/or margining tests (see Figure 2).

In addition, sub-100 nanometer chips have demonstrated problematic parametric

Embedded instrumentation is a nonintrusive technology: instead of physically placing a probe on a PCB test-pad or a chip pin, embedded instruments are able to launch test or validation routines from within a chip

performance, including thermal conditions, timing issues, clock propagation, power distribution and others. Traditional testing techniques are coming up short at identifying these problems. External instruments at the corners of a chip cannot identify the rampant variations across the chip. Only on-chip instruments can effectively monitor parametric characteristics.

#### **Using Embedded Instrumentation**

The concept of a tools platform or a unified tool environment is most appropriate for embedded instrumentation since different tools may be needed at any given point in the life-cycle of a chip, circuit board or system. As mentioned, Intel IBIST might validate the performance of a design's high-speed buses on prototype boards prior to volume manufacturing. These IBIST tests could then be redeployed into manufacturing along with other types of tests, such as boundary-scan (JTAG) test and processorcontrolled test (PCT) in a manufacturing test strategy.

In board test applications, PCT takes advantage of the most powerful instrument on most circuit boards, the processor. PCT tests are executed when control of the processor is temporarily given over to the PCT tools. The board's CPU then reads and writes to memory and input/output (I/O) registers on the board's addressable devices. In this way, PCT exercises the

#### 16 • EMBEDDED DESIGN

functionality of the board and, as a byproduct, detects and diagnoses structural faults like opens and shorts on the traces.

PCT is an 'at speed' test technology, meaning it will detect faults which are manifested when the board is running at operational speeds. In contrast, boundary scan is a static test technology. Taken together, these two embedded instrumentation technologies provide test coverage for a broad spectrum of structural and electrical faults.

#### **Embed Your Own Instruments**

Much of the infrastructure surrounding embedded instrumentation is based on industry standards. As a result, tools vendors are not limited solely to the instruments embedded by chip vendors at manufacture. Suppliers like ASSET InterTech are adding considerable value to the entire T&M lifecycle by developing innovative applications of embedded instrumentation.

One of the foundations for embedded instrumentation is the IEEE 1149.x boundary-scan family of standards. In addition to its ability to detect, isolate and diagnose structural shorts-and-opens faults at the board level, the original IEEE 1149.1 Boundary-Scan Standard (also known as JTAG) provides non-intrusive access via a four-wire interface to instrumentation embedded in chips and on circuit boards. Developed in the 1990s and widely adopted by the industry, boundary scan serves as a robust and well understood structural test and infrastructure technology.

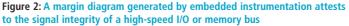

The boundary-scan family of standards has been expanded several times with new specifications that enhance and extend the original document. IEEE 1149.6 is a methodology for testing high-speed ACcoupled chip-to-chip interconnects on

Figure 4: The IEEE P1687 IJTAG standard defines the interface to embedded instruments as well as an on-chip architecture for accessing and automating their application

circuit boards. Another addition to the family, IEEE 1149.7, builds on the original specification but offers the option to reduce the footprint from four wires to two. It also

Processorcontrolled test (PCT) exercises the functionality of the board and, as a by-product, detects and diagnoses structural faults like opens and shorts on the traces

adds functional and architectural features for testing system-on-a-chip (SoC) devices and other types of chips like multi-die 3D components with vertical through-silicon vias (TSV).

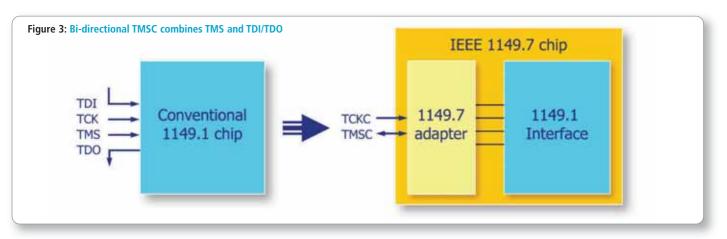

The provisions for multi-core and multi-die architectures in IEEE 1149.7 complement quite effectively the capabilities being defined in a preliminary standard under development, the IEEE P1687 Internal JTAG (IJTAG) standard. IJTAG is being developed specifically to support embedded instruments. P1687 IJTAG standardizes the interface to embedded instruments, defines an architecture for on-chip instruments and specifies many of the mechanisms for managing them.

Since embedded instrument IP (intellectual property) can come from a number of sources, such as chip suppliers, third-party providers, EDA tools or inhouse design groups, P1687 is intended as a standard way of connecting, analyzing, describing and using embedded instrumentation regardless of where the instrument has come from.

In chip test-and-debug applications, IJTAG technology (see Figure 4) embedded in various types of chips, either logic chips or field programmable gate arrays (FPGA), could automate and schedule the parallel operation of multiple embedded instruments. An embedded logic BIST engine for chip test might be operated simultaneously with a voltage monitor intended for yield analysis. The resulting simultaneous operation of these two embedded instruments could determine whether failures identified on chip-level automatic test equipment (ATE) or boardlevel tests correlate with voltage starvation.

#### Agile T&M

Deploying an IJTAG architecture and multiple embedded instruments either temporarily or permanently in an FPGA demonstrates the versatility and agility of embedded instrumentation. Such a strategy can be employed in chip test and debug, or board test applications. In fact, an entire board tester might be temporarily inserted into an FPGA to extend the test coverage of software-driven non-intrusive board test (NBT) and validation methodologies.

Designers would find this approach particularly effective for bringing up prototype circuit boards prior to a new design's transition into volume manufacturing. First prototypes often are delivered before the board's support package or FPGA's firmware have been completed. At this point, the structural, functional and performance capabilities of the prototype hardware must be tested to validate the design in preparation for software integration. Previously, functionally validating the hardware was severely limited without the board's firmware or OS in place. As a result, development schedules might be delayed while software was being completed. Now, an FPGA-based deployment of embedded instruments offers an alternative.

A network of IJTAG embedded instruments in the FPGA could function as a tester to validate, test and debug prototypes. In addition, this embedded tester might be needed later in the lifecycle of the circuit board. If so, then some or all of the embedded instruments might remain in the FPGA to perform manufacturing test, ongoing fault analysis, remote diagnostics or troubleshooting by field service.

#### **Filling Gaps**

Embedded instrumentation is indeed filling a gap that the electronics industry has had for some time. Specifically, attitudes toward validation, test and debug – the mainstays of T&M – are changing. Addressing test requirements sooner during the development of new technological advancements is a huge breakthrough, as are the vastly improved levels of validation, test and debug coverage made possible by non-intrusive software-based embedded instrumentation.

#### Quality second-user test & measurement equipment Tel: 02476 650 702 Fax: 02476 650 773 Web: www.telnet.uk.com Email: sales@telnet.uk.com

All equipment is used – with 30 days guarantee and 90 days in some cases. Add carriage and VAT to all goods. 1 Stoney Court, Hotchkiss Way, Binley Industrial Estate Coventry CV3 2RL ENGLAND

| I Stoney Gourt, Hotelikiss Wa                                     | y, Daney man |

|-------------------------------------------------------------------|--------------|

| Agilent 3458A (002) 8.5 Digit Multimeter                          | £3500        |

| Agilent 4192A L/F Impedance Analyser 5Hz-13 MHz                   | £3000        |

| Agilent 4195A 10Hz- 500MHz Spectrum An.                           | £3995        |

| Agilent 53310A Modulation Domain Analyser                         | £1000        |

| Agilent 5350B /51B/ 52B 10Hz-20GHz / 26.5GHz/ 40GHz Freq. Counter | from £1000   |

| Agilent 54540C 500 MHz- 4 Ch oscilloscope                         | £3995        |

| Agilent 54720D with 2x 54721A Plug-ins Oscilloscope 1GHz 4 ch.    | £2000        |

| Aglient 54750A High Bandwidth Digitizing Osc.                     | £1500        |

| Agilent 54845A Infinium 1.5GHz- 4 Ch Osc.                         | £4995        |

| Agilent 6574A 60V-35A Power Supply                                | £1495        |

| Agilent 81101A 50 MHz Pulse Generator                             | £3250        |

| Agilent 83630B Synthesised Sig. Gen. 26.5 GHz                     | £19500       |

| Agilent 83651B Synthesised Sig. Gen. 50 GHz                       | £13000       |

| Agilent 83752A Synth, Sweep Gen. 0.01-20 GHz                      | £9995        |

| Agilent 85046A 'S' Parameter Test Set 3 GHz                       | £2000        |

| Agilent 85047A 'S' Parameter Test Set 6 GHz                       | £3000        |

| Agilent 8508A / 85081B plug-in 1GHz Vector Voltmeter              | £2200        |

| Agilent 8510B and C Network An. 45MHz-26.5 GHz                    | from £2000   |

| Agilent 8511A Frequency Converter 45MHz-26.5GHZ                   | £2000        |

| Agilent 8515A 'S' Parameter Test Set                              | £2200        |

| Agilent 8517B 'S' Parameter Test Set 50 GHz                       | £5500        |

| Agilent 8563EC Spectrum Analyser 26,5 GHz                         | £15250       |

| Agilent 8566B 100Hz-22GHz Spectrum Analyser                       | £2750        |

| Agilent 8592B Spec. An. 9kHz-22GHz                                | £5000        |

| Agilent 8595E Spectrum Analyser with T/Gen. 9kHz- 6.5GHz          | £5000        |

| Agilent 8647A Sig. Gen. 250kHz-1GHz                               | £950         |

| Agilent 8664A (0.1-3GH) Signal Gen.                               | £2750        |

| Agilent 8648B / C Sig. Gen. 9kHz-2GHz or 3GHz                     | from £1800   |

| Agilent 8662A High Perf Sig. Gen. 10kHz-1280 MHz                  | £2000        |

| Agilent 8673B Synth Sig. Gen 2 – 26.5 GHz                         | £3750        |

| Agilent 8673D Synth. Sig. Gen. 0.05-26.5 GHz                      | £5995        |

| Agilent 8714B Network Analyser 3 GHz                              | £5500        |

| Agilent 8752A Network Analyser 300kHz-1.3 GHz High Perf.          | \$3000       |

| Agilent 8753A/B/C Spectrun Analyser 330kHz-3 or 6 GHz             | from £2000   |

| Agilent 8780A 10MHz- 3GHz Vector Signal Generator                 | £3000        |

| Agilent 8902A Measuring receiver 150kHz-1.3 GHz                  | £4995  |

|------------------------------------------------------------------|--------|

| Agilent E4420B 250kHz- 2GHz Signal Generator                     | £2000  |

| Agilent E4425B 250kHz-3 GHz Signal Generator                     | £4250  |

| Agilent E4432B - UN3- (250kHz- 3GHz)Signal Gen.                  | £2750  |

| Agilent (HP)42918 1.8 GHz R/F Impedance Analyser                 | £8000  |

| Audio Precision System One (SYS-222) Audio /Dist. Analyser       | £2200  |

| Amplifier Research 150L Power Amplifier 150W ( 10kHz-200MHz)     | £6500  |

| ENI 525LA R/F Power Amplifier 1 – 500MHz, 25 Watts               | £2500  |

| Keithley 236 Source Measurement Unit                             | £1500  |

| Keithley 237 High Voltage Source Meter                           | £2750  |

| Keithley 486 Picoammeter 5.5 digit                               | £1100  |

| Keithley 617 Programmable Electrometer                           | £1100  |

| Lecroy LC334AM 500MHz - 4 Ch Oscilloscope                        | £2750  |

| Lecroy LC564A 1GHz - 4 Channel dig. Colour Oscilloscope          | £2995  |

| Lecroy LC574AM 1 GHz, 4 Channel dig. Colour oscilloscope         | £3250  |

| Marconi 2023 Signal Generator 9kHz-1.2GHz                        | £1500  |

| Marconi 2030 10kHz - 1.35 GHz Sig. Gen.                          | £1995  |

| Marconi 2031 Signal Generator 10kHz-2.7GHz                       | £2250  |

| Marconi 2051 Signal Generator 10 kHz- 2.7 GHz                    | £5000  |

| Marconi 6203 20GHz Microwave An. Test Set                        | £6000  |

| Marconi 6204B 40 GHz Microwave An, Test Set                      | £17500 |

| Philips PM3384B 100 MHz - 4 Ch. Oscilloscope                     | £1750  |

| Rohde & Schwarz FSEB20 -B1,B4,- (9kHz- 7GHz) Spectrum Analyser   | £5995  |

| Rohde & Schwarz SME03-B%, B8, B11, B12-(5kHz-3GHz) Signal Gen.   | £2750  |

| Solartron 1250 Frequency Response Analyser                       | £2000  |

| Solartron 1253 Gain / Phase Analyser                             | £3000  |

| Tektronix AWG610 Arbitrary Function/ Waveform Generator 260MHz   | £6500  |

| Tektronix 496 Spectrum Analyser 1kHz-1.8GHz                      | £2200  |

| Tektronix 2711 Spectrum Analyser 9kHz-1.8GHz                     | £2000  |

| Tektronix 2792 Spectrum Analyser 10kHz-21GHz                     | £4000  |

| Tektronix TDS754C 500MHz - 4 channel Oscilloscope                | £2400  |

| Wayne Kerr 3260A + 3265A Precision Magnetic Analyser + Bias Unit | £4750  |

| Willtek 4403 (opt GSM, ACPM) Mobile Phone tester                 | £5750  |

| Yokogawa DL708E and DL716 Dig. Oscillopscope from                | £1500  |

## DESIGNING LOW-POWER EMBEDDED SYSTEMS

**WOJCIECH GELMUDA** AND **ANDRZEJ KOS** FROM THE AGH UNIVERSITY OF SCIENCE AND TECHNOLOGY IN POLAND LOOK AT HOW ENERGY DEBUGGING TECHNIQUES AND TOOLS CAN HELP A DEVELOPER CREATE MORE POWER-EFFICIENT BATTERY-RUN DEVICES

he consumer electronics market is flooded with different types of mobile devices and all of them have at least one thing in common – they run on batteries. But for several decades we have not seen a major breakthrough in batteries that might revolutionize the way mobile devices run, for example when they can operate for months or years without the need to recharge. Therefore, limited battery capacity-to-weight ratio is the mobile devices' bottleneck.

To overcome the insufficient battery capacity issue, new lines of low-power electronic components are being presented by manufacturers worldwide. These products have low-voltage power supplies and need less current to run. ARM, for example, offers the Cortex-M series of cores for energyefficient microcontrollers to be used in embedded devices. Still, such new electronic devices, with their low leakage currents and sophisticated sleep modes, do not entirely solve the insufficient battery capacity issue.

Most mobile devices nowadays, and in particular smartphones and tablets, employ multicore microcontrollers and many sensors. Even though most of them are energy-efficient devices, the sum of their power consumptions is usually not so low.

A low-power embedded system developer has to have extensive knowledge of existing electronic components to choose the best ones for the design to meet the proposed functionality. The battery used in the project has limits in terms of its capacity and maximum output current. With the given components and battery types there is one more thing the developer can do to prolong system working time on one battery charge and that is to write the code for the MCU that drives the whole system in a way that all the energy-saving functionality of the used components is efficiently utilized – in other words one has to use energy debugging.

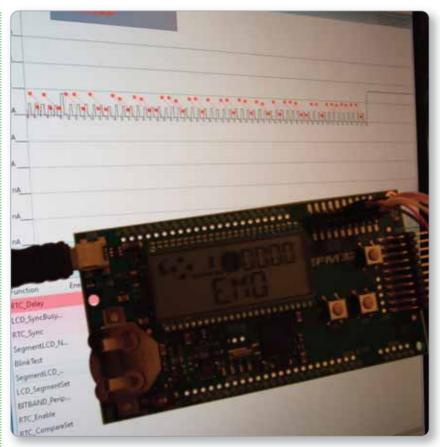

Figure 1: One of Energy Micro's Starter Kits with the energyAware Profiler software running in the background

#### **Energy Debugging**

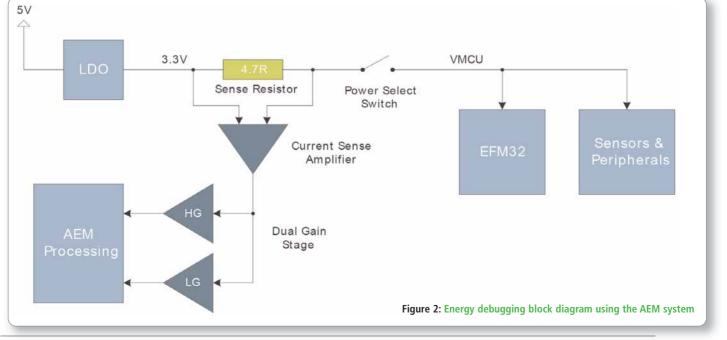

The easy way to determine the power consumption of an electronic device is to measure the voltage drop across a small resistor in series with the main DC power supply. With the known value of this resistor, the supply current can be calculated.

There are some power monitor chips available, for instance, LTC2990 from Linear Technology. Using this type of monitor is the proper approach when the system being designed does not have many different work modes – in other words, the power consumption does not change often in time – and the embedded software engineer is able to determine when a part of the system was turned on and consumed this extra current, which was measured by the power monitor.

Another example where the mentioned approach can be useful is when one wants to determine how much power the system consumes over a long period of time (for instance a day or a week) to select the right battery capacity for it. Some reduction in overall power consumption can be accomplished by employing this kind of power monitor. Nevertheless, when the system being developed implements a fast microcontroller and the current is being drawn from the battery supply in a nondeterministic way (due to the synchronous and asynchronous signals and interrupts), another approach has to be used in order to eliminate short- and long-term unnecessary power consumption. Writing and debugging a code for the microcontroller that drives the whole system has to be linked to the realtime current consumption of the system. Thus, the energy consumption has to be debugged.

#### **Developing and Analyzing the Code**

Years of working with low-power embedded systems have taught us that developing a code optimized for a specific microcontroller's current consumption is crucial. In some of our projects we used chips and tools from Energy Micro. Microcontrollers based on the ARM Cortex-M cores are suitable for our mobile applications. All of Energy Micro development boards have the J-Link debugger and Advanced Energy Monitoring (AEM) on board. The AEM tool makes it possible to gather information about current consumption from the microcontroller VMCU power domain.

Current sense amplifiers measure the voltage changes across a small resistor between the LDO output and the VMCU domain. Depending on the current At the early stages of prototyping, algorithms can be optimized and tailored for the specific system architecture to enhance their operation and, at the same time, made to consume as little power as possible

consumption range, the measurements are 1 $\mu$ A and 0.1mA for ranges below and above 250 $\mu$ A respectively. For small current consumptions up to 10 $\mu$ A the monitor can detect changes of even 100nA.

The data gathered by the AEM can be presented in real-time on a TFT display available in some of the Energy Micro kits or on a computer screen via the energyAware Profiler application provided free as part of the Simplicity Studio software.

The most helpful AEM functionality is its cooperation with the debugger. The developer can test and debug the microcontroller code and then compare the power consumption over time against the code. If a sudden power consumption peak occurs on the graph, it can be pinpointed to the specific location in the code. As such, the developer can detect what caused this increased current consumption and decide if it is normal or not, and then decide what next. The developer can analyze the code lineby-line and disable any subsystems that are not needed at certain times to preserve power. There are also labels attached to some data points in the plot. They indicate when specific, important events happened, for instance interrupts, to energy debug the system faster and more efficiently.

The energy debugging technique is important at all levels of system development. At the early stages of prototyping, when the code is written for the microcontroller on the development board, algorithms can be optimized and tailored for the specific system architecture to enhance their operation and, at the same time, made to consume as little power as possible. Next, when the code is being developed for the final system board, it is possible to energy debug the system with the use of a debug interface and by connecting the VMCU domain power supply as the main power supply of the final system board. However, the maximum current consumption of the VMCU domain is limited and it can be less than the board needs. Nevertheless, in most low-power embedded systems it is sufficient. Another approach to overcome this issue is to split the main power supply on the final board into several power domains.

#### Example

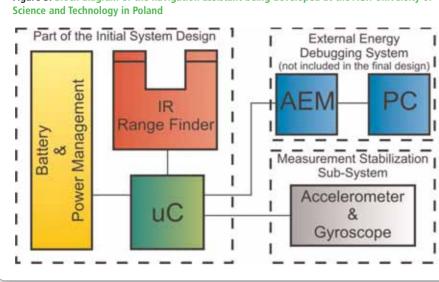

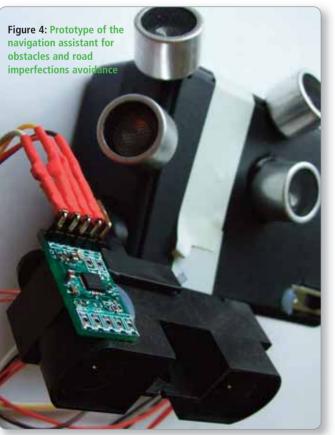

At the AGH University of Science and Technology in Poland one project deals with navigation assistants for blind people (see Figures 3 and 4). Since holes and imperfections in pavements and roads can be dangerous while navigating blind people,

Figure 3: Block diagram of the navigation assistant being developed at the AGH University of

one task was to design a device for detecting and informing the blind pedestrians of road imperfections.

The device was built based on a lowenergy microcontroller from Energy Micro with a Cortex-M3 core and an infrared range finder for scanning the area in front of the user. Since the device is mobile, the code for the microcontroller was developed to use all possible power-saving functionalities, so the battery used in the device is light and

ensures a day's operation.

The preliminary tests showed the range measurements had a large error coefficient due to the user's movements. These errors have been so great that it was impossible to detect the dangerous 5-10cm deep holes with high reliability. Thus, a stabilization subsystem had to be implemented. For that, an accelerometer and gyroscope were used.

Using adaptive filtering and integration the velocity are calculated. The analysis of the

pedestrian movement scheme showed that, based on detecting points in every step where the velocity equals zero, the algorithm for the infrared measurements stabilization could be created. Unfortunately, adding extra components to the existing system with a previouslyselected battery, DC/DC converters and LDOs, caused problems like unexpected microcontroller resets, incorrect data being read from the sensors and a noticeable reduction of working time between battery recharging. After elimination the possibility that these could be caused by faulty components, insufficient maximum output current was the obvious cause.

**Power Awareness**

Working closely with the energy debugging software

The power consumption debugging makes it possible to eliminate both software and hardware errors at the early stages of the design

and tools for the Cortex-M3 microcontroller and going over the lines of the code made detection of the sections where the output current was maxed out was both relatively easy and accurate. This also confirmed the insufficient output current assumptions.

Making changes in the code and adapting the stabilization algorithm to the system architecture made it possible to eliminate any unexpected resets and faulty data readings. The energy debugging technique also helped with better optimization of the current consumption, thus enhancing the energy-efficient functionality of the components used, which led to increasing the working time to an acceptable level.

The optimized stabilization system reduces the errors caused by the user's movement such that even 5cm holes or bumps on the road - as well as stairs - can be detected with great reliability.

Nowadays, where time-to-market is so important to all companies, electronic systems developers should not only follow news of low-energy chips but also news of energy debugging tools and software. Power consumption debugging makes it possible to eliminate both software and hardware errors at the early stages of the design.

Furthermore, when a device is already on the market and customers notice disappointingly high power consumption, maybe some of the problems can be detected with energy debugging and quickly eliminated by releasing new firmware, which is usually much cheaper than even the smallest hardware change. That is why understanding energy debugging techniques and being aware of the available tools is a must for every electronics engineer who is developing mobile and power-efficient devices.

Now available from RS Components New family of digital Multimeters from Keithley, offering a wide range of price and performance options the perfect balance of high precision and affordable cost.

FIND IT. **DESIGN IT.** BUY IT.

Find it online at: www.rs-components.com/keithley

0

## **EMBEDDED PROCESSORS GET** SMARTER AS ENERGY EFFICIENCY **TAKES CENTRE STAGE**

**JO STEIN HAUGEN.** APPLICATION ENGINEER AT ENERGY MICRO. GIVES A PRACTICAL GUIDE TO TACKLING ENERGY **EFFICIENCY IN DESIGN** THROUGH SELECTING THE RIGHT MCU

> nergy efficiency is increasingly being recognised as a key performance attribute of many electronic systems and in particular of

embedded designs. In products ranging from smart meters to wireless sensor nodes and from mobile health monitors to intruder alarms, designers need to take every step possible to limit energy consumption.

The detailed operational and design requirements of such applications may vary, but they share a common feature: they need to operate reliably over a period of years or even decades, using the limited energy resources available from batteries or an energy harvesting system. At the heart of designers' efforts to achieve this are a new generation of microcontrollers (MCUs) specifically designed with energy efficiency in mind.

It is worth considering in more detail the scale of the design challenge involved. Many of these microcontrollers must deliver real-time (or close to realtime) performance throughout a service life that is spent predominantly in a lowpower sleep mode that inherently reduces their speed of response to external events. A device such as a smart

for many years on a single battery

meter will often be buried or otherwise difficult to access, requiring 10 to 20 years of operation on a single battery.

As a result, energy budgets in such applications are aggressively trimmed. Given the current state of battery technology, it is not unusual to see an energy requirement for the lifetime average current draw to be between 5µA and 20µA. If a system designer budgets 20% of the available battery capacity for data collection and 'housekeeping'

functions, 20% for receiving commands and 30% for transmitting data, then the remaining 30% must support the system's idle mode. This may sound generous, but the meter will likely spend in excess of 99% of its life in some kind of sleep state, whose efficiency becomes absolutely crucial in reaching the design targets.

This is why sleep modes are one of the most important features of a low-power MCU.

#### The Factors that Make a 'Good' Energy-Saving MCU

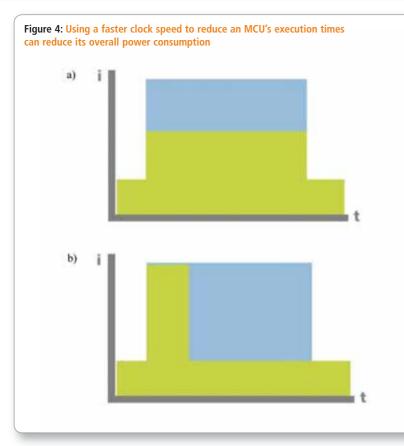

In the past there has been a somewhat casual assumption that because of their lower active power consumption, 8- or 16bit solutions must be the best choice for low-energy applications. But the fact is that a modern 32-bit CPU core like the ARM Cortex-M3 delivers a processing power of 1.25DMIPS/MHz; that is, it can perform a given task in around one quarter of the time required by older 16-bit CPU cores.

Since energy is 'power times time', using the 32-bit Cortex-M3 in preference to a less powerful alternative can prove more energy efficient, particularly if the designer opts for an MCU such as Energy Micro's Tiny Gecko, that even in active mode consumes only  $150\mu$ A/MHz.

So 'low power' does not necessarily mean 'low energy'.

As observed, an energy efficient processor stands and falls on its sleep modes and the designer's ability to choose the right mode of operation for the job. In a power-constrained application, subsystems such as displays and RF and PHY-layer transceivers will be designed to spend only as much time as necessary in their active state, MCU functions will therefore represent the only "low-hanging fruit" for power optimisation.

Most modern MCUs have more than one low-power mode (these will typically be something like "Sleep/Standby", "Deep-Sleep" and "Off"). The specific CPU, memory and I/O functionality available will vary from microcontroller to microcontroller, but the general principles involved remain the same.

Although it may appear to make sense to use the deepest possible sleep mode in every case, there is in fact a trade-off involved, the deeper the sleep, the longer the wake-up overhead. The overhead consists of hysteresis and propagation delays in the wake-up circuitry, start-up and stabilisation of the power supply and re-starting the CPU clock. The device then needs to restore its registers and other internal configurations, before doing the same for system memory. Only when these processes are completed can the MCU service the event that triggered the wake-up process.

This trade-off has two implications: first, if the MCU is in an overly deep-sleep mode, it may not be able to wake up in time to deal with an external event; second, during A smart meter will likely spend in excess of 99% of its life in some kind of sleep state, whose efficiency becomes absolutely crucial in reaching the design targets; this is why sleep modes are one of the most important features of a low-power MCU

the wake-up phase the device doesn't do any useful work. So waking too frequently from a deep sleep mode in order to perform a small amount of processing could conceivably burn more power than staying an a "higher" activity state with less time wasted on the wake-up process.

#### **Dealing with Events**

If there is a need to deal with unpredictable events it is much more difficult to reduce power consumption than for scheduled events such as real-time clock interrupts, or the time-slotted communications processes common in ZigBee and other mesh protocols, that require the processor to check for messages from other network nodes at a certain time.

Unfortunately, most applications involve events of the less predictable type and require the MCU to respond in real time or almost real-time. Examples include threshold/alarm conditions, power interruptions and wireless protocols that can transmit and receive at random intervals. In such situations, failure to wake within an appropriate timeframe may mean losing critical data or failing to respond to a user command. In the worst case, there may be a risk of system damage if an alarm condition is not dealt with in a timely fashion.

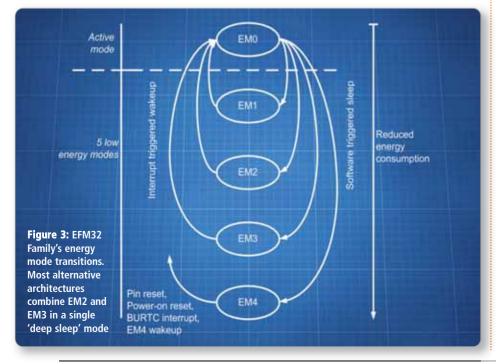

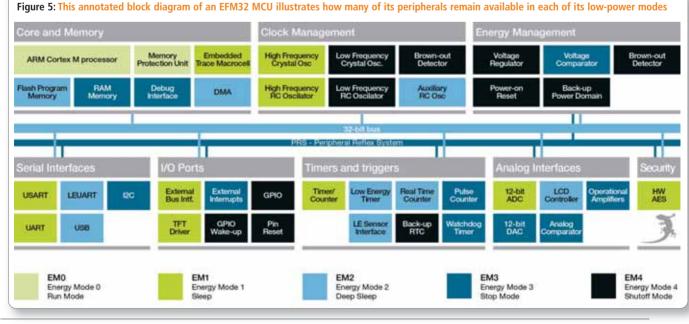

The task for the designer, therefore, is to find the lowest-power sleep mode that provides adequate response to anticipated (if unscheduled) events. Energy Micro's EFM32 Gecko family of energy-optimized 32-bit MCUs provides a good example of the options available. Although the Gecko architecture is optimized to perform beyond the basic requirements of each mode, most MCUs used for these types of applications have similar operating states and characteristics (Figure 3).

At the lowest level, most MCUs have a mode designated as "off" or shut-down mode, that preserves the minimum functionality needed to trigger wake-up from an external stimulus: in our example of the Gecko series this is designated EM4. In this mode, the entire device is powered down, other than the interrupt monitoring circuitry on the reset pin and GPIO pin wake up. The EFM32 draws around 20nA of current in this mode, although a typical 32-bit MCU would require nearer 1.5µA.

Restarting from such an "off" mode is essentially a device reset, a process that for the EFM32 takes around 160µs. Main memory contents will have been lost and

www.electronicsworld.co.uk

must be re-loaded. Some processors include a small (512 byte in the case of the EFM32) block of memory whose content is preserved for use on start-up.

A kind of 'mezzanine' state above EM4 preserves a few more critical functions, in particular the real-time clock and 512 bytes of backup memory. Drawing only 400nA, this state would consume the capacity of a pair of AA cells in roughly seven years. Although intended primarily for use in the event of power supply failure, it can be an excellent alternative when RTC and a faster wake-up time are desirable.

With more functionality still, 'stop' mode (EM3 in Figure 3) enables a limited degree of autonomous peripheral activity and faster wake-up. Here, the high- and low-frequency oscillators are disabled, but the MCU's full RAM and configuration register states are preserved. In addition to the elements active in EM4, the poweron reset and brown-out detector are active, and the CPU can be woken up by an asynchronous external interrupt or via a number of internal sources, such as the device's analogue comparators (ACMP) and pulse counter (PCNT).

For a designer, the key specifications to note in this mode are the time to wake up – which should be of the order of a few microseconds – and the absolute power consumption (10 to  $30\mu$ A for a typical MCU, 590nA for a best-in-class device such as the EFM32). Perhaps the most important point for the designer to remember is that some MCUs do not include full Waking up too frequently from a deep sleep mode in order to perform a small amount of processing could conceivably burn more power than staying an a "higher" activity state with less time wasted on the wake-up process

internal memory retention in this mode.

Deep sleep mode (EM2 in Figure 3) leaves all of the MCU's critical elements active, while disabling high frequency system clocks and other non-essential loads. In addition to the EM3 functionality, the 32kHz oscillator used to clock on-chip peripherals remains active. This allows selected low-energy functions including the RTC, watchdog timer and some external interfaces to remain active.

As in EM3, the designer needs to take care, since not every MCU series provides full register and RAM retention. Choosing a device with this capability allows the device to return to active state and resume program execution quickly. Bestin-class figures for current draw in this mode can be as low as 900nA (with RTC running from a precise clock source), with

time to return to active mode of as little as  $2\mu s$ .

Finally, in sleep/standby mode (EM1), the MCU's pointer and configuration register states are fully preserved, eliminating the need to save them on power-down and restore them on powerup. This typically saves hundreds to thousands of instruction cycles for each wake-up. The high-frequency oscillator remains active with the CPU clock tree disconnected, allowing the device to resume execution on the next clock cycle after a wake-up event. High-frequency peripherals - for instance direct memory access (DMA), analogue/digital and digital/analogue converters (ADC/DAC) and hardware encryption - remain active.

Sleep mode current draw ranges from  $45\mu$ A/MHz to  $200\mu$ A/MHz, depending on the choice of MCU.

#### **Selecting an MCU**

The process of selecting an MCU and the correct mode of operation for the application is relatively straightforward once these typical sleep mode specifications are understood. The designer first needs to list all of the alert. alarm and interrupt conditions within the application, and identify the one that requires the fastest response. For instance, in a logistics application, a device may perform both GPS-based location reporting and shock and vibration monitoring. The first has a wake-up tolerance that is measured in seconds; but when the MCU's accelerometer inputs exceed pre-set threshold levels, the device will need to wake up and start measuring and recording within a millisecond or less.

The second step is to quantify the exact wake-up time from each sleep mode in the application that is required. This includes not just the time taken to return to a ready state, but also the time needed to execute the code that services the event in question. Executing an interrupt service routine, for instance, will take longer than jumping straight to a block of code dedicated to the specific event.

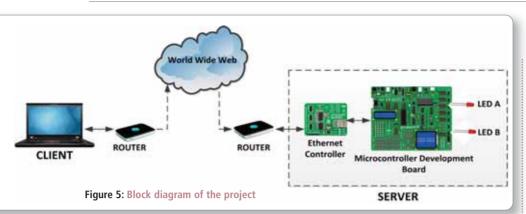

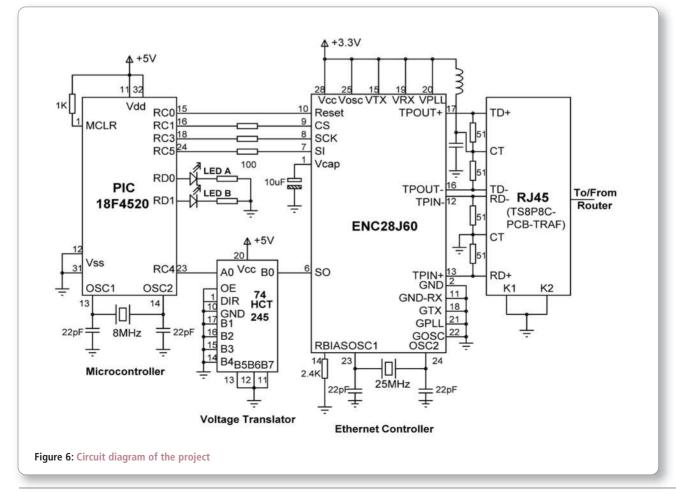

Comparing the maximum tolerable delays with the minimum attainable service time figures will identify the appropriate sleep mode.