August 2015 Volume 121 Issue 1952 £5.20

# Electronics WORLD

THE ESSENTIAL ELECTRONICS ENGINEERING MAGAZINE

Precision

Amplifiers

Enable High

Performance

Current

Sensing

### **EMBEDDED DESIGN**

### **SPECIAL REPORT:**

- Progammable logic

- IoT wireless connectivity

- SOC design

Technology

The robot – your next

best friend

$0.0015\Omega$

Smart Apps Formula 1 in your pocket

PRESOLUTION

9

NEW Series LTE design

# THE WORLD'S LARGEST SELECTION .ABLE FOR IMMEDIATE SHIPMENT! $^{\circ}$

**OPEN ACCOUNTS AVAILABLE FOR QUALIFYING CUSTOMERS**

LIVE **WEB CHAT** 24/7, 365 DAYS PER YEAR

FREE **SHIPPING ON ORDERS** OVER £50\*

**PRICES ARE IN BRITISH POUND** STERLING AND **INCLUDE DUTIES**

# \_OCAL SALES & AVAILABLE

0800 587 0991 • 0800 904 7786

1,000,000+ PRODUCTS IN STOCK | 650+ INDUSTRY-LEADING SUPPLIERS | 3.9 MILLION PARTS ONLINE

\*A shipping charge of £12.00 will be billed on all orders of less than £50.00. All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in British pound sterling and include duties. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2015 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

Cover supplied by **LINEAR TECHNOLOGY** More on pages 11-13

#### **REGULARS**

05 **TREND**

> KEEPING UP WITH THE FAST PACE OF CHANGE IN AUTOMOTIVE ELECTRONICS

06 **TECHNOLOGY**

08 **RASPBERRY PI COLUMN**

14 LTE COLUMN

16 **EMBEDDED USER INTERFACE DESIGN ON A BUDGET**

by Lucio Di Jasio

20 THE TROUBLE WITH RF...

IDLE STATE

by Myk Dormer

**37 INDUSTRY ANNOUNCEMENTS**

**PRODUCTS**

#### **FEATURES**

30

32

38

22 **EMBEDDED AND APPLICATION DEVELOPERS -LEARNING FROM EACH OTHER**

By Greg Law, founder and CEO, Undo Software

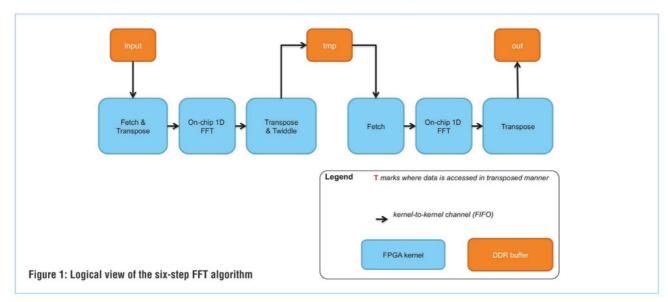

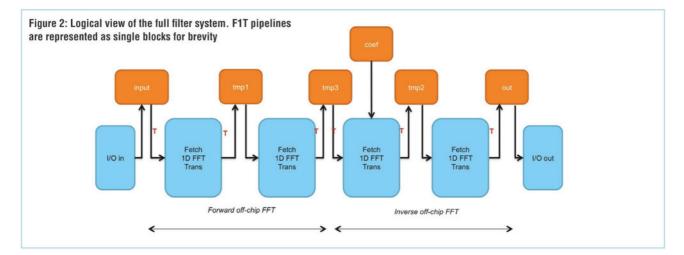

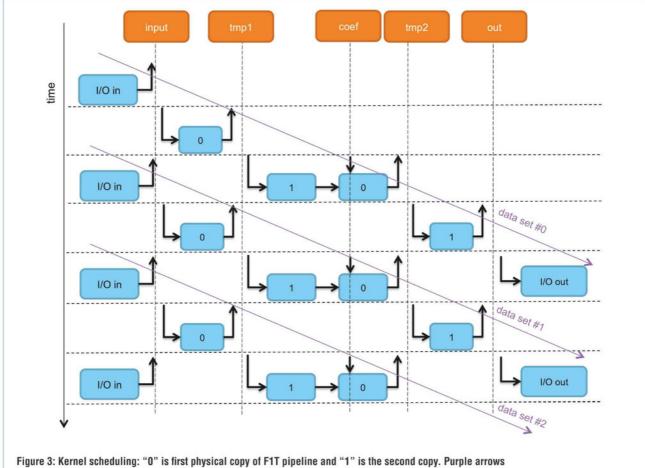

26 SYSTEM DESIGN EXPLORATION WITH OPENCL **FOR FPGAS**

> Dmitry Denisenko and Mykhailo Popryaga describe the design of a two-million point frequency domain filter using Altera's OpenCL software development kit for FPGAs

**OPTIONS FOR PROVIDING IOT WIRELESS** CONNECTIVITY

By Rui Ramalho, Product Manager for connectivity modules at Murata Europe

TIME TO TAKE THE HEAT OUT OF LEDS

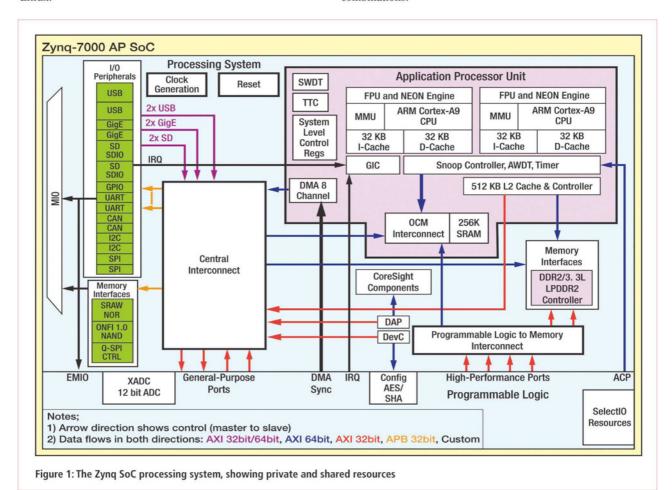

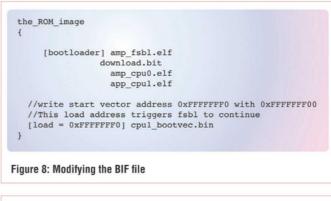

Using ARM A9 cores on a Xilinx's Zynq system-on-a-chip can significantly increase the performance of a system, writes Adam P. Taylor, Chief Engineer for electrical systems at e2v

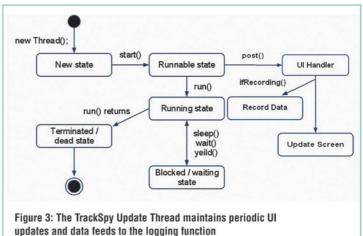

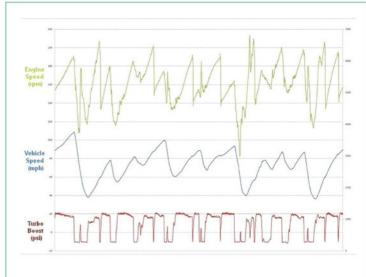

**FORMULA 1 IN YOUR POCKET: TELEMETRY FOR EVERYONE?**

By Tony Dewhurst, TrackSpy Development Lead

Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry - particularly as regards electric shock, fire hazards and explosions.

# **Switching for Every Application**

## Because in Electronic Test, One Platform Does Not Fit All!

Pickering offers the largest range of switching products and platforms for all automated electronic Test & Measurement applications:

- The most switching choices in PXI, LXI and PCI formats

- Switching from low level DC to 1kV and RF/Microwave to 65GHz

- Pickering is the only switching vendor with eBIRST™ Switching System Test Tools, which quickly and accurately locate switching system faults in all of their switching platforms. Visit pickeringtest.com/ebirst to learn more.

Pickering support all of their products with a standard three year warranty.

For more information scan this QR Code or go to pickeringtest.com/advantage

Switching | Instrumentation | Programmable Resistors | Custom Design | Cables & Connectors

## KEEPING UP WITH THE FAST PACE OF CHANGE IN AUTOMOTIVE ELECTRONICS

The automotive sector has long pushed the boundaries in electronic design, pioneering applications that make their way into other industries over time. Considering the vast changes taking place in the automotive industry right now, the automotive electronics market is collectively in the middle of one of the most exciting times for decades: electric vehicles, collision avoidance systems, alternative fuel sources, driverless cars... the list goes on.

The automotive industry has some good reasons for this pace of change: the need to be competitive in a marketplace where differentiation is hard; demand for reduced production costs; faster time-to-market; the rigours of industry compliance such as with ISO 26262; and, of course, increasingly discerning consumers who expect more for their money. So it is no surprise that we are seeing automotive electronic systems that until a few years ago would have been reserved purely for the highest premium brands, with processing power found only in "super computers".

In turn, all these changes and demands put pressure on the electronics design team, which is why more companies are re-evaluating their tools and processes to ensure they are fit for purpose and able to keep up with the ever-evolving environment. Companies that are not reviewing their systems will be left behind by those modernising to enable the latest development best practice.

Agile development is not new and has become far more widespread than purely for software development. As organisations have awakened to this new way of working, where iterations and releases happen faster, they have realised the benefits of flexibility in their plans, enabling better alignment with their business needs. Similarly, continuous integration (CI) has gained popularity, involving building and testing embedded software products on a more regular basis, and if something doesn't work properly fixing it earlier and more cheaply.

A natural evolution from this is continuous delivery (CD) that, according to Evans Data research carried out in the first half of 2014, was then being adopted by over 60% of organisations surveyed in the UK and the US.

CD involves delivering products as soon as they are releasable, with the intent of getting early customer feedback to influence the next iteration. These shorter cycles enhance the alignment between development and customer, increase competitiveness and reduce risk by making small changes frequently. Such an incremental approach to development can apply across all elements of a project, not just code and other software components, but encompassing any asset in a project, for instance CAD material, web content, marketing documentation and other data associated with bringing a project to market.

Some might not consider cars to be objects that lend themselves to continuous delivery. Although it's true that for many physical components, various prototyping and manufacturing steps enforce delays or manual steps between developers and customers, the CD approach can still be adopted if delivery into the QA or pre-production stages is considered to be a "release".

TREND • 05

These new methodologies may have a great deal to offer, but it does not necessarily follow that the legacy systems and tools will support them. Many automotive design and programming teams are using big, heavy and inflexible tools that began life as general manufacturing systems more suitable for numerically-controlled cutters than modern software development. Tools that haven't had a major change in the past five years are probably not going to be flexible enough, or sufficiently up-to-date, to cope with today's electronic software design environments. For example, the theories behind both agile and CD depend on transparency and visibility across all aspects of a project, from previous versions through to the current working model. This means that a single repository or 'source of truth' for all assets, not just software source code, is essential, with the added bonus of simplifying compliance management and reducing software maintenance costs.

Automation is also a major tenet of CD (and also of DevOps, which readers may have heard of in the context of more mainstream software development environments). Manual and repetitive tasks have the potential for error to creep in, and modern automation tools for software builds, testing and release management reduce these risks. A good example is the automation of compliance testing and simulators, which helps reduce the need for physical prototypes until the last possible moment, hence reducing cost and potential wasted time.

At the heart of many agile and CD projects sit version control systems, also known as version management. Traditional software developers may know them from back in the day as source code or SCM (software configuration management) systems, but the modern generation of these tools is designed to support every single asset within a project, if necessary across non-technical environments too. In fact, Perforce's own research a couple of years ago found that many of its users deploy version control for tasks other than managing software development.

One of the challenges of the automotive sector is the wide range of software that needs support: embedded software, hardware software, mobile apps, simulation models, web services and communications. Plus, designers work with a wide range of platforms, such as Java and .Net, and a variety of different development tools. As end products will be in the marketplace for some years, they need to be supported, including incremental feature releases, not just new developments.

#### By Mark Warren, Perforce Software (www.perforce.com)

#### EDITOR: Svetlana Josifovska

Tel: +44 (0)1732 883392 Email: svetlanaj@sjpbusinessmedia.com

SALES: James Magnani

Tel: +44 (0)20 7933 8976 Email: jamesm@sjpbusinessmedia.com

DESIGN: Tania King PUBLISHER: Justyn Gidley ISSN: 1365-4675

PRINTER: Buxton Press Ltd

#### SUBSCRIPTIONS:

Subscription rates: 1 year: £62 (UK); £89 (worldwide) Tel/Fax +44 (0)1635 879361/868594 Email: electronicsworld@circdata.com

business media

2nd Floor,

52-54 Gracechurch Street.

London, EC3A 0EH

Follow us on Twitter @electrowo

Join us on LinkedIn

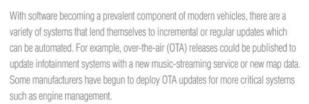

# NEW FD-SOI PROGRAM HELPS DESIGNERS CREATE LOW-POWER APPLICATIONS

Grenoble-based CEA-Leti has been joined by seven partners in support of its new FD-SOI (fully depleted silicon on insulator) IC development program, called Silicon Impulse. The initiative aims to provide a comprehensive technology platform for IC design, advanced intellectual property (IP) creation, emulation and test services, along with industrial multi-project wafer (MPW) shuttles.

The partners include CEI-Leti, CEI-List,

STMicroelectronics, Dolphin Integration, CMP,

Mentor Graphics, Cortus and Presto Engineering,

who will combine their expertise and facilities for

one-stop-shop services to speed development of

energy-efficient products for ultra-low-power (ULP)

Internet of Things (IoT), energy-efficient computing

systems, and robust and reliable applications for harsh

environments. The partners are also in discussion with

Synopsys to join the program.

"Leti has always concentrated on research that helps our partners adopt technology to become more competitive in their markets," said Marie-Noëlle Semeria, CEO of Leti.

With the program's flexible format, Silicon Impulse's involvement can be limited to consulting or extended to developing and delivering the whole system, or anything in between. It can help innovators with their projects from concept through production hand-off. Companies can receive advice and have their products shaped from a very high level, including

FD-SOI

Fully Depleted Silicon On Insulator, or FD-SOI, is a planar process technology that relies on two primary innovations

First, an ultra-thin layer of insulator, called the buried oxide, is positioned on top of the base silicon. Then, a very thin silicon film implements the transistor channel. Thanks to its thinness, there is no need to dope the channel, thus making the transistor fully depleted.

ultra-thin body and buried oxide Fully Depleted SOI" or UTBB-FD-S

FD-SOI enables much better transistor electrostatic characteristics versus conventional bulk technology. In addition, the buried oxide layer lowers the parasitic capacitance between source and drain and efficiently confines the electrons flowing from source to drain, dramatically reducing performance-degrading leakage currents.

a feasibility study and recommendations on how to implement the system. Leti and its partners can also provide unique IP and/or technology components such as foundation IP or more complex system-level IP blocks, RF, NVM, N/MEMS, 3D components and any other advanced technology to shape a unique and advanced, yet manufacturable, product. At another level, Leti and List can provide embedded software to complete the whole product.

MPW shuttles are offered to open the doors to a wider set of users and projects, enabling innovators to

test their ideas, especially mixed-signal, analog or RF technologies or any new IP that would require silicon validation in FD-SOI. This also provides an affordable platform for startups and other small companies to build their prototypes and run small volumes until they receive financing and/ or demonstrate market traction to build their own mask set.

The first 28nm FD-SOI MPW is planned for February 2016 to be processed at STMicroelectronics's site in Crolles, near Grenoble.

# THE WORLD'S FIRST EMOTIONS-READING PERSONAL ROBOT GOES ON SALE IN JAPAN

The world's first personal robot which reads emotions, named Pepper, went on sale in Japan in June. Some 1.000 units were available for

purchase immediately, with followup shipments scheduled from July onwards.

Pepper not only reads emotions, it has been created to have emotions, enabled by functions developed by cocoro SB. These emotion functions have been modelled on the release of hormones in humans in response to stimuli to the five senses, which in turn generate emotions.

Pepper's emotions are generated autonomously following processing of information from its cameras, touch sensors, accelerometers and other sensors within its "endocrine-type multi-layer neural network" Its emotions are influenced by people's

facial expressions and words, as well as its surroundings, which in turn affect its words and actions. For example, Pepper is at ease when it is around people it knows, happy when praised and scared when the lights go off.

Depending on the emotion at the time, Pepper raises or lowers its voice, sighs, exclaims, cries, and so on. Pepper's emotions can be seen on the heart display, which shows different colours and movements.

SoftBank, the company behind Pepper, plans to expand the lineup of robots and apps including a dedicated model for businesses, called 'Pepper for Biz'.

Call: 01844 204420

Email: sales@ecopacpower.co.uk

Website: ecopacpower.co.uk

THIS SERIES PRESENTS THE RASPBERRY PI SINGLE-BOARD COMPUTER, ITS FEATURES AND BENEFITS, AND ITS USE IN VARIOUS PROJECTS

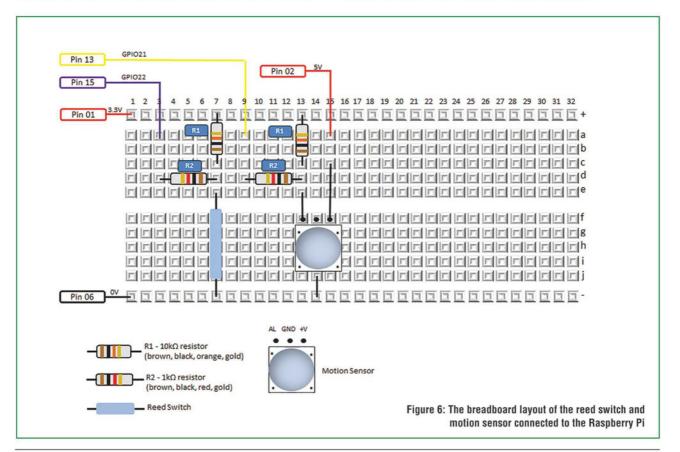

## Creating A Motion Sensor and Door Switch With The Raspberry Pi

#### BY ANDREW ROBSON AND MIKE COOK

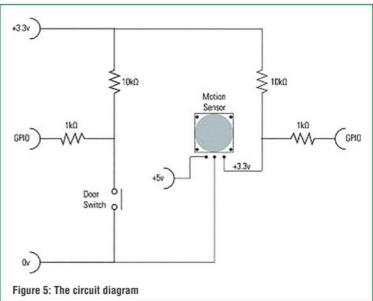

n our first home-automation project we will create a motion sensor and door switch.

Motion sensors and door switches allow us not only to create alarms or alerts, but also to monitor flow and movement throughout a home. Using the information created by these sensors, you can apply rules and actions using Python. For example, you can turn off

a light in a room if motion is not detected for a length of time, or receive an e-mail alert if your garage door is open for a period of time. So by combining sensors, rules and actions, you can create a more intelligent home environment.

A door switch contains a reed switch (see Figure 1), triggered when the two pieces come apart. One piece is attached to the door and the other to the door frame. One half contains a magnet and the other a reed switch held closed when the magnet is near. When the two come apart the magnetic field loses its strength and the switch is broken. When the door is closed, current flows through the switch, and when the door is open the current is broken. This type of switch is called normally open.

The motion sensor, sometimes known as a passive infrared (PIR) sensor (see Figure 2), is packaged with an integrated circuit and a lens that will focus the moving objects for the sensor. Both sensors interact with the Raspberry Pi through the GPIO port in the same manner, which makes their software identical.

You will need to write a Python script to monitor the sensors and produce an action when either sensor is triggered. In this

Figure 1: Door switch

Figure 2: Motion sensor

tutorial you will learn to trigger a message to the screen, but also take any number of other actions as explained before.

#### **Project Parts**

The following parts are needed for this project:

- 1 x door switch; easily obtained from a home security outlet or online.

- 1 x motion sensor; usually 5-12V with three terminals, +V<sub>E</sub>,

GND and 3.3V Pi-friendly output.

- 2 x 10kΩ resistors: brown, black, red, gold.

- 2 x 1kΩ resistors: brown, black, orange, gold.

- 1 x solderless breadboard; a prototyping board to which parts and wires can be connected by clipping them on to the board. It is used for prototyping electronics without having to solder parts together.

- Jumper wires: three male-to-male for breadboard connections, five male-to-female for connecting the breadboard to the GPIO pins. Jumper wires usually come in packs of various quantities, colours and sizes. Although only eight are needed for this project, having 20-30 of each are sufficient for most projects. Any size will do for this project, but shorter male-to-male (10cm) and longer maleto-female (20cm) are best.

#### Construction

The Raspberry Pi's GPIO ports are used to interface with the sensors, configured for input or output. In this case we will use them for input as data is collected from an external sensor.

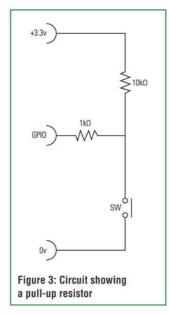

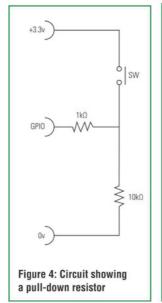

A GPIO port can have three different states: high (positive), low (ground) or floating (either). To accurately set the state of the GPIO pin, tie it either to positive or negative (ground), by using a pull-up or pull-down resistor. When the GPIO is connected to a positive terminal, the GPIO pin's value is high; when connected to ground it is low.

Figure 3 shows a 10k $\Omega$  pull-up resistor that connects the GPIO to the positive terminal when the switch is open.

However, when the switch closes, there is a lower resistance path to ground and the GPIO will go low.

Figure 4 shows a pull-down resistor (10k $\Omega$ ) connecting the GPIO pin to ground, making it low. When the switch is pressed there is a lower resistance to positive, which changes the GPIO state to high. The 1k $\Omega$  resistor is there to

protect the GPIO pin from a short circuit when the switch is pressed.

#### Tip

Always double-check the wiring before powering on the Raspberry Pi, as it can be very easily damaged by not

protecting the GPIO pins with resistors. Be especially careful of the 5V pins, which if connected to a GPIO pin will cause permanent damage.

In your project you want a closed circuit (low state) when the door is closed or when there is no motion, and a high state when the door is opened or motion is detected, so a pull-up resistor is needed to set the GPIO high in an alarm state – see the circuit diagram in Figure 3.

The PIR sensor has three coloured wires for ground, positive and alarm. The colours and pin positions may differ, depending on which model you have, so be sure to check its data sheet. The alarm pin is open-collector, meaning it requires pull-up resistor.

#### Software

The software will print to screen whenever motion is detected or the door sensor is triggered. Ideally, print to screen only once per event, and use variables (motion and door) to keep track of when the system is in alarm state and so prevent the trigger reccurring for the same event. If logging these events to a database, or taking another action such as switching on a light or sending an e-mail alert, this method prevents multiple actions being created for the same event. The code is provided in Listing 1. •

#!/usr/bin/env python

Home Automation using motion detection For the Raspberry Pi

import RPi.GPIO as GPIO import time GPIO.setmode(GPIO.BOARD) GPIO.setup(13, GPIO.IN) GPIO.setup(15, GPIO.IN) def main(): motion = False door = False

if GPIO.input(13):

if motion == False: print "Motion Detected"

motion = True

while True:

else:

motion = False

if GPIO.input(15):

if door == False: print "Door Opened"

door = True

else:

door = False

time.sleep(.3)

if \_\_name\_\_ == "\_\_main\_\_":

main()

Listing 1: Home automation with motion detection

#### RASPBERRY PI PROJECTS

Raspberry Pi represents a new generation of computers that encourage the user to play and to learn and this book is aimed at the beginner Raspberry Pi user who is eager to get started creating real-world projects.

Containing 16 practical projects, this fun and informative resource introduces readers to the skills required in order to make the most of the Pi.

Raspberry Pi Projects will be

available in paperback and e-book priced £14.99.

We have several copies of this book to give away. To register your interest, write to the Editor at svetlanaj@

Raspberry Pi

Projects

Andrew Robinson

Mike Cook

Mike Cook

Willey

The standard Communication and Co

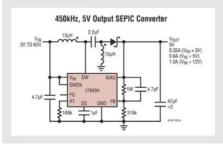

## PRECISION AMPLIFIERS ENABLE HIGH PERFORMANCE CURRENT SENSING

By Greg Zimmer, Senior Product Marketing Engineer, Signal Conditioning, Linear Technology Corporation

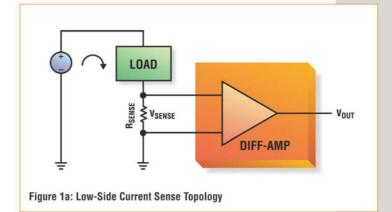

ost analog ICs (comparators, op-amps, instrumentation amplifiers, references, filters, etc) are designed to handle voltage signals. When it comes to handling current signals, designers are left with a lot fewer options and a lot more headaches. That's unfortunate, since there can be a big advantage to directly

monitoring and measuring current. Motor torque, solenoid force, LED intensity, solar cell exposure and battery power can be monitored best by looking at the current flow. What's needed is a circuit that can precisely sense current and convert this current into a voltage so it can be amplified, conditioned and measured by the readily available voltage devices (amplifiers, comparators, ADCs, etc). Although a resistor can translate current to voltage, a resistor by itself does not provide a complete solution. The most common solution is to use a sense resistor, placed directly in series with the current, and an amplifier to isolate and condition the voltage across this resistor (V<sub>SENSE</sub>).

#### **COMBINING AN AMPLIFIER & A SENSE RESISTOR**

At first glance, placing a resistor in series with a ground contact may seem like the most straightforward current sensing approach. This technique, known as low-side current sensing (Figure 1a), requires that no ground paths exist that could allow current to be diverted around the

sense resistor or that could contribute current from an adjacent circuit. If a mechanical frame establishes the system ground, it may be impractical to insert this sense resistor. Also, since grounds are not perfect conductors, ground voltage can vary at different points in the system, necessitating the use of a differential amplifier for precision measurements (Figure 1b).

There is a more serious problem when implementing low-side current sensing. A resistor in the ground path means that the "ground" of the load will change as the current changes. This can induce common mode errors in the system and presents a problem for interfacing to other systems requiring the same ground potential. Since measurement resolution is enhanced by the magnitude of V<sub>SENSE</sub>, the designer must trade-off "ground noise" for increased resolution. A modest full-scale V<sub>SENSE</sub> of

100mV translates to 100mV of injected ground noise. The problem of ground variation can be avoided by placing the current sense resistor between the power supply and the load.

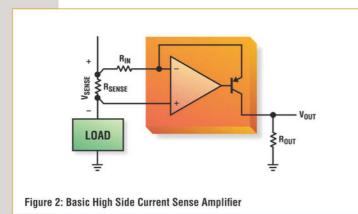

This alternative approach is referred to as high-side current sensing. Again, the differential voltage across the sense resistor provides a direct measurement of current, however, now there is a non-zero common mode voltage across the resistor. This configuration presents the technical challenge that a small differential sense voltage must be discerned from the common mode voltage of the power supply (Figure 2).

51 LOAD 0.1µF LOAD Load Out Ground 100mV/A LTC2053  $0.0015\Omega \leq V_{SENSE}$ of Load 10k Current Local Ground 0.1µF **Parasitic** Chassis Resistance  $150\Omega$ True Ground Figure 1b: Low-Side Current Sense Circuit Implemented

For low voltage systems, an instrumentation amplifier or other rail-to-rail differential amplifier may suffice for monitoring a high-side sense resistor. The output of the amplifier must then be translated to ground without adding significant error. When the supply voltage is very high, circuitry may be required to translate  $V_{\text{SENSE}}$  down to the input common mode range of the amplifier or to float the amplifier up to the supply voltage. Aside from the added board space and cost, these techniques assume that the common mode voltage will stay within a narrow, specified range. For most current sense applications, it's very useful to anticipate large common mode fluctuations. For example, if the current sense circuit can operate when the power supply voltage drops, it can indicate if there is a problem at the supply or at the load; excessive current

suggests current limiting and load faults, and insufficient current indicates power supply failure. On the other hand, current sense circuits may face common mode voltages that exceed the supply voltage. Many current-devices, such as motors and solenoids, are inductive by nature; rapid current changes through them will cause inductive flyback, leading to large voltage swings across the sense resistor. It is precisely in these instances when the amplifier can be most useful.

#### SIMPLE SOLUTION

To address the challenges of current sensing, high-side current sense amplifiers were created. These special amplifiers are designed to extract a small differential voltage, generated by current passing through a small sense resistor, from a high common mode voltage. The sense voltage is then amplified and translated into a ground-referenced signal. Figure 2 illustrates the basic topology of a high side current sense amplifier. In this case, the amplifier forces a voltage across R<sub>18</sub> that is equivalent to  $V_{SENSE}$ . The current through  $R_{IN}$  is then forced through R<sub>OUT</sub>, providing a ground referenced output voltage. For this basic capability, it is clear that high-side current sense amplifiers should have high input impedance, high gain with good gain accuracy, and a wide common mode range with good common mode rejection. What may not be as clear is the importance of

the amplifier's precision.

### FOCUS ON THE RESISTANCE Ideally, the task of current an

Ideally, the task of current and voltage sensing should not impact the load to which it's connected. This means that voltage sense devices should have nearly infinite input impedance; this ensures that no appreciable current can be diverted from the load. Conversely, a current sense device should have nearly zero input impedance; this ensures that the voltage to the load is not significantly reduced. High-side current sense circuits (amplifier + resistor) are subject to both of these requirements. The amplifier used to sense the voltage across R<sub>SENSE</sub> must have high input impedance. The resistor used to sense the current to the load must be very

To fully appreciate this, let's consider the use of a large sense resistor. As the series resistance is increased, the voltage

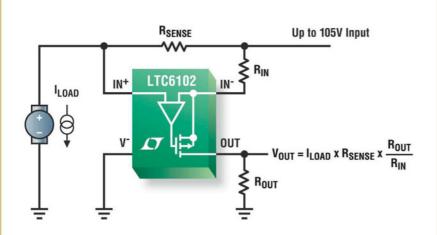

Figure 3: Linear Technology's LTC6102 provides a straightforward implementation of high-side current sensing. An  $R_{\text{SENSE}}$  and two gain resistors configure the part. The designer can customize power consumption, response time and the input/output impedance characteristics by their selection of  $R_{\text{IN}}$  and  $R_{\text{out}}$ .

available to the load is reduced. Extra series resistance is a source of wasted energy; large sense resistors can lead to excessive heat dissipation, with potential long-term reliability concerns.

Is there any reason to use a large sense resistor? The primary advantage is to increase the over-all output voltage (EQ1). This can be useful when the amplifier has fixed gain or limited gain configurability.

There is a limit to the size of the sense resistor. The input range of the amplifier and the maximum expected current will determine the largest practical sense resistance (EQ2).

$$R_{SENSE\ MAX} = (V_{SENSE\ MAX} / I_{SENSE\ MAX})$$

[EQ2]

As an example, if 50mA is the maximum expected current through the sense resistor ( $I_{\text{SENSE\_MAX}}$ ) and the high side current sense amplifier can accept inputs up to 250mV ( $V_{\text{SENSE\_MAX}}$ ), the maximum sense resistance is 50hms (R<sub>SENSE MAX</sub>).

Ideally, the designer should not be forced to add sense resistance to compensate for the amplifier. As long as the amplifier can operate with sufficient gain and gain accuracy, the designer should instead focus on the minimum acceptable sense resistance. This can be calculated from the current sense amplifier's input offset voltage and the smallest current that must be resolved:

$$R_{\text{SENSE MIN}} = (V_{\text{OFFSET}} / I_{\text{RES}}).$$

[EQ3]

As an example, if 1mA resolution is required (IRES) and the offset voltage of the high-side current sense amplifier is 1mV ( $V_{\mbox{\scriptsize OFFSET}}$ ), the minimum sense resistance is 10hm ( $R_{\text{SENSE\_MIN}}$ ). Equation 3 highlights a key point: the minimum sense resistance is directly related to the offset of the high side current sense amplifier.

#### TAKING A CLOSER LOOK AT A MODERN CURRENT SENSE **AMPLIFIER**

With high-side current sensing in mind, precision highside current sense amplifiers offer dramatic improvements in performance over previous generations. For example, Linear Technology's LTC6102 is a new high-side current sense amplifier that incorporates zero-drift technology.

This amplifier has an input offset voltage of only 10µV and an offset drift of 50nV/°C Max. Compared to previous generations of current sense amplifiers, the LTC6102 can use a significantly smaller sense resistor. If the system can tolerate a large  $V_{\scriptscriptstyle SENSE}$ , the LTC6102 can accept sense voltages up to 2V. The combined offset plus this maximum sense voltage provides over 106dB of dynamic range, allowing the LTC6102 to resolve microamps from amps of current. Sensing very small current

To address the challenges of current sensing, high-side current sense

is possible since any gain can be selected with external resistors. The gain accuracy can be better than 99% by using precision resistors.

The LTC6102 does not compromise on other important current sense features, either. The high impedance inputs limit the input bias current to less than 300pA. The LTC6102 can operate with an input common mode voltage up to 105V. The common mode rejection of 130dB contributes less than 32µV of offset error across a full 100V of input common mode voltage range. For fault protection, the LTC6102 has a tusec response time, allowing it to quickly initiate a power shutdown in the event of unexpected load or supply changes.

#### CONCLUSION

Precision high-side current sense amplifiers offer inherent benefits for monitoring and controlling current. Advancing technologies in battery management and motor control, to name a few examples, are creating a significant demand for current sense amplifiers with higher common mode voltages, higher accuracy, and better precision. Leading the way, the LTC6102 breaks new ground with an impressive set of features and outstanding precision characteristics. High-side current sense amplifiers have now achieved the performance levels of industry leading precision op-amps, giving designers a simple, versatile and highly accurate alternative to the lower precision or more complicated current sense circuits of the past.

For more information about current sensing, Linear Technology has compiled the  $\mathbf{I}_{\text{SENSE}}$  Application Note, an extensive collection of current sense circuits. Download it now at www.linear.com/currentsense

Linear Technology (UK) Ltd • Tel: 01628 477066 Email: uksales@linear.com • www.linear.com

apid mobile data growth requires the wireless industry to use more sophisticated, higher-capacity access technologies like LTE. While supporting many advanced antenna techniques, LTE needs precise containment of the radio frequency (RF) signals used to transmit mobile data. Network operators

increasingly need high-performance antennas to meet these performance metrics.

With the many antenna techniques LTE supports – and the often highly different antenna design requirements, as well as different network applications – it can be challenging to select the best antenna to fit a given scenario.

Constructing high-performance wireless networks is like building a pyramid, wherein the lower layers of precisely-cut stones support the above layers and any inconsistency can seriously harm the entire structure.

In wireless network optimization, the bottom stones are the physical layer, which is the network equipment that delivers the RF coverage. Operators need to build and optimize the physical layer to set a solid foundation on which they can add layers for

PHYSICAL LAYER REPATH

COVERAGE DESIGN

ANTENNA PATTERNS

parameter optimization, radio resource management and other advanced features.

The RF coverage layer must be finely sculpted for LTE networks to run optimally. The upper layers will not reach their full potential without that well-sculpted, finely-calibrated foundation. A poorly sculpted base can lead to reduced throughput that diminishes the quality of service for subscribers. Operators must deliver strong RF signal strength in the desired coverage areas with sharp attenuation of that signal outside each area.

Deciding which basestation antenna to use is a critical decision for achieving finely-sculpted RF patterns. Antenna technology advances including MIMO (multiple input multiple output), beamforming and the use of various transmission modes plus RF path architecture changes complicate that decision. The addition of more frequency bands for LTE has forced an increase in the number of antenna ports, and antenna sizes have grown as more capabilities are integrated. All these changes impact antenna performance and selection.

For example, MIMO technology, or spatial multiplexing, increases throughput by transmitting distinct data streams over different signal paths using the same resources in both frequency and time. MIMO requires a high signal-to-interference-plus-noise ratio (SINR) and low correlation of each path. The signal de-correlation is a result of the antennas (polarization or spatial diversity) and the environment (rich scattering).

There are several types of MIMO: single-user MIMO (SU-MIMO), multi-user MIMO (MU-MIMO), open loop and closed loop MIMO and massive MIMO. The various types of MIMO are a function of which LTE transmission mode is selected.

SU-MIMO requires multiple antennas at both ends of the link to spatially multiplex channels serving a single user. SU-MIMO is most often used on the downlink as there are antenna and power limits to device designs. MU-MIMO combines multiple spatially "de-correlated" users onto the same resources. MU-MIMO does not increase peak user throughput, but it does increase average user throughput

and sector capacity. Both uplink and downlink MU-MIMO are possible. Massive MIMO uses a two-dimensional array of closely-spaced antennas, MU-MIMO with tens of devices, and is expected to possibly use an active antenna system (AAS).

The addition of more frequency bands for LTE has forced an increase in the number of antenna ports, and antenna capabilities are integrated

Beamformers use an

array of antenna elements individually phased in such a way as to form beams (or nulls) in a desired direction. Typical beamforming antennas have highly-correlated, closelyspaced elements and columns. Passive antennas can support horizontal beamforming. An AAS integrates the active transceiver array and the passive antenna array into the same

radome, and supports two-dimensional (azimuth) and 3D (both azimuth and tilt) antenna array configurations.

Operators must choose antennas based on the techniques most advantageous to their network design and needs. Operators with frequencies below 1GHz are most likely to use a singlecolumn cross-polarized antenna due to size limitations inherent with leasing and zoning (typically less than or equal to 610mm wide x 1830mm high), while antennas serving the 1-2GHz range are typically limited today to no more than two cross-polarized columns. Size constraints likewise limit 2.5GHz four-column (eight-port) antennas to a column spacing ≤ 0.65λ (0.65 wavelengths), which can give sub-optimal uplink performance compared to 1λ, but serves the downlink well.

Ray Butler is Vice President of Wireless Network Engineering at CommScope.

This column is an edited extract from CommScope's new eBook, 'LTE Best Practices'. Over the next few months different authors of this eBook will contribute articles to this section.

#### SPECIAL OFFERS for full sales list check our website

#### www.stewart-of-reading.co.uk Check out our website, 1,000's of items in stock

Used Equipment - GUARANTEED All items supplied as tested in our Lab Prices plus Carriage and VAT

| IFR 2025                     | Signal Generator 9kHz - 2.51GHZ Opt 04/11                                              | £1,250         |

|------------------------------|----------------------------------------------------------------------------------------|----------------|

| Fluke/Philips PM3092         | Oscilloscope 2+2 Channel 200MHZ Delay etc                                              | £295           |

| HP34401A                     | Digital Multimeter 6.5 digit                                                           | £325           |

| Agilent E4407B               | Spectrum Analyser 100HZ - 26.5GHZ                                                      | £5,000         |

| HP3325A                      | Synthesised Function Generator                                                         | £195           |

| HP3561A                      | Dynamic Signal Analyser                                                                | £650           |

| HP3581A                      | Wave Analyser 15HZ - 50KHZ                                                             | £250           |

| HP3585B                      | Spectrum Analyser 20HZ - 40MHZ                                                         | £1,500         |

| HP53131A                     | Universal Counter 3GHZ                                                                 | £600           |

| HP5361B                      | Pulse/Microwave Counter 26.5GHZ                                                        | £1,250         |

| HP54600B                     | Oscilloscope 100MHZ 20MS/S                                                             | from £12       |

| HP54615B                     | Oscilloscope 2 Channel 500MHZ 1GS/S                                                    | £650           |

| HP6032A                      | PSU 0-60V 0-50A 1000W                                                                  | £750           |

| HP6622A                      | PSU 0-20V 4A Twice or 0-50V 2A Twice                                                   | £350           |

| HP6624A                      | PSU 4 Outputs                                                                          | £350           |

| HP6632B                      | PSU 0-20V 0-5A                                                                         | £195           |

| HP6644A                      | PSU 0-60V 3.5A                                                                         | £400           |

| HP6654A                      | PSU 0-60V 0-9A                                                                         | £500           |

| HP8341A                      | Synthesised Sweep Generator 10MHZ-20GHZ                                                | £2,000         |

| HP83731A                     | Synthesised Signal Generator 1-20GHZ                                                   | £2,500         |

| HP8484A                      | Power Sensor 0.01-18GHZ 3nW-10uW                                                       | £125           |

| HP8560A                      | Spectrum Analyser Synthesised 50HZ - 2.9GHZ                                            | £1,950         |

| HP8560E                      | Spectrum Analyser Synthesised 30HZ - 2.9GHZ                                            | £2,400         |

| HP8563A                      | Spectrum Analyser Synthesised 9KHZ-22GHZ                                               | £2,750         |

| HP8566B                      | Spectrum Analsyer 100HZ-22GHZ                                                          | £1,600         |

| HP8662A                      | RF Generator 10KHZ - 1280MHZ                                                           | £1,000         |

| HP8970B<br>HP33120A          | Noise Figure Meter                                                                     | £750           |

| Marconi 2022E                | Function Generator 100 microHZ-15MHZ - no moulding handle                              | £295<br>£325   |

| Marconi 2022E                | Synthesised AM/FM Signal Generator 10KHZ-1.01GHZ                                       |                |

| Marconi 2024<br>Marconi 2030 | Synthesised Signal Generator 9KHZ-2.4GHZ<br>Synthesised Signal Generator 10KHZ-1.35GHZ | £800<br>£750   |

| Marconi 2305                 |                                                                                        | £750<br>£250   |

| Marconi 2440                 | Modulation Meter<br>Counter 20GHZ                                                      | £295           |

| Marconi 2945                 | Communications Test Set Various Options                                                | £2.500         |

| Marconi 2955                 | Radio Communications Test Set                                                          | £595           |

| Marconi 2955A                | Radio Communications Test Set                                                          | £595           |

| Marconi 2955B                | Radio Communications Test Set                                                          | £850           |

| Marconi 6200                 | Microwave Test Set                                                                     | £1.950         |

| Marconi 6200A                | Microwave Test Set 10MHZ-20GHZ                                                         | £2,500         |

| Marconi 6200B                | Microwave Test Set Town 2-2001 2                                                       | £3,000         |

| IFR 6204B                    | Microwave Test Set 40GHZ                                                               | £10,000        |

| Marconi 6210                 | Reflection Analyser for 6200 Test Sets                                                 | £1,250         |

| Marconi 6960B with           | 6910 Power Meter                                                                       | £1,250<br>£295 |

| Marconi TF2167               | RF Amplifier 50KHZ - 80MHZ 10W                                                         | £75            |

| Tektronix TDS3012            | Oscilloscope 2 Channel 100MHZ 1.25GS/S                                                 | 2800           |

| Tektronix 2430A Tektronix 2465B R&S APN62 R&S DPSP R&S SMR40 Cirrus CL254 Farnell AP60/50 Farnell B30/10 Farnell B30/10 Farnell B30/20 Farnell LF1 Racal 1991 Racal 2101 Racal 9300 Black Star Orion Black Star Or | Oscilloscope Dual Trace 150MHZ 100MS/S Oscilloscope 4 Channel 400MHZ Syn Function Generator 1HZ-260KHZ RF Step Attenuator 139dB Signal Generator 10MHZ - 40GHZ with Options Sound Level Meter with Calibrator PSU 0-60V 0-50A 1KW Switch Mode PSU 0-60V 0-50A 1KW Switch Mode PSU 0-60V 0-50A 1KW Switch Mode PSU 30V 10A Variable No Meters PSU 30V 20A Variable No Meters PSU 30V 20A Variable No Meters PSU 0-35V 0-2A Twice Digital Sine/sq Oscillator 10HZ-1MHZ Counter/Timer 160MHZ 9 Digit Counter/Timer 160MHZ 9 Digit Counter Timer 160MHZ 9 Digit Counter Timer 1.3GHZ Test Set Scopemeter 2 Channel 50MHZ 25MS/S Scopemeter 2 Channel 100MHZ 5GS/S TV Gen Multi Outputs Sine/sq Oscillator 10HZ-100KHZ Low Distortion Oscillator Dual Trace 15MHZ Synthesised Signal Generator 10MHZ-20GHZ Wow & Flutter Meter TV Signal Generator Multi Outputs Timer Counter Analyser 20GHZ PAT Tester 6 1/2 Digit DMM True RMS IEEE as 7150 plus Temp Measurement DMM 7 1/2 Digit Gain Phase Analyser 1mHZ-20KHZ PSU 0-35V 0-2A 2 Meters PSU 0-30V 0-2A Digital Function Generator 0.002-2MHZ TTL etc Kenwood Badged Synthesised Function Generator 2 Channel 50MHZ | \$350<br>\$600<br>\$225<br>\$300<br>\$13,000<br>\$40<br>\$2195<br>\$500<br>\$45<br>\$75<br>\$45<br>\$295<br>\$45<br>\$75<br>\$230<br>\$85<br>\$250<br>\$275<br>\$125<br>\$600<br>\$60<br>\$25<br>\$25<br>\$25<br>\$25<br>\$25<br>\$25<br>\$25<br>\$25<br>\$25<br>\$25 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### STEWART OF READING

17A King Street, Mortimer, Near Reading, RG7 3RS Telephone: 0118 933 1111 • Fax: 0118 933 2375 9am - 5pm, Monday - Friday Please check availability before ordering or CALLING IN

# **Graphic Object Layer**

**LUCIO DI JASIO**, ELECTRONICS ENGINEER AND TECHNICAL AUTHOR, PRESENTS THIS SERIES ON EMBEDDED USER-INTERFACE DESIGN ON A BUDGET

n the previous seven instalments of this column, we analysed all the parts of the Mikromedia board. For each of them we found out which module of the Microchip Library for Applications (MLA) was available and how it could be configured to match the Mikromedia specific interfaces. By now you would have realised this mostly involves adding

a few lines to the HardwareProfile.h file and eventually commenting or uncommenting a few lines in selected config files to enable/disable optional features. But in the development of user interfaces (UI) for true embedded applications, these building blocks can only take us so far. To develop large and complex interfaces with a professional look and feel we need to learn to use a more powerful (second) layer of abstraction – enter the graphic object layer (GOL).

#### Of Objects And Widgets

Sitting on top of the graphics primitives, the touch interface and graphics resources (fonts and images), we find the MLA GOL module, where we finally meet for the first time the "widgets" – the graphical components we have all grown to recognize as the essence of all graphical user interfaces (GUIs).

The name of this library, however, can be a bit misleading: does it

mean we need to use an object-oriented programming language; is C++ now a requirement; and so on?

I am happy to report it is not – at least not with the MLA GOL library! An object-oriented design methodology is not a function of the language we use. The GOL library is, in fact, written entirely in C language and compatible with the MPLAB XC compiler suite.

This means that we can design a GUI for a 16-bit microcontroller (PIC24, dsPIC33) and quickly recompile it for a 32-bit model (to be used on a PIC32 Mikromedia) or even for an 8-bit microcontroller (on a PIC18 Mikromedia).

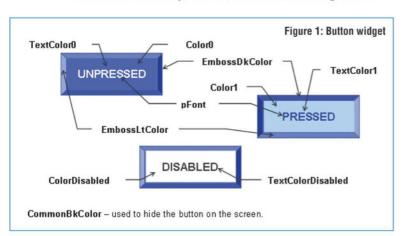

In perfect object-oriented style, the GOL library requires us to create objects (widgets) by defining their type, position and a number of additional attributes using a simple BtnCreate() function (see Listing 1).

Listing 1: Example of a button widget

There are similar xxxCreate() functions for all possible types of widgets (there were 21 at last count), all taking a similar list of arguments.

Then we talk to the widgets, and they communicate with each other by exchanging messages, which are simple, standardized, data structures that carry information about an event and optional parameters (see Listing 2).

typedef struct { BYTE type; BYTE uiEvent; SHORT param1; SHORT parama; } GOL MSG;

#### Listing 2: A message data structure

User touch inputs are a great example of such messages. The connection between the touchscreen module and the GOL, for example, is achieved by a single function, TouchGetMessage(), that checks for the last touch event (coordinates) and packs them inside a message data structure (see Listing 3 below).

```

void TouchGetMsg(GOL_MSG *pMsg)

static SHORT prevX = -1;

static SHORT prevY = -1;

SHORT x, y;

x = TouchGetX();

y = TouchGetY();

pMsg->type = TYPE_TOUCHSCREEN;

if ((x!=-1) & (y!=-1))

{// Pressed

pMsg->uiEvent = EVENT_PRESS;

}

```

Listing 3: Snippet of the TouchGetMsg() function

#### Figure 2: Screenshot of the GDDX user interface

#### Page Layout

If we organize the GUI in pages, similar to mobile applications, there is simply too little room to subdivide the screen further into smaller windows, so each page is completely defined by an active widgets list. The GOL main loop is constantly scrolling down the active widgets list and passing around messages (response). Each widget can decide to act upon selected messages and/or send messages back. Each widget knows its position on the screen and is ready to paint itself (!) when asked to do so by receiving a paint message.

There are entire books devoted to teaching the art of optimal layout of the graphical elements on a page, so we definitely won't delve into the subject here, except to point out how tedious the work can quickly become, because for each widget on each page we have to specify the absolute position; see the second row of parameters: left, top, bottom, right, passed to the BtnCreate() function in Listing 1.

#### **GDD X Comes To The Rescue**

As we have seen previously (you will remember the graphic resource converter, or GRC), the MLA developers have created a handy tool, the Graphic Display Designer (GDD), to help us prototype and rapidly develop GOL user interfaces without spending hours "counting pixels"; see Figure 2.

As was the case of the GRC, the tool is written in Java and therefore works across all platforms (Windows, Linux and OS X) but also, in the most recent incarnation it can be installed directly as a plugin inside MPLAB X (hence the new name GDD X).

Not only the manual layout of widgets and the definition of multiple pages is simplified, but the tool attempts also to automate the definition of the events (and the messages produced) to connect widgets according to the application logic. This requires a little more explaining.

#### I Will Call You Back

To keep the overall application design simple and modular, rather then defining actions as separate functions for each widget, the GOL library groups all activity in two "loops", the message passing loop and the drawing loop. The message passing loop does exactly what you'd expect, taking each event/message generated by the application and passing it to each widget in the active list (page). A number of automatic actions/reactions are predetermined (built in) for each widget type. If you send a touch press event with a pair of coordinates that correspond exactly to the location of a button on the screen, for example, it will trigger that button to change state. The drawing loop, then, is where each widget is asked to redraw itself (if necessary) to produce the required visual feedback. In the example of the button being pressed, this will force the button

widget to redraw itself to look "pressed".

On top of such automatic behaviours, though, it is up to the user to inject additional application specific logic. For example, we might want to associate moving a slider on the screen Sitting on top of the graphics primitives, the touch interface and graphics resources (fonts and images), we find the MLA GOL module

to a corresponding change of intensity of the display backlight. To allow this, a special user defined function (callback) is called inside each loop: GOLMsgCallback() and GOLDrawCallback() respectively.

```

WORD GOLMsgCallback( WORD objMsg, OBJ_HEADER* pObj, GOL_MSG* pMsg) {

if( pObj->ID == 1) // intercept messages from the slider {

// update the screen backlight

BacklightSet( SldGetPos( pObj));

}

```

Listing 4: GOLMsgCallback() example

The example in Listing 4 shows how to intercept a message coming from a slider widget (recognized by its specific ID assigned at creation) and then change the display backlighting based on the position of the slider.

Similarly, by intercepting the drawing loop using the GOLDrawCallback() function we can define custom graphic effects that go beyond the normal expected behaviour of the stock widgets.

#### The Heap

While playing with dynamic memory allocation in an embedded application can be a bad idea, it must be noted that the GOL library makes very judicious use of memory and, in fact, there is very little dynamic involved too. It is just a matter of flexibility and convenience. The library does not require allocating global buffers of pre-computed size for the widgets we will use, so it does it for us using the standard

C heap management library. It is then entirely up to us to "manage" the memory, attempting to free and re-use chunks of it as we move from page to page in our application, or we rather prefer to keep things in place (so to speak) to avoid the hassle and the complications that derive from it.

In any case, we have to reserve a sufficient amount of (RAM) memory for Heap use by entering it in the MPLAB XC linker (XC16-ld) project options. GDDX does compute automatically the sum of all the memory required for the application, making this step simple and guess-free.

#### **Accelerate The Applications**

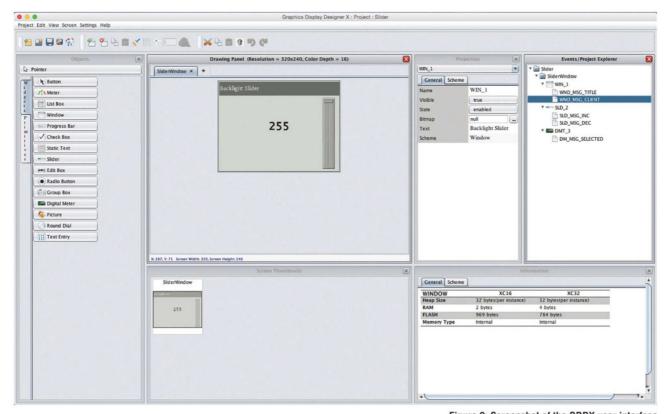

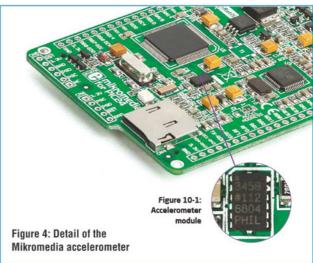

There is one last peripheral module of the Mikromedia board that we have not yet discussed: the accelerometer. This is an ADXL345 device connected via I2C interface in each of the Mikromedia boards;

it can be considered just another user input sensor to integrate in the application interface.

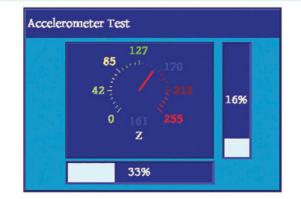

Figure 5 shows a demo application representing the Z axis sensor output using a 'round dial' widget, and the X and Y axes using two 'progress bar' widgets.

Now the true fun begins, as you dig deeper into these libraries and start applying this knowledge to other boards and designs of your own creation.

Figure 5: The ADXL345 accelerometer user interface

#### **USER INTERFACE DESIGN FOR EMBEDDED APPLICATIONS**

Lucio Di Jasio is EMEA **Business Development** Manager at Microchip Technology. He has held various technical and marketing jobs in the company's 8, 16 and 32-bit divisions for the past 18 years.

Lucio has published several books on

programming for embedded control applications, and we have three copies of his book 'Graphics, Touch, Sound and USB, User Interface Design for Embedded Applications' to give away at the

If you want to win this book, please send an email to svetlanaj@sjpbusinessmedia.com, mentioning the title in the heading.

Tel. 01298 70012 www.peakelec.co.uk sales@peakelec.co.uk

Atlas House, 2 Kiln Lane Harpur Hill Business Park **Buxton, Derbyshire** SK17 9JL, UK

Follow us on twitter for tips, tricks and news

For insured UK delivery: Please add £3.00 inc VAT to the whole order. Check online or give us a call for overseas pricing.

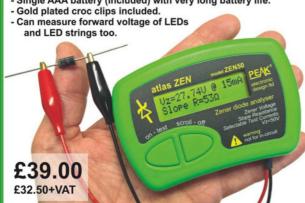

## ZEN50

#### Zener Diode Analyser (inc. LEDs, TVSs etc)

#### Brand new product!

Introducing the new Atlas ZEN (model ZEN50) for testing Zeners (including Avalanche diodes) and many other components.

- Measure Zener Voltage (from 0.00 up to 50.00V!)

- Measure Slope Resistance.

- Selectable test current: 2mA, 5mA, 10mA and 15mA.

- Very low duty cycle to minimise temperature rise.

- Continuous measurements.

- Single AAA battery (included) with very long battery life.

@peakatlas

#### SOT23 Test Adapter for Multimeters and Peak Analysers

#### Brand new product!

Designed to look like a giant SOT23 device, this beautiful adapter allows you to easily connect surface mount diodes, Zeners, MOSFETs and transistors.

Just place your device into the controlled-force clamshell and connect your probes to the gold plated test

Great for connecting crocs, hookprobes and multimeter prods.

DCA Pro

"A very capable analyser" The famous

Exciting new generation of semiconductor identifier and analyser. The DCA Pro features a new graphics display showing you detailed component schematics. Built-in USB offers amazing PC based features too such as curve tracing and detailed analysis in Excel. PC software supplied on a USB

Flash Drive, Includes Alkaline AAA battery and comprehensive user guide.

**NEW LOW PRICE!** £105.00 £87.50+VAT

It's only possible to show summary specifications here. Please ask if you'd like detailed data. Further information is also available on our website. Product price refunded if you're not happy

## **Idle State**

#### BY MYK DORMER

"G

reen design means ultra-low power". Could I have crammed any more popular buzzwords into one short sentence?

For good or ill, the ultimate power consumption of our products is fast becoming one of the most important factors in their overall design, for reasons as abstract as "ecological goodness" or

as practical as the inconvenience and/or expense of battery replenishment in portable devices.

Unfortunately, along with the desire for lower power comes the desire for more functionality. More processing power, more functions and, in the low-power radio arena, higher transmit power, better receiver performance and greater data throughput. More sophisticated technology helps to some degree. Smaller chip geometries promise improved "megahertz per milliamp" figures, and new display types reduce wasted power there – but receiver large-signal performance needs current in the front-end stages, and a transmitted watt of power is still a watt, and no power amplifier will exceed 100% efficiency.

In low-power radio design the upshot of this is that much, or even most, of the critical circuitry in a battery-powered or otherwise power-critical design is duty-cycled on and off to reduce the average current (once conventional design has minimised the peak value), a technique pioneered by the paging industry. Frequently, this duty cycle can be a fraction of 1% or less, and can reduce a peak radio current of several hundred milliamps to no more than a few tens of microamps, average.

This is a very well understood technique, used in a wide variety applications – including the mobile phone, but it still harbours an interesting trap for the unwary: In designing a low duty cycle system it is necessary to control the cycle rate by means of some piece of hardware that is always "on". This is usually a low-frequency oscillator of some type, driving either a hardware digital counter or the "interrupt out of sleep" function of the device's main processor. Common alternatives include RC oscillators internal to the processor, or in timing-critical applications, a low frequency 'watch' crystal, combined with a CMOS oscillator.

Unless the design is very simplistic and powers down all the circuitry in the off state, then there will be a situation where

the controlling hardware is powered (even if most of it is in some form of sleep mode) and significant parts of the rest of the circuit is either powered down or in standby.

Now, these standby modes ("chip select false") are very useful, but often either do not reduce the current drain sufficiently or actually (internally) the standby is a 'power off', which switches off significant parts of the interface circuitry.

That leaves us with the most absolute case: the highcurrent circuitry, such as a radio module, an LCD display or a complex signal processing chip, that has its power supply rail switched off (disconnected) when "off". It would seem that, when the actual power rail is absent (by means of an inline switch device, or the shutdown of a dedicated regulator), there could be no possible difficulty – which is where the trap lies!

Consider the likely circuit configuration. The powered

The design must be deliberately arranged so that the powered section of the unit never presents a voltage to an input or an output of the unpowered part, although this is easier said than done

controlling device (probably not the main processor) not only controls the rail switching but also has one or more control or signal lines feeding across the powered/unpowered barrier. If conventional design methodologies have been followed, there is

a very good chance that some of those lines will be "active low"; for example: chip select pins are often active low and "UART output" serial ports likewise idle in their mark (high) state.

This can be a disaster. Active low signals idle at a (logic) high voltage. The outputs of the unpowered circuitry will no longer be able to present this idle state to the inputs of the controlling circuit, causing the potential for spurious activations, serial UART framing/over-run errors and so on.

If there are pull-ups on the powered side, or if the lines are outputs from that section, then things can be worse: the voltage present on the (innocent, inactive) output will be present on the input pin of the unpowered circuit. In the best case this can just result in wasted current flowing but more likely will cause the substrate diodes in the unpowered circuit's logic inputs to conduct, allowing unexpected parts of the circuit to power up, latch up, or possibly fail to initialise properly when "properly" powered up in the operating cycle. In some cases, I have seen entire integrated circuits powered up through leakage current flowing into just one input. At this point wasted current is the least of your worries.

The cure is as obvious as it is draconian. The design must be deliberately arranged so the powered section of the unit never presents a voltage to an input or (by direct logic drive or via a pull-up) an output of the unpowered part, although this is easier said than done.

Where the option exists to define the state of the control or data lines, such as, for example, where a data port is being handled in software between two processors, then it is necessary to ensure that all the idle states are low – data ports set to zero before power-off, and all control signals and strobes defined as active high.

If the unpowered circuit's input is unavoidably active low,

then add an open collector (or drain) buffer, or ensure that the driving output in the powered side of the circuit is switched to a high-impedance ("tri-state") condition before powering off. In either case a pull-up is necessary to the switched power rail on the unpowered side.

Lastly, if the unpowered circuit presents an output to the powered circuit that usually idles in a high state (like a UART output), then a high-value pull-down is needed to avoid an undefined logic state on the input, and the powered circuit input will either need to be programmed to ignore the apparent spurious state during power-off, or it can be isolated with a CMOS switch or a logic (OR) gate.

This is, I admit, an elementary mistake to run into, but sometimes it's those very simple issues that complicate much more complex jobs, if they are not spotted in time.

Even after thirty years on the bench, I have still caught myself missing this a time or two in the recent past. Hopefully, now you won't.

Myk Dormer is a Senior RF Design Engineer at Radiometrix Ltd www.radiometrix.com

# EMBEDDED AND APPLICATION DEVELOPERS — LEARNING FROM EACH OTHER

BY **GREG LAW**, FOUNDER AND CEO, UNDO SOFTWARE

vidence of software's growing importance is everywhere: from industrial devices to those in the home, products and processes increasingly rely on software for controlling operations and introducing new features to differentiate them from the competition. This trend is having a major impact on software development, with embedded systems now combining traditional device-level software with application code. The graphical user interface (GUI) on a smart TV is a perfect example – previously it would have been more basic, and now its look and usability are key selling points in a competitive market.

#### The Evolution Of Consumer Electronics

Another good example of how things have changed is the way we listen to music. The original Sony Walkman of 1979, which played cassette tapes, was purely mechanical, with no software involved. As it evolved, an LCD was added to it, requiring an 8- or 16-bit embedded microcontroller, with code running on the bare metal of the

with code running on the bare metal of the device.

Next, as functionality and complexity of music devices increased, an embedded real-time operating system (RTOS) was required to manage drivers, schedulers and sensors. Most software was still system-level rather than application code, but the balance was beginning to shift.

Fast-forward to the iPod Touch and the device is running a full-blown operating system that manages memory, scheduling, user interfaces and application code. When we get to the iPhone, the roles of embedded and application code have swapped around completely from the early iPods. The OS takes up the minority of code on the device; most is application code, which also drives the touchscreen-based user experience.

Essentially, in 20 years the picture has changed around completely – and not just in consumer electronics. Previously hardware focused devices, from uninterruptible power supplies to industrial robots, now rely on application software to provide user-visible differentiation, a trend that should continue. The rise of the Internet of Things (IoT) and the spread of software in sectors such as connected cars means that software will run all aspects of our world, and the vast majority of that software will be application-level code.

#### The Changing Debugging Challenge

The ways embedded and application software is written and debugged traditionally have been very different. Tracking down a bug depends on three things – visibility of code, the time between the bug striking and a problem being detected, and how deterministic the failure is, e.g. does the failure unfold in exactly the same way from the same starting state or does it vary due to outside factors.

These scenarios are, however, not identical for embedded and application developers. Embedded developers working in tightly constrained environments have had to contend with a lack of visibility into their code and what it's doing. There was normally little clue as to what led to something going wrong or where an issue originated, making it correspondingly hard to track down when creating hardware. For example, when writing code on bare metal or to bring up a device, we don't even have a printf to rely on. Consequently, the Joint Test Action Group (JTAG)

created an IEEE standard to assist with device, board and system testing, diagnosis and fault isolation. JTAG is now used as the primary means of accessing sub-blocks of integrated circuits, making it an essential mechanism for debugging embedded systems that may not have any other debug-capable communications channel. On most systems, JTAG-based debugging is available from the very first instruction after CPU reset, letting it assist with development of early boot software that runs before anything is set up.

Along with integrated circuits, entire software debugging, instruction tracing and data tracing infrastructures based around JTAG have been created for software debug around silicon architectures, from PowerPC to ARM. Processors can normally be halted, single-stepped or let run freely. Developers can set code breakpoints, both for code in RAM (often using a special machine instruction) and in ROM/Flash. Most designs have "halt mode debugging", but some allow debuggers to access registers and data buses without halting the core being debugged.

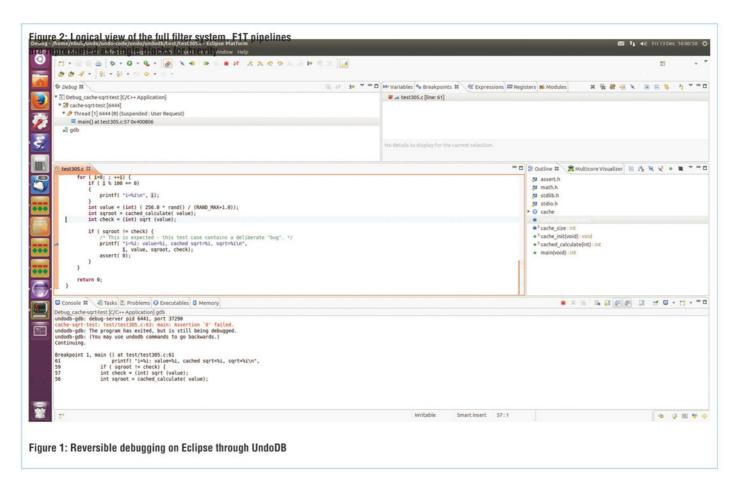

Often used in conjunction with hardware emulators, JTAG provides a rich variety of powerful debugging tools for embedded developers, including the ability to reversibly debug code; for example, debuggers can often step or run code in reverse, which is incredibly powerful when trying to track down the most elusive bugs.

#### **Debugging Application Code**

In contrast, application developers have greater visibility into what their programs are doing – at least the trusty printf is available, plus the developer can (usually) be confident that the hardware and OS on which their code is running is stable.

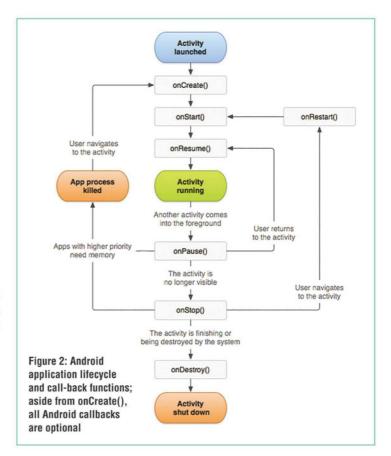

However, this is outweighed by modern devices' software stacks being so much more complicated, with many more factors impacting how a program behaves. Take an Android phone app for example. It may work perfectly well on one version of the operating system on a particular phone, but exhibit bugs on others due to the fact that developers simply cannot have visibility over all potential characteristics. It is much less deterministic, with inputs from outside the program (user interaction, network sockets or system calls, for example), all potentially affecting reliability.

Essentially, it is a different sort of visibility problem, one that is getting worse as code becomes more complex and runs on more diverse devices. So it is no wonder that a study from the Judge Business School of the University of Cambridge, UK, published in 2013, found that the global cost of debugging software had risen to \$312bn annually. The study reported that developers spend 50% of their development time fixing bugs or making code work, rather than designing or writing new code. The vast majority of debugging time is spent locating the bug - once it has been found, correcting it is normally relatively simple.

#### The Options For Application Developers