# Electronics WORLD

THE ESSENTIAL ELECTRONICS ENGINEERING MAGAZINE

## **Keysight FieldFox**

Industry's first 50 GHz handheld analyzer

#### SPECIAL REPORT

#### ON LOW POWER DESIGN:

- Filters

- NOCs

- SOCs

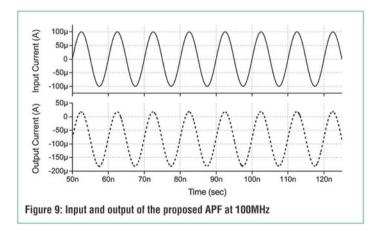

Technology

IC developed to very

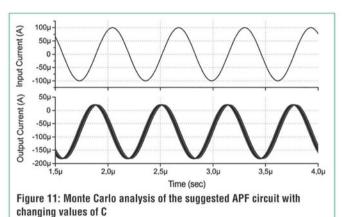

accurately measure Earth's

magnetosphere

Analog Design

Past and future, according

to Bob Dobkin, Linear

Technology's co-founder

Products

Latest components,

systems and

equipment

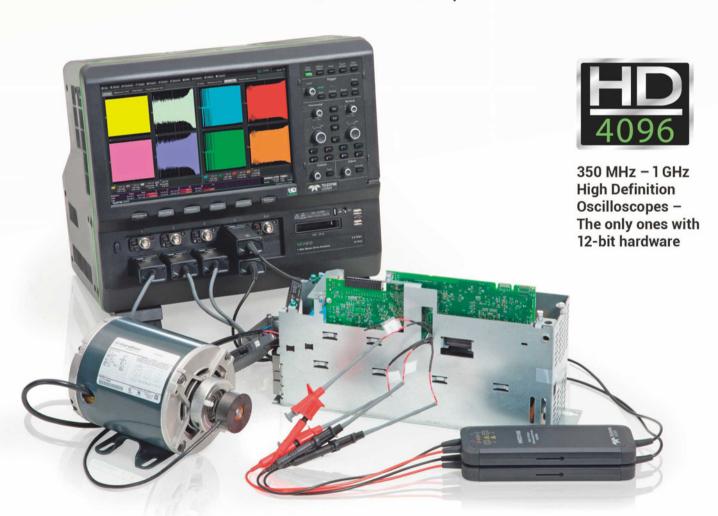

# Complete Power Analysis for 3 Phase Motor Drives

**NEW!** Motor Drive Analyzer MDA800 – 8 Channel, 12-bit, up to 1 GHz

Who's doing that?

teledynelecroy.com

#### REGULARS

05 TREND

ELECTRIFICATION SPURS AUTOMOTIVE POWERTRAIN SEMICONDUCTOR MARKET GROWTH

06 TECHNOLOGY

08 RASPBERRY PI COLUMN

12 LTE COLUMN

14 EMBEDDED USER INTERFACE DESIGN ON A BUDGET

by Lucio Di Jasio

18 THE TROUBLE WITH RF...

SOMETIMES WE CAN DO THE IMPOSSIBLE by **Myk Dormer**

45 EVENT

NORTHERN MANUFACTURING & ELECTRONICS

46 EVENT ECOC 2015

INDUSTRY ANNOUNCEMENTS

9 PRODUCTS

46

41

Cover supplied by KEYSIGHT TECHNOLOGIES More on pages 20-21

#### **FEATURES**

THE EVOLUTION OF ANALOG CIRCUITS

By **Bob Dobkin**, Co-Founder and Chief Technical Officer of Linear Technology

24 PUSHING THE LIMITS

**Lucio di Jasio**, electronics engineer and technical author, explains how to increase the USB current limit to charge portable devices more efficiently

28 NOVEL HIGH-PERFORMANCE MECHANISM FOR PREDICTING INTER-ROUTER SWITCH ALLOCATIONS

Jian Cao, Hai Jiao, Yuan Wang, Qihui Zhang and Xing Zhang from the School of Software and Microelectronics at Peking University propose a novel mechanism to increase network saturation throughput and minimize packet average latency thanks to a three-stage router pipeline and a look-ahead routing algorithm

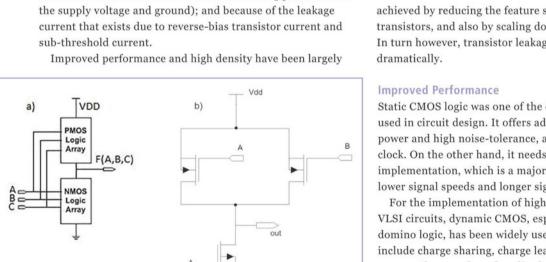

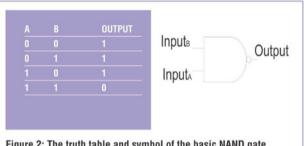

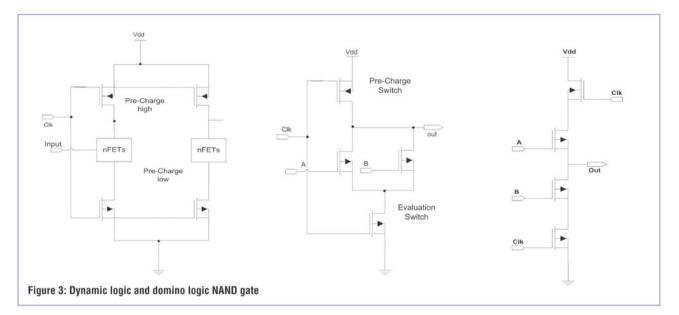

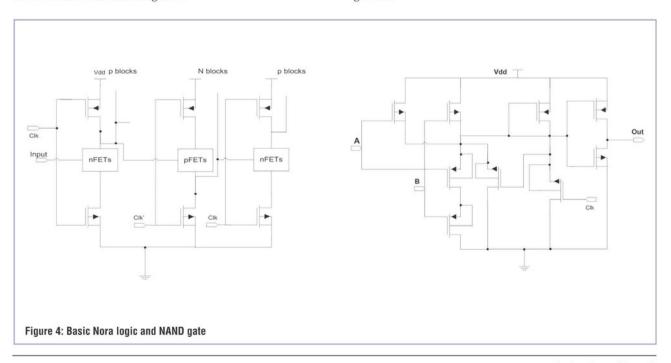

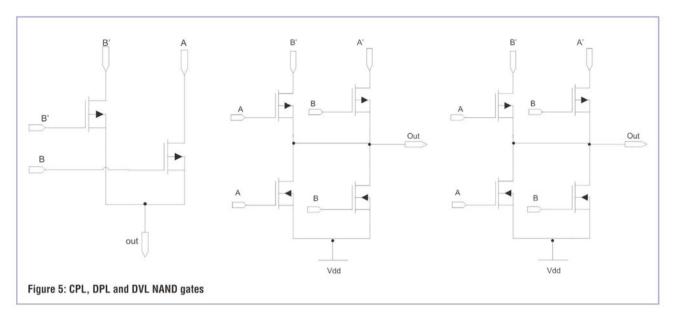

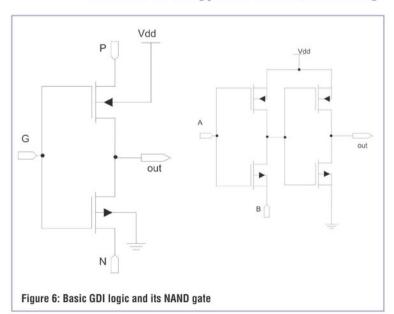

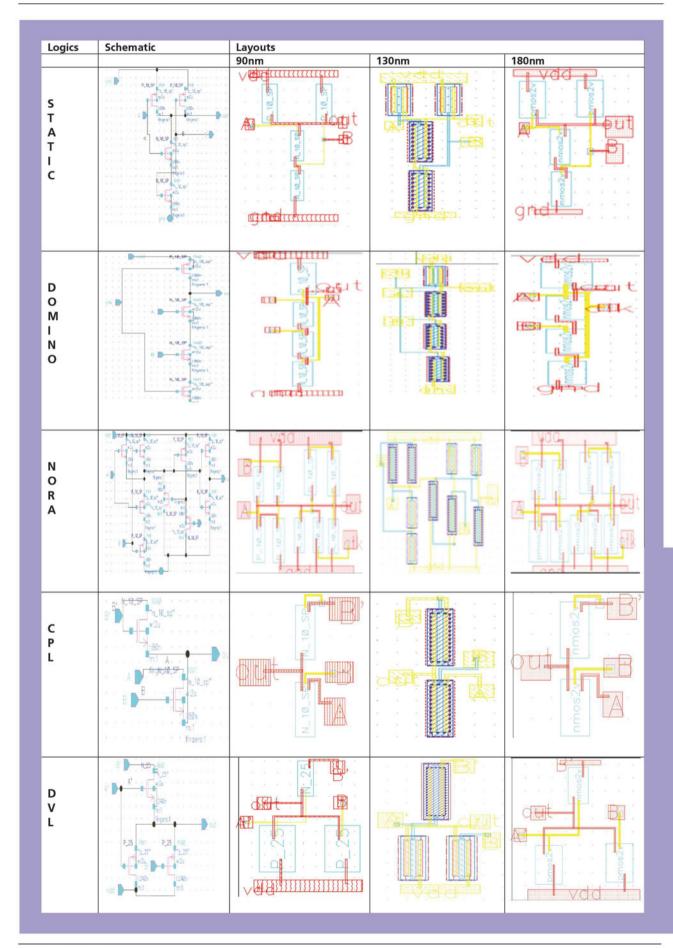

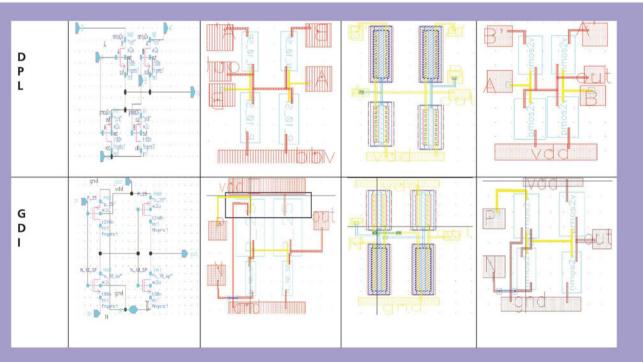

32 PERFORMANCE ANALYSIS OF DIFFERENT DIGITAL LOGIC FAMILIES FOR THE SYNTHESIS OF NAND GATES

In deep submicron nanometer CMOS process technologies, leakage power has become a significant concern for the design of low-power SOCs. **Momna Asghar, Sidra Ashraf** and **Shabbir Majeed** from University of Engineering and Technology in Taxila, Pakistan, investigate

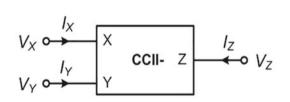

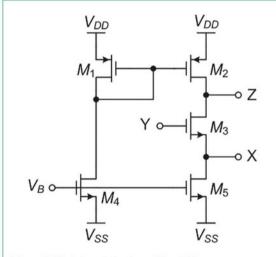

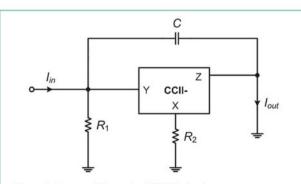

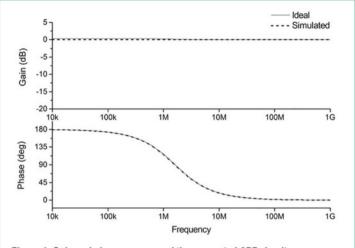

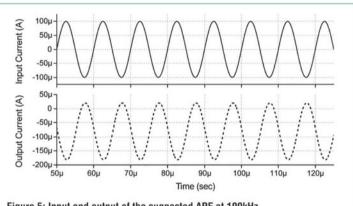

38 SINGLE CCII-BASED, FIRST-ORDER, CURRENT-MODE, ALL-PASS FILTER

**Firat Yucel** of Akdeniz University and **Erkan Yuce** of Pamukkale University, both in Turkey, present a current-mode first-order all-pass filter consisting of only two grounded resistors and a floating capacitor, which dissipates very low power

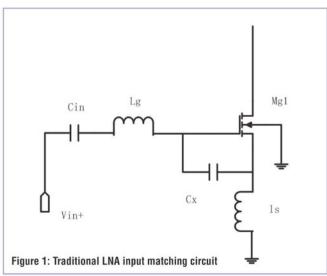

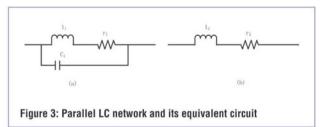

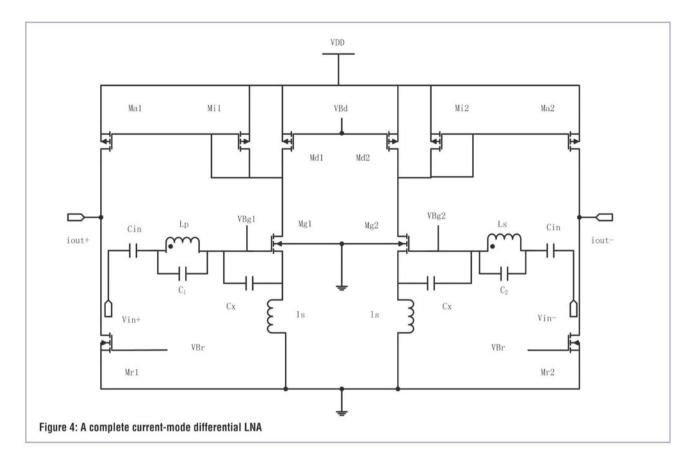

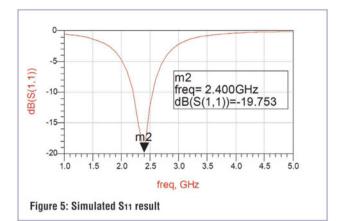

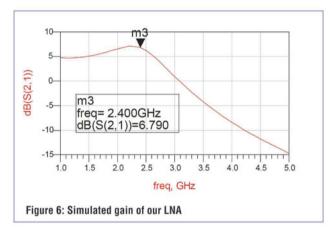

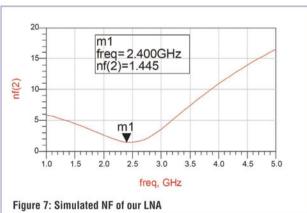

LOW-VOLTAGE LOW-POWER LOW-COST CURRENT MODE LNA

Minglin Ma, Xiangliang Jin, Yuan Chen, Chengwei Li and Zhijun Li from Xiangtan University in China present a low-voltage, low-power and low-cost current-mode differential low noise amplifier, operating at 2.4GHz, and based on a standard TSMC 0.18 $\mu$ m RF CMOS process

Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry – particularly as regards electric shock, fire hazards and explosions.

## THE WORLD'S LARGEST SELECTION .ABLE FOR IMMEDIATE SHIPM

## DIGIKEY.CO.UK 0800 587 0991 0800 904 7786

OPEN ACCOUNTS AVAILABLE FOR QUALIFYING CUSTOMERS

LIVE WEB CHAT: 24/7, 365 DAYS PER YEAR

FREE SHIPPING ON ORDERS OVER £50\*

PRICES ARE IN BRITISH POUND STERLING AND INCLUDE DUTIES

### **LOCAL SALES &** TECHNICAL SUPPORT AVAILABLE

1,000,000+ PRODUCTS IN STOCK | 650+ INDUSTRY-LEADING SUPPLIERS | 3.9 MILLION PARTS ONLINE

\*A shipping charge of £12.00 will be billed on all orders of less than £50.00. All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in British pound sterling and include duties. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2015 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

### **AUTOMOTIVE** POWERTRAIN SEMICONDUCTOR MARKET GROWS

Increasing volumes of new vehicles and the need for fuel-efficient technologies are ramping up the automotive powertrain semiconductor market, which grew 8.3% in 2014, according to US-based analysis house IHS. Forecasts are that these revenues will continue to grow with a compound annual growth rate (CAGR) of nearly 6% in the next five years, from \$7.2bn in

Electrification is propelling the powertrain semiconductor market on a global scale. This includes start-stop systems, forecast to grow at a CAGR of 21%, and plug-in hybrid vehicles, expected to grow at CAGR or 37% for the next five years. In addition, for internal combustion engines there is an increasing trend away from traditional incumbent multi-port fuel injection systems towards gasoline direct-injection systems. Direct injection systems are more efficient and require higher semiconductor content than their multi-port counterparts.

"Propulsion systems for electric and hybrid vehicles demand, on average, 10 times more semiconductor content than a conventional engine," said Ahad Buksh, analyst for automotive semiconductors at IHS. "Without electrification, the powertrain semiconductor market would have grown only 3.1% annually for the next five years, whereas electrification is now accelerating the market at 6% growth rate annually."

Some key components of electrification for the powertrain include the motor inverter, DC/DC converter, battery management system and plug-in charger, all of which require

2014 to \$9.5bn in 2019.

For internal combustion engines, there is an increasing trend away from traditional incumbent multi-port fuel injection systems towards gasoline direct

power management by analog integrated circuits (ICs) and discrete components. These systems saw growth of 24% in 2014 and another 22% increase is forecast for 2015, according to IHS, the highest of any automotive semiconductor application.

From a revenue perspective, semiconductor content in electric and hybrid vehicles are expected to generate more than \$1bn in total revenue growth from 2014 to 2019, by which time IHS forecasts \$1.6bn will be generated in this segment. In addition, emissions legislation efforts in most regions around the world are the main drivers for semiconductor sales in powertrain applications, while current concepts in engines and exhaust after-treatment systems for ICEs. together with a requirement for on-board diagnostics, require sensors for their operation. As a result, the market for semiconductors in internal combustion engines was \$4.3bn in 2014, growing to \$5.4bn in 2019, says IHS.

The engine control unit (ECU) uses most of the semiconductors in these applications, in addition to a growing trend toward electrification of various

> components - including fans, water pumps and oil pumps that will further contribute to powertrain semiconductor revenues in the future.

> Transmissions are well-established systems for semiconductors, but recent new concepts such as dualclutch transmissions (DCTs) and continuously variable transmissions (CVTs) have entered the market. As a result, this portion of the semiconductor market is expected to grow from \$1.4bn in 2014 to \$1.5bn by 2019, according to IHS. Most new growth stems from the demands on microcontrollers, particularly as a result of increased sensor content featured in new transmissions.

IHS forecasts that on a regional basis, China, Japan and eventually Europe will drive the market for DCTs, while China, South Asia and eventually North America will drive the market for CVTs.

IHS offers insight, analytics and expertise in critical areas that shape today's business landscape since 1959 (www.ihs.com)

#### EDITOR: Svetlana Josifovska

Tel: +44 (0)1732 883392 Email: svetlanaj@sjpbusinessmedia.com

SALES: Philip Woolley

Email: philipw@sjpbusinessmedia.com

**DESIGN: Tania King PUBLISHER: Justyn Gidley**  ISSN: 1365-4675

PRINTER: Buxton Press Ltd

#### SUBSCRIPTIONS:

1 year: £62 (UK); £89 (worldwide)

Tel/Fax +44 (0)1635 879361/868594 Email: electronicsworld@circdata.com

2nd Floor. 52-54 Gracechurch Street, London, EC3A 0EH

Follow us on Twitter

Join us on LinkedIn

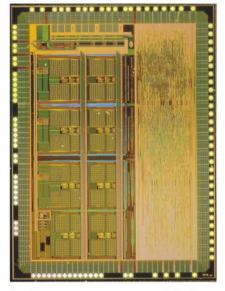

## PARTNERS ENABLE SATELLITE-BASED EXPLORATION OF THE EARTH'S MAGNETOSPHERE

The Fraunhofer Institute for Integrated Circuits, the Space Research Institute of the Austrian Academy of Sciences and the Full Service Foundry division of ams, a provider of high performance sensors and analog ICs, have jointly developed a new IC for highly accurate measurements of the Earth's magnetosphere from space.

As part of NASA's "Magnetospheric Multiscale" mission launched in March, four identically-equipped satellites are performing highly accurate three-dimensional measurements of the Earth's magnetosphere to assess its dynamics. The research focuses on the so-called magnetic reconnection, a physical process in which the Earth's magnetic energy is converted into kinetic and thermal energies and particle acceleration. Magnetic reconnection is one of the mechanisms responsible for the aurora, as well as for temporary disturbances in the Earth's magnetosphere.

Like all measurement instruments and equipment in satellites, the Space Research Institute's magnetometer has to be very small

IC for highly accurate measurements of the Earth's magnetosphere

and light, and consume very little power. In addition, it must offer very high accuracy under harsh conditions that include radiation and very

low temperatures. The satellites' digital flux-gate magnetometer (DFG) operates at a resolution of 10pT — several thousand times more sensitive than a conventional electronic compass — enabling the sensing of the smallest variations in magnetic flux.

The Fraunhofer ASIC was fabricated by ams using its specialty 0.35µm CMOS (C35) process technology, which allows for the design of complex analog/mixed-signal integrated circuits. Based on a unique process architecture, the rad-hard C35 technology is very well suited for use in space and aerospace applications.

"The ams specialty 0.35µm CMOS process enabled the team of researchers and scientists at Fraunhofer to develop a complex analog/mixed-signal integrated circuit that impressively outperformed our expectations in all respects — performance, power consumption, die area and reliability," said Johann Hauer, project manager for ASIC Development at Fraunhofer.

## TOSHIBA DEVELOPS TWO NEW PROCESS TECHNOLOGIES FOR MICROCONTROLLERS AND WIRELESS COMMUNICATION ICS

Toshiba has announced a new flash memory embedded technology based on a 65nm logic process that uses less power than current mainstream solutions, and a single-poly non-volatile memory (NVM) process based on 130nm logic and analogue power process

Applying the optimal process to diverse applications will allow Toshiba to expand its product line-up in such areas as microcontrollers, wireless communication ICs, motor controller drivers and power supply ICs.

The IoT market is seeing strong demand for low power consumption in many areas, including wearable and healthcare-related equipment. In response, Toshiba has adopted Silicon Storage Technology's third-generation SuperFlash cell

technology, in combination with its own 65nm logic process. The company has also fine-tuned circuits and manufacturing processes in developing its ultra-low power consumption flash embedded logic process. Microcontrollers for consumer and industrial applications based on this process have up to 60% lower power consumption than current mainstream technology.

Following the first series of microcontrollers,

Toshiba plans to release sample BLE (Bluetooth

Low Energy) products in 2016.

The company aims to lower power consumption for entire systems, targeting 50µA/ MHz operation. In applications where significant cost reductions are a concern, Toshiba has

developed an NVM embedded process that adopts Yield Microelectronics's single-poly MTF (multi-time programmable) cells on Toshiba's 130nm logic process technology.

NVM and analogue circuits are embedded on a single chip that can incorporate multiple functions usually executed by a multi-chip system. This reduces the number of terminals and realises smaller packages. Applying MTP specifications for write times improves the new process's performance while limiting added steps in mask pattern lithography to three or fewer, or even none. By using MTP to adjust output accuracy, Toshiba will expand its product line-up in fields where higher accuracy is essential, such as power management ICs.

## Slim Range with Power Meter and Surge Protection Slim Range with Power

Olson Electronics has expanded the Slim Range to now include the popular Olson Power Meter and Surge Protection.

You can now check what power is being used to ensure the PDU does not get overloaded or easily check what current is being drawn, while the surge protection helps protect equipment from voltage spikes. It's ideal for wall or floor mounting and is available in 5 different sizes.

#### **Standard Features**

- · Olson Power Meter, Displaying Volts, Amps, Watts and Power Factor

- Surge Protection Varistors

- A robust steel construction

- Light grey RAL 7035 paint finish

- High integrity dual earthing and external M5 earth stud with 250mm long earth lead

- The option on three different plugs

- UK 13A fused plug (BS1363)

- 16A IEC 60309 (BS4343) plug

- 32A IEC 60309 (BS4343) plug

- PDU comes with the option of 4, 6, 8, 10 or 12 UK 13A sockets (BS1363)

#### **Technical Data**

Operating Voltage 230VAC Maximum Voltage 250VAC

**Current Rating** 13A/16A/32A

(rating matches plug)

Manufactured to BS5733

Approved to BS EN60950 €

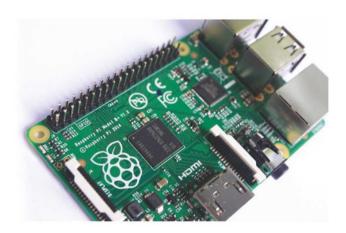

THIS SERIES PRESENTS THE RASPBERRY PI SINGLE-BOARD COMPUTER. ITS FEATURES AND BENEFITS, AND ITS USE IN VARIOUS PROJECTS

### **Making A Temperature** Gauge With The Raspberry Pi

#### BY ANDREW ROBSON AND MIKE COOK

n this project we will use a DS18B20 sensor to detect temperature and display it on screen. We will also write Python code to monitor the temperature and send an e-mail alert when it exceeds a predefined level. The sensor returns a Celsius value, so we will include some optional Python code to do a Fahrenheit conversion. Below is the list of components

needed for this project, which includes:

- 1 x DS18B20 sensor, which looks like a transistor but is actually a highly accurate 1-wire temperature sensor.

- 1 x 4.7kΩ pull-up resistor.

- 1 x solderless breadboard; a prototyping board to which parts and wires can be connected by clipping them on. It is used for prototyping electronics without having to solder parts together.

- Jumper wires: Male-to-male for breadboard connections, and male-

wires usually come in packs of various quantities, colours and sizes. Although only six are needed for this project, 20 or 30 of each are sufficient for most projects. Any length will do for this project, but shorter male-to-male (10cm) and longer male-tofemale (20cm) are best.

to-female for connecting the breadboard to GPIO pins. Jumper

#### Construction

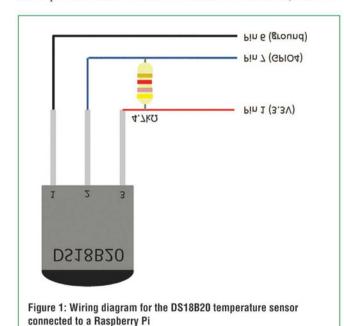

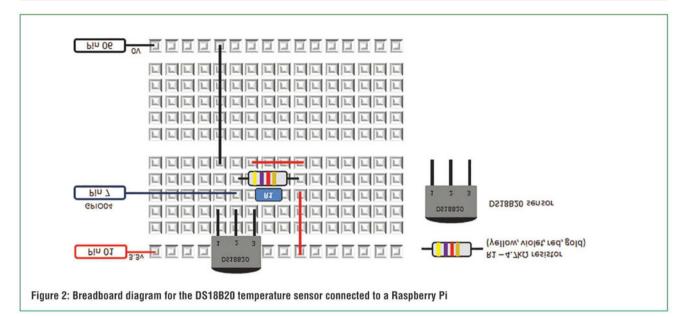

The circuit for this sensor is very easy to build. Beside the power and ground connections, all that's needed is the  $4.7\Omega k$ pull-up resistor between the signal and power as shown in Figures 1 and 2.

Use pin 7 for the sensor connection, as the software used to interface with the DS18B20 is hard-coded for pin 7. This software is built into the Raspberry Pi kernel.

We will be use an application called Modprobe to retrieve the temperature value.

At the Raspberry Pi command prompt, type the following two commands:

#### sudo modprobe w1-gpio sudo modprobe w1-therm

A nice feature of the DS18B20 sensor is the unique number associated with each sensor, permitting quick access to the reading from each one. The preceding command interfaces with the sensor and retrieves the temperature, which is then written to a new directory on the Raspberry Pi, found in /sys/bus/w1/devices/.

To check if this file has been created, we can do a directory listing by typing ls/sys/bus/w1/devices/. This will show a directory that correlates to the unique number of the sensor, similar to 28-0000040be5b6, for example (since each sensor has a unique number, this will vary).

If a directory is still not showing, then we'll need to do the following:

Check the circuit wiring.

- Make sure that the correct resistors are in place. (This is very important - yellow, violet, red, gold.)

- Feel the temperature gauge for warmth: if it feels hot, it's been wired backwards.

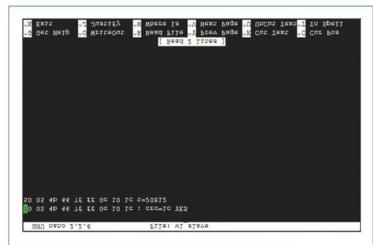

- If you do see the new directory, navigate into it and view the contents of the w1\_slave file, which will contain the temperature value (remember to replace my number with yours):

#### cd/sys/bus/w1/devices/28-0000040be5b6 nano w1 slave

You will now see the contents of the w1\_slave file, which contains the temperature data in Celsius. In my example (see Figure 3), the temperature is 20.812 degrees Celsius. Press Ctrl + X, followed by N to exit.

Now that testing is complete and the sensor is working well, we'll need to write Python code to automate the preceding and print the temperature to the screen, as shown in Listing 1:

```

#!/usr/bin/env python

```

Home Automation: temperature check

For the Raspberry Pi

import subprocess

import time

def fileexists(filename):

try:

with open(filename): pass

except IOError:

return False

return True

def GetTemperature():

#set this variable to true if you want a Fahrenheit

#temperature Fahrenheit = False

#These two lines call the modprobe application to get the

#temperature from the sensor

subprocess.call(['modprobe', 'w1-gpio'])

subprocess.call(['modprobe', 'w1-therm'])

#Open the file that you viewed earlier so that Python can #see what is in it. Replace the serial number with

#your own number

filename = "/sys/bus/w1/devices/28-0000040be5b6/

w1\_slave"

if (fileexists(filename)):

tfile = open(filename)

else:

return o

# Read the w1 slave file into memory

text = tfile.read()

# Close the file

tfile.close()

# You are interested in the second line so this code will

# put the second line into the secondline variable

secondline = text.split("\n")[1]

Figure 3: The temperature shown in the w1\_slave file that was created by Modprobe

#### Listing 1: Temperature check

main()

Lastly, we can create code to monitor the temperature and send an e-mail when it exceeds a particular value, using the SendEmail function from the e-mail project (project 4 in Chapter 13 of the book). Using this program, replace the main routine with the code in Listing 2.

# This is the main routine of the program tempind=False while True: temperature=GetTemperature() if temperature > 25 and tempind==False: #Use the SendEmail routine from the #e-mail project SendEmail("The temperature is "+; str(temperature)) tempind=True; else: #This will ensure you only receive one e-mail #once the temperature is above 25 #This variable is set back to false when the #temperature is less than or equal to 25 tempind=False; #Fetch the temperature every 10 seconds time.sleep(10)

#### Listing 2: Temperature alert

This is an edited extract from the book 'Raspberry Pi Projects' by Dr Andrew Robinson and Mike Cook, published by Wiley

#### **RASPBERRY PI PROJECTS** Raspberry Pi represents a new generation of computers that encourage the user to play and learn. This book is aimed at the beginner Raspberry Pi user who wants to create real-world Containing 16 practical projects, this fun and Raspberry Pi Projects introduces readers to the skills required in order to make the most of the Pi. available in paperback and e-book format, priced £14.99. We have several copies of this book to give away.

To win a copy, register your interest by writing to the Editor at

The Proteus Design Suite now includes full support for data exchange with Mechanical CAD packages via the STEP/IGES file formats. This allows you to better visualise your design and helps quickly solve fixtures, fittings and casement problems.

Import 3D STEP/IGES models for your parts and visualise inside the Proteus Design Suite. Export your completed board to Solidworks or other MCAD software.

Visit www.labcenter.com Tel:+44 01756753440 E-Mail info@labcenter.com

ememble blame for 3G Auction similar and Gethe free

emember the telecoms crash of 2001? Some blame it on the over-exuberant bidding for 3G wireless spectrum at the time. Auctions in the UK reaped £22.5bn, and similar amounts were gained in the US and Germany. In the bleak aftermath of the frenzy, some licence winners ended up

defaulting on their payments.

The promise of 3G technology was faster data rates and higher throughput. But wait – who was using mobile data applications 10-15 years ago? At the time, 3G was really a solution in search of a problem – the elusive "killer app". The contours of the future were being drawn by the Blackberry and other devices, but 2007 is when the real killer app came into being with the launch of the iPhone. And that's when we knew we had a problem.

Fast forward to 2015: For the past several years, mobile data traffic has expanded at a compound annual growth rate (CAGR) of 60-70% according to Cisco, who predicts a ten-fold increase in the next five years. How will we make way for all those tweets, bloated attachments and cat videos? That is exactly the problem that

Figure 1: Multi-beam, sector-sculpting base station antennas carve out more capacity for LTE networks

currently occupies the minds of operators, regulators and equipment manufacturers whilst the rest of us are blissfully tapping away on our smartphones and tablets.

More spectrum! Yes, that is obviously a step in the right direction, but spectrum is a finite resource and is becoming scarcer. In the recent AWS-3 auction in the US, bidding closed at almost \$45bn. We have to believe the licensees are keenly aware of the value of the assets they bought.

LTE is another powerful weapon in the battle for capacity. Using orthogonal frequency-division multiple access (OFDMA) modulation, the spectral efficiency of LTE approaches the Shannon Limit – the theoretical maximum of bits that can be transmitted per MHz of radio spectrum. It looks like we have reached the end of the mobile radio access technology rope.

A third approach still open to pursuit is the addition of cells and cell sites. By dividing the coverage area into smaller pieces, the same spectrum can be reused and divided among a smaller group of users. Sector splitting is one way to create more cells. The traditional three 120-degree sectors radiating from a cell tower are split into six, or even nine, by using antennas with narrower beams and by adding radios.

Another method involves placing small cells within the coverage of the larger "macro" cells. Small cell antennas are installed at lower heights, around 5-10m, and are typically placed in hot-spots where they suck up local traffic to the relief of the macro cell.

Having read this far, perhaps you wonder what noise has to do with all this. Let me explain – noise is the enemy of spectral efficiency in LTE networks, the bane of capacity and data throughput. It's Shannon's Limit again – to get LTE up to its maximum speed, the signal-to-noise ratio (SNR) must be considerably higher than with earlier technologies.

Noise from various sources in the environment plays into SNR, but the dominant noise contribution comes from the wireless network itself. Noise spills over from adjacent cells where others are talking and surfing on the same channel that brings the football match to your seat on the crosstown bus. Stronger signals don't provide the solution; they merely result in even more noise everywhere.

The main effort must be focused at reducing the spillover from cell to cell which, of course, is most difficult at the cell

edges. As cells become smaller and more numerous, a higher percentage of their area will be occupied by these boundaries. Therefore, noise mitigation in LTE networks includes making

Noise is the enemy of spectral efficiency in LTE networks, the bane of capacity and data throughput

the cell boundaries as sharp and narrow as possible. No clever algorithms or bleeding edge processor speeds can help here. To achieve this, we must turn to the unsung hero that has been part of every radio system since Marconi and Heaviside – the antenna.

Advances are being made steadily in the art of beam shaping, wherein base-station antennas focus their energy where we want it while reducing stray radiation in other directions. CommScope refers to this specialized RF pattern shaping as sector sculpting, which is made possible by directional antennas, both in azimuth (horizontal direction) and elevation

(vertical space). Sector sculpting allows precise wireless coverage with minimal interference with neighboring cells.

Beam forming and beam switching are other emerging techniques already supported by LTE standards but are just now beginning to gain attention beyond some early implementations in Time Division Duplex (TDD) networks. The basic idea is to put a spotlight on each user and avoid illuminating the bloke one street over. The better one can do this, the higher the use that can be squeezed out of each precious slice of spectrum.

LTE is a noise-limited technology, and reducing that noise is critical to getting the best network performance and a return on that expensive spectrum. Selecting the right antennas is part of the solution, but only a part. Ensuring a clean network means limiting interference within the RF path at each cell site, between cells and between cell layers. Noise is a big no-no and RF engineers have a big role to play in keeping it out.

Erik Lilieholm is technical sales manager for the Wireless Network Engineering team at CommScope. This column is an edited extract from CommScope's new eBook, 'LTE Best Practices'. Over the next few months different authors of this eBook will contribute articles to this section.

### Refactoring The MLA

**LUCIO DI JASIO**, ELECTRONICS ENGINEER AND TECHNICAL AUTHOR, PRESENTS THIS SERIES ON EMBEDDED USER-INTERFACE DESIGN ON A BUDGET

he Microchip Library for Applications (MLA) is a relatively large and successful project, one that has been in constant evolution for over a decade.

The vision at its roots was radical and simple: a single set of libraries to support all PIC microcontrollers, regardless of

their core, be it 8, 16 or 32-bit – a true unified platform for all embedded applications. As a side note, contrast it with the competing and somewhat simplistic vision that all embedded applications should unite under a single core/architecture.

Over the years MLA grew and evolved to support an even larger number of applications; it was adapted to support several new microcontroller architectures, and with code growth and time, there is always accumulation of code debt. This a relatively popular term used nowadays to indicate the compounding effect of many little implementation details, fixes and hacks, each well-meaning but sub-optimal, and although designed to preserve precious legacy and ensure stability, eventually building up to make the resulting (software) product hard to manage, rigid and fragile. The only

healthy way to get rid of code debt is to refactor the code, which may call for tough decisions, some sacrifices and hard work.

So, in early 2014 the MLA design team published a brand new and vastly improved library. Officially we should refer to it as the current MLA, as opposed to the legacy version that has been archived (but is still available, together with a dozen previous revisions) on a separate page of Microchip's website. Two more releases have followed since, one being published only in May, to consolidate features and complete the refactoring process.

#### Changes

Let's start with what didn't change: The unified platform vision remained. The application libraries are the same (graphics, touch, file system, USB...) and the broader architectural setup is the same – hardware abstraction, module configuration, full source-code availability etc.

So far so good, so what was all the "refactoring" about? Here are the details, and better perhaps, the reasons for it and the resulting benefits:

| Legacy MLA                                         | Current MLA                              |

|----------------------------------------------------|------------------------------------------|

| mla_install>/Microchip                             | <mla_install>/framework</mla_install>    |

| <mla_install>/Microchip/Include</mla_install>      | <mla_install>/framework</mla_install>    |

| <mla_install>/Microchip/Help</mla_install>         | <mla_install>/doc</mla_install>          |

| <mla_install>/[demos]</mla_install>                | <mla_install>/apps/[demos]</mla_install> |

| <mal_install>/Board Support Packages</mal_install> | <mla_install>/bsp</mla_install>          |

Table 1: Legacy vs updated (current) MLA

#### 1. New folder and file naming convention and organization

This is the most visible change that will cause the most (initial) concern, but it is by far the easiest to understand. As shown in Table 1, the main source code folder is now renamed framework, all the demo projects have been grouped in an apps folder and all the documentation has been grouped in a doc folder, conveniently exposed at the top of the directory structure. More importantly, all the folders and file names have been changed to use only lower case letters, remove spaces and keep things consistent across libraries.

The primary reason for the naming conventions change is the need for cross-platform compatibility (OSX, Windows, Linux). To further improve cross-platform support, the entire set of CHM (Windows only) help files has been replaced by a Javabased help system and a set of PDF documents.

Also, you will appreciate how in the new folder structure all the included files are not separated from their source libraries, reducing "folder hopping" when adding them to your projects in MPLAB X.

#### 2. Exclusive support for MPLAB X and XC compilers

Five years after the introduction of MPLAB X and the unification of all PIC compilers under a single umbrella with the MPLAB XC suite, it was time to let go of hundreds of old project configurations to focus exclusively on the new tool chain. This reduced demo apps clutter and allowed better streamlined testing.

Also, the unified MPLAB XC suite provides a more uniform set of preprocessor directives (pragmas, definitions...), removing the need for macros (previously defined in compiler.h) and many conditional directives (#ifdef), effectively reducing code clutter and improving readability.

#### 3. Custom types replaced by C99 fixed-width data types

Since all the new MPLAB XC compilers support the C99 standard, usage of custom definitions, such as BYTE, WORD, DWORD, is now superseded by fixed-width data types, such as uint8\_t, uint16\_t, uint32\_t, etc. This change helps avoid conflicts when combining MLA firmware with other (open source) libraries and applications.

#### 4. Improving the hardware abstraction

If there is one piece of information you should have learned from all the previous columns in this series, it's the key role of the HardwareProfile(.h) as primary mechanism for abstraction of hardware detail in the MLA. But having been conceived only as an include file, it posed some serious limitations. It is now replaced by a combination of three files: system.c, system.h and system\_config.h to allow a more flexible and clean abstraction mechanism.

Whereas before the hardware profile could contain only definitions for pin and peripheral names, that job is now performed by the system\_config.h file, while system.c collects all the hardware initialization functions required for the target board of choice.

In Listing 1 you'll find a segment of a typical system.c file to be used in a code example for a PIC24 Mikromedia board and, in particular, the SYSTEM\_BoardInitialize() function.

```

void SYSTEM_BoardInitialize(void)

{

DisplayBacklightConfig();

DisplayPowerConfig();

DisplayBacklightOff();

// Initialize the Display Driver

DRV_GFX_Initialize();

// make all pin digital by default

AD1PCFG = oxFFFF; // all inputs (not touch) digital

// configure PPS for PIC24 Mikromedia

PPSUnLock;

// SPI2

PPSInput(PPS SDI2, PPS RP26); // SDI2 = RP26 G7/pin

PPSOutput( PPS RP21, PPS SCK2OUT); // SCK2 =RP21

G6/pin 10

PPSOutput(PPS_RP19, PPS_SDO2); // SDO2 =RP19 G8/

pin 12

// configure Serial Flash CS pin

M25P8o_CS_LAT = 1;

M25P8o_CS_TRIS = 0;

// configure Codec CS pin

CODEC_CS_Disable();

CODEC CS Config();

CODEC_DCS_Disable();

CODEC DCS Config();

SYSTEM_TickInitialize(1);

TouchInit(NVMWrite, NVMRead, NVMSectorErase,

NULL);

// initialize the Graphics library

GFX_Initialize();

} // Board Initialize

```

Listing 1: system.c - SYSTEM\_BoardInitialize() Function

The unified MPLAB XC suite provides a more effectively reducing code clutter and improving readability

Such function can now be shared among all projects targeting the same Mikromedia board instead of being repeated in the main.c file of each project. The net result is a considerable reduction of code duplication and of the number of conditional compilation directives (#ifdef) previously seen in the legacy MLA examples.

Relying exclusively on MPLAB X helps here as well, as the project organization can now use the build configuration (and file exclusion) features available, further reducing example code clutter.

#### 5. Peripheral driver abstraction

In the past, different libraries occasionally carried along their own implementation of commonly-used peripheral drivers, making it difficult to use some libraries together by creating potential driver conflicts. In the new structure, not all drivers are fully abstracted yet, but the commonly used ones such as UART and SPI are already available. More will be ported and implemented over time.

#### 6. A migration path to Harmony

In the last few years, USB, graphics and file system support for the PIC32 architecture has been strongly developed in the MPLAB Harmony branch. API compatibility between MLA and Harmony has been greatly improved and will continue to converge further. For example, Graphics Library v4.00 in both MLA and Harmony are already highly compatible.

#### **API Changes**

Eventually it boiled down to this: All libraries' APIs had to change, which will cost the most editing time. But equally this is the simplest kind of refactoring work, something the compiler will be quick to point out and MPLAB X autocompletion feature (CTRL- $\backslash$  or  $\square$ - $\backslash$  for Mac users) will help fix really fast.

All new APIs follow a standard and uniform naming convention for all their functions:

[module]\_[sub-module]¬\_[featureActions]

As an example, a common macro in Legacy MLA:

GetPeripheralClock()

is now:

SYS\_CLK\_FrequencyPeripheralGet()

Although at first this might sound arbitrary, very soon you will notice how convenient and quick it is to guess most of the function names you'll need, based on the library name and the function/action required.

Once again, the main consequence of these changes will be reduction of naming conflicts and better integration with foreign libraries.

#### Summary

We've seen how the MLA vision of a uniform platform is still going strong and that the library is a living organism that keeps evolving. Refactoring the MLA was a bold decision, but a much needed one. The (new) current MLA emerging is a better one because it builds on the strength of the new tool chain (MPLAB X, MPLAB XC), and is now better structured and ready to integrate with larger application code bases. •

#### **USER INTERFACE DESIGN FOR EMBEDDED APPLICATIONS**

Lucio Di Jasio is EMEA Business Development Manager at Microchip Technology. He has held various technical and marketing jobs in the company's 8, 16 and 32-bit divisions for the past 18 years.

Lucio has published several books on programming for embedded control applications, and we have three copies of his book 'Graphics, Touch, Sound and USB, User Interface Design for Embedded Applications' to give away at the end of this series.

If you want to win this book, please send an email to svetlanaj@sjpbusinessmedia.com, mentioning the title in the heading.

EventCity Manchester

30th September to 1st October 2015 9.30am - 4.30pm (4.00pm close Thurs)

#### The exciting Manufacturing Technology **Exhibition in the North**

Over 300+ national and international suppliers will gather in Manchester this autumn for Northern Manufacturing & Electronics 2015 together with the new RoadRailAir event. The exhibition will feature live demonstrations and new product launches of machine tools & tooling, electronics, factory & process automation, packaging & handling, labelling & marking, 3D printing, test & measurement, materials & adhesives, rapid prototyping, ICT, drives & controls and laboratory equipment.

Free industry seminar programme online @ www.industrynorth.co.uk

The exhibition is free to attend, free to park and easy to get to. Doors open at 9.30am on Wednesday 30th September.

Pre-register online now for your free entry badge and show preview at www.industrynorth.co.uk Tel 01784 880890 · email philv@etes.co.uk

FREE SEMINARS I FREE PARKING

ROADRAILAIR

#### YOUR PARTNER FOR QUALITY QUARTZ FREQUENCY CONTROL PRODUCTS, FROM INITIAL DESIGN TO FINAL PRODUCTION

- A fully equipped Design & Test Centre in Munich, where our Design Engineers are available to discuss optimal timing solutions and layout issues for your initial design.

- 3-D images available on request to help with your Design work

- Free Geyer Y-Quartz App analysing tool to help optimize your oscillator circuit and identify the best crystal specifications for your application

All supported by our network of offices in Europe, Asia and America, and factories in Taiwan. S Korea and Japan.

39 Basepoint, Abbey Park, Romsey, Hants, SO51 9AQ, UK Tel: +44 (0) 1794 319318

sales@geyer-electronic.co.uk • www.geyer-electronic.com

## Sometimes We Can Do The Impossible

BY MYK DORMER

ngineering usually consists of methodical application of well-understood techniques to well-defined problem. ... Well, most of the time. On rare occasions however, it can become far less predictable - and far more challenging and enjoyable - when the problem defies conventional solutions, and something innovative needs to be pulled out of the hat.

Integer-N phase-locked loop (PLL) frequency synthesizers are a very well understood and very widely used radio sub-system, providing a clean, programmable frequency source, with stability of the reference clock source.

In a nutshell, these circuits operate by dividing the output of a VCO and a fixed (crystal) reference oscillator down to a common (comparison) frequency, feeding the divider outputs into a phase comparator and using the output to tune the VCO. When the loop is "in lock" the VCO frequency is equal to the comparison frequency multiplied by the divide ratio of the (N) divider. This comparison frequency is the reference oscillator output divided down by the (R) divider.

In mathematical terms:  $F_{out} = (F_{ref}/R) \times N$

There are obviously many additional implementation details that a circuit designer would have to consider, but that is the heart of the system. The finest frequency steps the synthesizer can tune in equals the comparison frequency, which is usually chosen to equal the channel spacing of the radio.

There are many newer, more sophisticated variants on this theme, notably "fractional-N" schemes, where by means of sophisticated logic design the N value is not an integer so the comparison frequency can be larger than the tuning-step size, but many radio devices still use the original, simpler technique I have described.

So what happens when a customer orders a variant of an existing (integer-N synthesizer based) radio on a frequency that is not a multiple of the usual comparison frequency?

Obviously, if the new channel frequency is a multiple of another, similar frequency (such as a change from a 25kHz channel step to 12.5kHz or 20kHz), then the R division ratio is changed to yield a new comparison frequency and N is re-calculated accordingly.

The really interesting problems arise when the new comparison frequency value cannot be generated from the existing reference oscillator frequency by an integer R value, or where the comparison frequency necessary for one or more of the channels is simply too low for acceptable loop dynamic behaviour (in typical narrowband low-power wireless equipment a comparison frequency much below 10kHz is likely to compromise setting time, so, say, a channel frequency of 153.005MHz could prove a problem).

Ideally, an engineer could meet these new requirements with a new radio, such as a new design with a fractional-N PLL, or even a reversion to a crystal-controlled radio, but in the real world, with limited engineering resources and large stocks of existing hardware, it is quite possible that no actual physical changes can be made.

In this case there is an interesting (and cunning) work-around. While it may not be possible to come to a suitable compromise between N and R values and a comparison frequency within acceptable bounds for certain awkward frequencies, it is worth remembering that the PLL doesn't have to produce the exactto-the-last-digit frequency; it only needs to produce a frequency within the frequency tolerance of the radio.

A typical narrowband low-power radio is designed around a frequency tolerance of somewhere around ±1kHz. The stability of

"no viable result" channels will be likely

the reference oscillator will have been specified accordingly, probably with a comfortable margin added in.

To take our VHF example here, typical modules in this band use 5ppm crystals (or

TCXOs), so have an absolute accuracy of around ±750Hz... what happens to the design if the PLL is programmed to generate a frequency that isn't exactly 153.005MHz, but is just within ±100Hz of it?

As far as the operation of the radio is concerned it doesn't matter one jot. The "error" in the PLL output frequency is swamped by the frequency tolerance of the reference, and both added together still fall inside the previously mentioned ±1kHz necessary accuracy.

Programming the N and R values, on the other hand, becomes possible.

Assume a 10MHz reference.

A 5kHz comparison would allow R = 2000, N = 30601, but we

#### Trying to keep a low profile?

Ranging from 40W to 112.5W with convection cooling and up to 225W with forced air cooling. Relec Electronics has a range of open frame ac dc power supplies on a 4" x 2" footprint with a height profile of just 25.4mm for those designs where a low profile is critical. All feature high efficiency with low standby power consumption and a universal ac input. Single fixed outputs range from 12 to 48Vdc on the lower power units and 12 to 58Vdc on the 112.5/225W unit.

Approved to IEC, EN, UL 60950-1 2nd edition, class II safety standards, the 40W & 60W PSU's have an optional function ground enabling them to meet class I when this is connected. Hold up time is between 10 and 16ms; the outputs are fully protected against over voltage and short circuits.

These power supplies are ideally suited for telecom, datacom and a wide range of industrial applications. For further information on the 40W MPE-S040, 60W MPE-T060 or 112.5/225W ABC225 series, view the Relec website or contact us directly.

#### Design solutions for design engineers

Relec Electronics Ltd Tel: 01929 555800 e-mail: sales@relec.co.uk

www.relec.co.uk

have already decided that (to meet settling time requirements) F<sub>comp</sub> must be over 10kHz.

Consider R = 599, N = 9165. The  $F_{comp}$  value is an outlandish 16.6944908kHz but the output frequency is only -8.35Hz different from the desired 153.005MHz.

By allowing small amounts of absolute frequency error in the calculations and accepting that the comparison frequency will have to be different for each channel frequency, it is possible for an integer-N synthesizer to generate output frequencies that at first inspection it should not be able to, whilst maintaining the comparison frequency within acceptable limits. It is even possible to use the same technique to push the comparison frequency up, to improve the settling time of the loop, and as such the radio's dynamic performance.

So, the fractional N synthesizer is an unnecessary complication, and the industry has been wasting this effort for thirty years? Of course not! This technique, whilst useful, has a number of significant limitations, including:

- Generating the combination of N/R values for a "close-enough" output frequency is not something done with a simple linear equation. There may be more sophisticated mathematics that can relate acceptable frequency error to N/R ratio, but it is beyond me; I use a brute force numerical analysis method and a lot of computing time.

- There is no absolute guarantee that every single combination of reference frequency, output frequency and error limit will yield a viable N/R combination. I have occasionally run into cases where no solution can be calculated. If a radio has more than a handful of channel frequencies then one or more "no viable result" channels will be likely.

- It is necessary to store separate N/R values for every channel. Existing radio firmware that generates a "table" of frequencies by assuming a constant R value and calculating N on the fly will not be usable for this method.

Within these limitations, however, this technique is a very useful "work-around" for an otherwise insoluble problem, and for the engineer it gives the enjoyable feeling of having "cheated" the physical laws we struggle with, even if only to a small degree.

Myk Dormer is a Senior RF Design Engineer at Radiometrix Ltd www.radiometrix.com

## Ensuring Optimum Performance of Today's Satellite Systems with FieldFox Handheld Analyzers to Ka Band and Beyond

Wilkie Yu, Keysight Technologies

ccording to recent announcements and forecasts, governments and private enterprises around the world are aiming to place hundreds of new satellites into orbit in the next few years. Many will be the latest generation of high-throughput satellites (HTS), some of which will use Ka-band

frequencies—26.5 to 40 GHz—for up- and downlinks. The result will be tremendous increases in bandwidth and capability, and the ability to deliver advanced services to more people in more places.

In tandem, new earth stations and teleports will be constructed to manage the satellites and direct the signals they carry. To keep everything running smoothly, there is still a need for maintenance and troubleshooting of crucial earth station equipment: antennas, transmitters, receivers and transmission lines.

Testing of these elements has typically required five or six types of RF and microwave test equipment. Today, a single Keysight FieldFox handheld combination analyzer can replace the set of instruments traditionally used for measurements in the field (Figure 1).

#### **Equipping the industry**

As Hewlett-Packard, Agilent Technologies and now Keysight, we have spent decades equipping the satellite industry with exceptional high-frequency instrumentation. This includes vector network analyzers (VNAs), spectrum analyzers, power meters, and cable and antenna testers (CATs).

For field personnel, the all-in-one replacement is Keysight's FieldFox analyzer. These handheld combination analyzers are equipped to handle routine maintenance, in-depth troubleshooting

Figure 1: Easily carried to the antenna flange, FieldFox handheld combination analyzers can be equipped to handle tasks ranging from routine maintenance to in-depth troubleshooting. (Photo courtesy of INTELSAT)

and anything in between. This is possible because they can be equipped for CAT, spectrum analysis, vector network analysis, and more. In every operating mode, FieldFox delivers precise measurements at millimeter-wave frequencies—up to 50 GHz—virtually anywhere satellite maintainers need to go.

While FieldFox provides important advantages in numerous measurement scenarios, spectrum analysis provides an especially compelling example. For more than 20 years, operators around the world have relied on the HP/Agilent 856x series of portable spectrum analyzers as part of their field kit for maintenance and troubleshooting. These widely used instruments are no longer in production and will soon move into the "extended support" phase.

Comparing the 856x series with FieldFox, the most obvious differences are in their physical attributes. An 856x measures 13.25 by 16.81 by 7.38 inches and weighs 38 pounds (17.2 Kg). Equipped with the latest features, functions and user-interface technologies, a 50 GHz FieldFox is just 11.5 by 7.4 by 2.8 inches and weighs 7.1 pounds (3.2 Kg) (Figure 2).

From Day 1, FieldFox was designed for durability: its mechanical design has no fans or vents. The rugged, fully sealed enclosure is compliant with US MIL-PRF-28800F Class 2 requirements. The analyzers have also been type tested to IEC/EN 60529 IP53 requirements for protection from dust and water, extending instrument durability in even the harshest environments.

#### **Delivering modern advantages**

FieldFox delivers exceptional performance, enabling engineers and technicians to carry precision with them. It starts with advanced measurement hardware and software as well as a modern digital architecture. Analog-based spectrum analyzers such as the 8565E/EC suffer from two important shortcomings: log fidelity errors, which affect amplitude accuracy, and span accuracy errors, which affect frequency accuracy. To compensate, users must adjust analyzer settings to place signal of interest at the top/center position of the display: that's the only measurement point that delivers the analyzer's best accuracy.

This is not an issue with FieldFox: its exceptional accuracy of  $\pm 0.5$  dB is available anywhere on the screen, from minimum to maximum displayed frequency and from reference level to noise floor. This saves time and also provides greater confidence in measurement results. Table 1 provides a side-by-side comparison of key features and specifications.

Another timesaving advantage is the ability to start making measurements at power on: warm-up time is not needed. This comes from the "instant alignment" or InstAlign feature built into the analyzer. FieldFox is ready to make accurate spectrum measurements immediately and through any temperature changes over its specified operating range of 14 to 131 °F (-10 to +55 °C).

With these capabilities, FieldFox delivers results that match the world's highest performance spectrum analyzer to within tenths of

|                                                    | FieldFox                  | 856x                        |

|----------------------------------------------------|---------------------------|-----------------------------|

| Amplitude accuracy                                 | ±0.5 dB, no warm up       | > ±4.0 dB after 30 minutes  |

| Spurious-free dynamic range (SFDR)                 | 104 dB                    | 100 dB                      |

| Phase noise at 40 GHz                              | -74 dBc/Hz, 10 kHz offset | –69.7 dBc/Hz, 10 kHz offset |

| Displayed average noise level (DANL), 40 to 50 GHz | -142 dBm/Hz, preamp on    | -127 dBm/Hz                 |

| Tracking generator                                 | 300 kHz to 50 GHz         | 300 kHz to 2.9 GHz          |

FieldFox provides performance advantages in 7.1-pound package that provides a 3.5-hour battery life

a decibel. This ensures confidence in measurements and reduces the risk of accepting bad systems, subsystems or components, or of failing good ones.

#### Applying the all-in-one analyzer

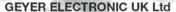

At an earth station, engineers and technicians can use FieldFox to validate system performance with fast, detailed analysis of uplink and downlink signals. This is true within the RF and IF portions of either signal path (Figure 3).

Calibrated CAT and VNA measurements help field personnel maintain cable, waveguide and antenna systems efficiently and consistently. The combination of network analysis, spectrum analysis, power measurements, and more, in one handheld unit enables faster diagnosis and repair of faults.

FieldFox also supports remote operation through an application that runs on a variety of Apple iOS devices. This feature enables collaboration between personnel, one example being an engineer working at a dish and another engineer below, analyzing measurement results using an iPad or iPhone.

#### Reducing upfront and ongoing costs

Although FieldFox replaces multiple instruments, it is priced such that each aspect-CAT, VNA, spectrum analyzer-is about one-half the cost of a comparable benchtop unit. Upfront, this provides a tremendous savings in capital expenditures.

Once FieldFox has been deployed, it also reduces ongoing costs. For example, the analyzer's design has proven its mettle in the field: FieldFox has the lowest failure rate of any complex microwave or millimeter-wave instrument from Keysight.

Another benefit of migrating to modern, field-ready technology is a reduction in operating expenses. FieldFox requires just one calibration per year, reducing annual costs compared to the traditional array of equipment that requires multiple calibrations per year. A standard three-year warranty also reduces overall repair cost.

#### Wrapping up

As new-generation earth stations come on line, FieldFox handheld combination analyzers offer a powerful all-in-one solution. With a robust array of essential, accurate and timesaving capabilities packed into a durable, 7.1-pound (3.2 Kg) unit, engineers and technicians will be equipped for faster diagnosis and repair of today's most advanced installations.

The recently introduced line of six millimeter-wave FieldFox instruments includes three combination-analyzer models that cover 32, 44 or 50 GHz and three spectrum-analyzer models that cover the same frequency ranges. For more information, please visit www.keysight.com/find/FieldFox.

#### **Keysight Technologies** www.keysight.com/find/fieldfox

Figure 3: These simplified block diagrams of transmitter and receiver channels illustrate the elements field personnel can measure, characterize and troubleshoot using a FieldFox all-in-one analyzer.

#### BY BOB DOBKIN, CO-FOUNDER AND CHIEF TECHNICAL OFFICER OF LINEAR TECHNOLOGY

or the last forty years, analog circuits have accounted for 20% of the total integrated circuit (IC) market. As digital ICs advanced both in complexity and function, so have analog ICs. But while digital ICs have increased in functionality, which is based on the number of transistors,

Bob Dobkin - Co-Founder and Chief Technical

Officer of Linear Technology

analog ICs have progressed by other metrics. For digital ICs, performance advances depended on the reduction of both feature size and transistor size. Squeezing more transistors onto a chip increased the productivity of the digital IC. Analog ICs are based on real-world parameters, so power, resolution and speed, among others, are the parameters for improvements in analog productivity.

Digital is information – numbers, voltages and currents do not matter in digital circuits as long as the input and the output are correct. In a digital circuit it doesn't matter how the signal gets from input to output. Digital circuits can be gate arrays, microprocessors or discrete logic, as long as they work properly.

Analog functions take into account real-world parameters, such as voltage and current, noise and speed – all analog

properties defined in analog ICs. So with analog circuits, how you get from an input signal to an output signal is critical.

#### **Process Innovations**

The process innovations for digital ICs have greatly impacted the analog side. Forty years ago analog ICs were produced using an eight-mask process. Almost all manufacturers had very similar processes and the types of devices they produced

were also very similar. Now, each company manufacturing analog ICs has its own processes and variations, so there is no such thing as a plug-in second source.

Process improvements for analog are not only in transistor size, but also in process complexity. Analog ICs are frequently manufactured

with as many as 50 mask layers, and contain a mix of bipolar, CMOS, thin film resistors and other specialized IC components needed for the analog functions.

Analog ICs do not shrink the same way digital ICs do. Some

parameters for analog ICs such as voltage and current require certain chip areas too. Higher voltage demands larger transistors and greater spacing, so new lithography cannot shrink the chip. High-current operation requires large-area transistors, and shrinking parameters do not improve the ability of the transistor to carry high currents. Also, power dissipation requires large chip area and good thermal connections for proper operation. As a result, analog circuitry is more physically tied to the function it performs.

#### **Further Improvements**

The density improvements originally designed for digital have been adopted for analog ICs as well. Smaller transistors operate faster, so applications have flourished using the new transistors enabled by tiny line widths. High-speed RF circuits running at low power at gigahertz frequencies are now common.

Analog-to-digital converters with resolution of over 20 bits, or converters that operate at gigahertz frequencies, are the direct result of having fast, small CMOS transistors as part of the process. As these fine line processes are driven down in cost by the huge volume of digital circuits they support, the analog circuits produced in these processes continue to be more cost-effective and more widely available.

Switching regulators operating at multiple megahertz with 95%-plus efficiency are the result of the finer line transistors. The smaller transistor size allows analog ICs to have an immense amount of digital support circuitry, as well as faster analog circuitry.

Analog component parameters have improved as well, among them op-amp speeds and DC precision. Linear regulators (LDOs) have lower dropout, lower supply current and analog monitoring outputs. New architectures for linear regulators enable the paralleling of devices without specialized external circuitry and adjustment to zero output. One particularly interesting new LDO has an output noise of 1 $\mu V$  from 10Hz to 100kHz – better than many low-noise amplifiers.

#### Commitment

These developments result from new circuit innovations, cleaner fabs, better masking, better defect density in masks and wafers, and larger wafers. Analog integrated circuits have improved their performance, in addition to implementing greater system performance on chip.

Neither digital nor analog ICs have had step function changes from year to year. Development has been a steady progression of improved performance parameters over the last 40 years. Over the next decade and beyond we can look forward to further improvement in analog circuit innovation and performance.

**BOB DOBKIN, CO-FOUNDER** AND CHIEF TECHNICAL OFFICER OF LINEAR **TECHNOLOGY CORP ON...**

#### ... the big difference between analog technology in the 1990s and today:

significant digital content can be combined with analog circuitry on

data converter is available with less than one ppm resolution and less than one ppm linearity. This has trickled down to make 16-bit

#### ... Moore's Law:

Linear circuits are typically several generations behind cutting-edge circuits are below 65nm.

Analog circuits do not need cutting-edge digital line widths. In

#### ... analog designers:

Some people like doing analog circuits and really appreciate the

#### ... the future of analog design:

Analog is still needed with ever-higher performance. We keep

he universal serial bus (USB) is the most used computer interface. It started as an expansion bus for personal computers, but quickly proliferated because of its flexibility, performance and hot-plug capability. Most portable electronic devices that require PC connectivity use USB for file transfers, including MP3 players, digital cameras, mobile phones and tablets.

Since a standard USB bus downstream port can provide at least 500mA (USB 2.0) or 900mA (USB 3.0) of current, it was convenient to use it for charging these devices. But, if this current limit was increased, the charging could be more efficient. This can be achieved with the Microchip USB2534 hub controller with RapidCharge.

If the current required exceeds the limit, then both the charging device and port must follow a protocol to enable battery charging.

A downstream battery charging port is responsible for providing the proper handshake signalling to the charging device to indicate that it is attached to a charging port and can draw current above

the standard USB limits. The proper signalling varies depending on the portable device. Some portable devices follow the USB-IF BC1.2 protocol, but there is an installed base of devices that use proprietary handshake protocols for battery charging, also known as legacy modes.

Legacy devices support some form

of battery-charging detection intended for use with a dedicated charger. Some of these chargers short D+ to D- directly or connect them through a series resistor. For charger detection, some legacy devices assert a voltage on D+ by connecting a pull-up resistor and then sensing a voltage on D-. If a positive voltage is detected, the device can assume it is plugged into a dedicated charger and not a standard USB port.

Other devices pull down one data line while pulling up the other. Once the device detects a charger by the presence of a voltage on D-, it can start charging from the V<sub>bus</sub> connection at current levels that exceed the USB specification.

Other legacy devices that rely on the charger to drive fixed voltages (more than 1V) on the D+ and D- data lines, are referred to as SE1 chargers. If these voltages are sensed by the charging device, the device assumes it is plugged into a dedicated charger and starts charging. A standard USB downstream port would not present these fixed voltages on the D+ and D- lines.

#### **Charger Detection**

Some portable devices follow

the USB-IF BC1.2 protocols, but there is an

handshake protocols, also known as legacy

modes, for battery charging

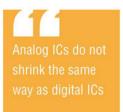

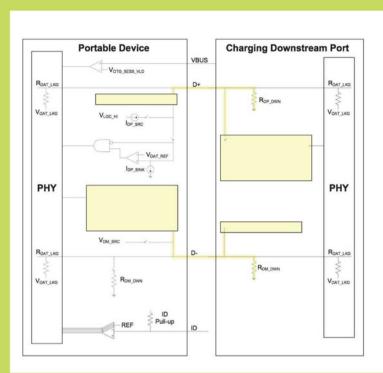

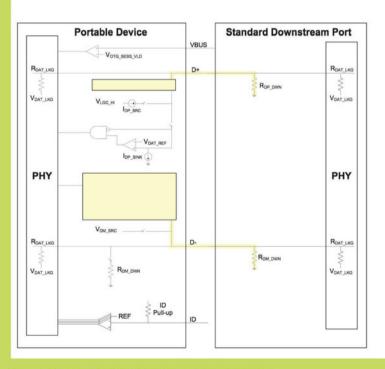

The portable device is responsible for charger detection and Figure 1 shows the necessary hardware.

There are five functional blocks shown in Figure 1 - V<sub>bus</sub> detect, data contact detect, primary detection, secondary detection and ACA detection. A portable device includes a session valid comparator. V<sub>bus</sub> has to be above the threshold voltage before charger detection is

> initiated. This is shown as  $V_{\text{OTG\_SESS\_VLD}}$  on the diagram.

Data contact detect is an optional block used to confirm that the data lines made contact during attachment. A current source on D+ and a pull-down resistor on D- are turned on. If the D+ line goes low, it indicates the data lines are attached to a charging port or a standard port and the logic proceeds to start

primary detection. A timeout circuit is needed to ensure that primary detection starts following a set time after attachment, in case contact is not detected or the data contact detect block is not present.

A portable device is needed to implement primary detection, used to distinguish between a standard downstream port (SDP) and a charging port. Figure 2 shows what happens when the device is connected to a dedicated charging port (DCP); Figure 3 when it is

connected to a charging downstream port (CDP); and Figure 4 when it is connected to an SDP.

Secondary detection is used to distinguish between a DCP and a CDP. If a portable device is ready for enumeration within a set time after V<sub>bus</sub> detection, it can bypass secondary detection; otherwise, it needs to implement it. Only portable devices with a USB Micro-AB connector can support ACA detection, and thus it's optional. Detection is done by measuring the resistance of the ID pin.

#### **Battery Charging**

The Microchip USB2534 hub controller includes RapidCharge technology for providing the proper handshake signalling to portable devices on downstream ports to enable battery charging. It also includes the capability for USB upstream battery-charger detection.

To charge most portable devices it is necessary to provide the proper handshake signals for legacy chargers, SE1 chargers, chargers compliant with Chinese Telecommunications Industry battery-charger specification YD/T 1591-2009, and BC1.2-compliant devices. The hub controller includes all these protocols to implement complete batterycharging, supporting devices from Apple, Samsung and others.

If a USB downstream port is configured to support battery charging, the port is a CDP if it can enumerate the device or DCP if it cannot. If the port is not configured to support battery charging, the port is an SDP.

The downstream ports can also be enabled for battery charging by adding a pull-up resistor (10k $\Omega$ ) on the battery-charging configuration strap for the corresponding port. These straps are sampled at reset, and if they are sampled high the corresponding port is enabled for battery charging.

Battery charging can be also enabled by using battery-charging configuration registers that reside in the USB2534. These configuration registers are used by the internal ROM firmware to configure the battery-charging functionality for each port. The registers can be modified by a configuration programmed in the one time programmable (OTP) memory using the ProTouch programming tool, which was developed by Microchip for configuration and programming of the USB2534 hub controller.

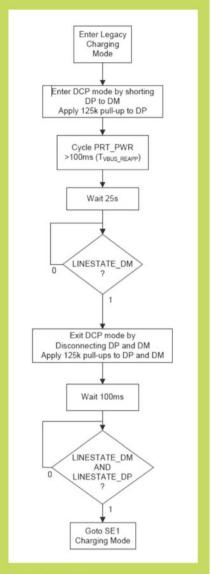

When there is no upstream V<sub>bur</sub>, and consequently no USB host connected on the upstream port, the downstream battery-chargingenabled ports will operate as DCP ports. The battery-charging-enabled ports will exit this mode if the upstream port has a host connection. DCP mode will be also entered if the USB2534 is suspended and remote wakeup disabled.

In DCP-mode battery charging, the port will attempt to handshake with and identify the BC-capable device. Here the device always starts in SE1 mode. It cannot detect that an SE1 device is attached, but can detect that a non-SE1 device is attached when the device toggles DM or DP.

Upon entering RapidCharge mode, the USB2534 goes into SE1 charging mode and the port presents the SE1 voltage levels. If an SE1 device is attached, it will passively detect the SE1 levels and begin to charge. The DCP will not be able to detect the presence of the SE1 device; the port remains in SE1 charging mode while the SE1 PD is charging.

Figure 1: Charger detection hardware

Figure 2: Primary detection with a dedicated charging port

If a BC 1.2 device is attached, its current is enough to pull the D- line low. Likewise, legacy charging devices have been observed to pull the D-line low when attached. To accommodate this, the downstream port transitions to legacy charging mode (Figure 5) if the classic D-line state is detected as low. The D-line state is de-

Figure 3: Primary detection with a charging downstream port

Figure 4: Primary detection with a standard downstream port

bounced to avoid false detects from device plug-ins.

The battery-charging-enabled ports will exit DCP mode and enter CDP mode if the upstream port gets a host connection. Upon detecting the USB-host-set address command, any BC-enabled

Figure 5: Legacy charging mode

port will be turned off for at least 250ms before it can be turned on, to allow the port power to decay. If the host sends a command to turn on the port power, the command will be delayed appropriately; if the command is received after the timer has expired, it will be executed immediately.

An external MCU can override the automatic charger detection sequence by modifying the SMBus runtime batterycharging registers. Because the start of battery-charging detection is set to

occur by default, the MCU must write to the battery-charging control register or the configuration interlock register to disable the automatic sequence before it begins. If the automatic sequence is disabled, the MCU can still initiate it manually.

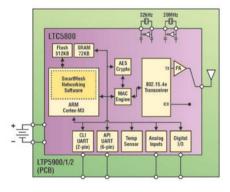

# Wireless Mesh Network. Wired Reliability.

#### Every Node Can Run on Batteries for >10 Years at >99.999% Reliability

The Dust Networks LTC®5800 and LTP®5900 product families from Linear Technology are embedded wireless sensor networks (WSN) that deliver unmatched ultralow power operation and superior reliability. This ensures flexibility in placing sensors exactly where needed, with low cost "peel and stick" installations. The highly integrated SmartMesh® LTC5800 (system-on-chip) and LTP5900 (PCB module) families are the industry's lowest power IEEE 802.15.4e compliant wireless sensor networking products.

#### Features

- Routing Nodes Consume <50μA Average Current

- >99.999% Reliability Even in the Most Challenging RF Environments

- Complete Wireless Mesh Solution No Network Stack Development Required

- Network Management and NIST-Certified Security Capabilities

- Two Standards-Compliant Families: SmartMesh IP (6LoWPAN) and SmartMesh WirelessHART (IEC62591)

D, LT, LTC, LTM, LTP, Linear Technology, the Linear logo, the Dust Networks logo and SmartMesh are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

#### Highly Integrated LTC5800 and LTP5900 Families

#### 🖊 Info and Purchase

www.linear.com/dust

Linear Technology (UK) Ltd., 3 The Listons, Liston Road, Marlow, Buckinghamshire, SL7 1FD, United Kingdom.

Phone: 01628 477066 Fax: 01628 478153 Email: uksales@linear.com

www.linear.com/starterkits

## **NOVEL HIGH-PERFORMANCE MECHANISM**FOR THE PREDICTION OF INTER-ROUTER SWITCH ALLOCATION

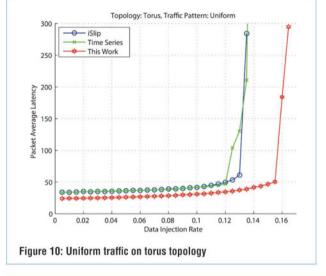

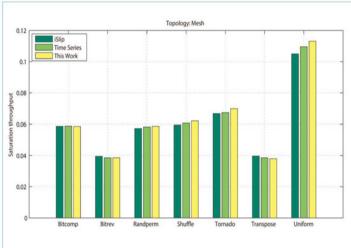

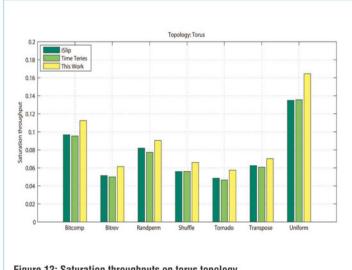

JIAN CAO, HAI JIAO, YUAN WANG, QIHUI ZHANG AND XING ZHANG FROM THE SCHOOL OF SOFTWARE AND MICROELECTRONICS AT PEKING UNIVERSITY PROPOSE A NOVEL MECHANISM TO INCREASE NETWORK SATURATION THROUGHPUT AND MINIMIZE PACKET AVERAGE LATENCY THANKS TO A THREE-STAGE ROUTER PIPELINE AND A LOOK-AHEAD ROUTING ALGORITHM

ith today's increasing demand for computational power and the shrinking transistor sizes, chip complexity is rising at an ever faster speed, aided by the number of cores integrated onto a single die.

Nowadays, the focus of chip design has largely moved from computation-centric to communication-centric, the network-on-a-chip (NoC) being a typical example. NoC was developed to efficiently tackle the tough communications requirements, with hundreds and even thousands of cores integrated onto a single chip. Essentially, the main goal of most

NoC router designs is to maximize network throughput whilst minimizing packet average latency at lower power consumption.

Over the past few years there has been substantial research on different aspects of the NoC, including routing algorithms, fault tolerance, quality-of-service, and so on. The router architecture at the centre of the NoC has a great impact on the area and power consumption of the entire network, as well as packet latency and throughput; therefore, many research projects have been devoted to the effective and efficient design of the NoC router's microarchitecture.

Previously, a lot of effort focused on router pipelined design and quality of switch allocation. Packet chaining and pseudocircuit are some of the design schemes that maximize the quality of router switch allocation by performing 'predictions'

based on historical events and future requests respectively. A speculative router pipelined design successfully reduces the pipelined stages, which offers a lower network zero-load-latency; however, the scheme suffers from a large chip area as it has to integrate more logic for the miss-speculative cases.

In our design, we combined the benefits of switch allocation prediction

and reduced pipelined stages, and as such created a novel router. We used a look-ahead routing algorithm for passing routing calculation information from the upstream router directly to the downstream router before the actual data packets arrive, whilst switch allocation is being optimized in a predicted manner. Thus, a speculative pipelined design could be used together with switch allocation prediction.

#### **Router Architecture**

Our proposed router design belongs to the virtual-channel router family, where each physical channel contains multiple virtual channels to increase the router's efficiency and improve

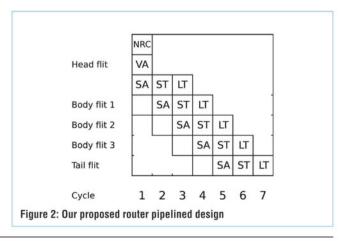

Figure 5: Power consumption of different routers

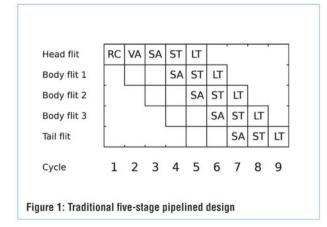

network throughput. The router architecture has a three-stage pipeline: starting with the paralleled execution of routing computation (RC), speculative virtual-channel and switch allocation (Spec-VA/SA), followed by switch traversal (ST) and link traversal (LT), as shown in the space-time diagram of Figure 2.

Since only the head-flit of each packet needs to perform RC and VC allocation, the shorter the package length, the larger the advantage in terms of average packet latency compared to traditional five-stage pipeline router designs as shown in Figure 1.

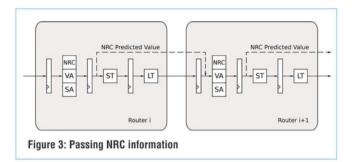

The next-route-computation (NRC) information from an upstream router transmits directly to the downstream router as shown in Figure 3, before the actual arrival of data packets in the former router design carrying routing information in the head-flit. During this time, the downstream router uses the NRC information for switch allocation optimization to increase network throughput, and decrease packet transfer latency and network zero-load-latency. We know that under moderate network traffic, speculative VA and SA stages can be performed successfully, thus producing a lower per-hop packet latency.

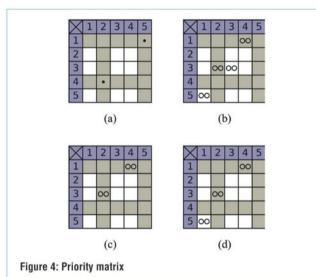

A switch allocator priority matrix is designed to resolve conflicts when multiple input and output requests occur simultaneously. The form of this priority matrix is identical to that of the request matrix, but with ones and zeroes being illegal entries.

As shown in Figure 4a, the predicted request is displayed as a black dot which represents a pending input/ output port request in the next allocation cycle. When such a prediction exists, the priority level of the entire row and column of the matrix is raised to 1, shown with colour cells in the matrix.

To simplify the circuit, when multiple predictions are presented simultaneously, cells in the matrix with prediction intersections, such as (1, 2) and (4, 5) for example, will remain at the same priority level as their neighbours. If conflict within the priority matrix continues, a winner is chosen arbitrarily.

Figures 4b to 4d show an example of the input/output port switch allocation; symbols inside the matrix represent requests in the current cycle, and the colour cells are where allocation priority exists.

A conflicting request is resolved by choosing one with priority; such as for example, eliminating request (3, 3) and leaving (3, 2) as shown in Figures 4b and 4d. Requests outside the priority cells with no conflicts, such as (5, 1) for example, are left within the request matrix after allocation; see Figure 4d.

#### **Router Implementation**

To determine our proposed router's power consumption and area, we used a design compiler from Synopsys, with Verilog RTL codes, and synthesized the design using the TSMC 90nm standard cell library.

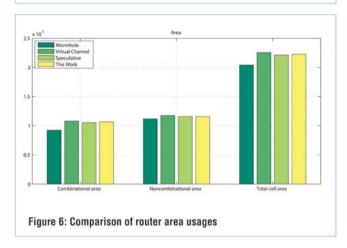

Comparisons of power consumption and area with other modern router designs are shown in Figures 5 and 6 respectively. It can be seen that the proposed router has comparable power consumption and slightly higher area usage due to the included inter-router switch allocation prediction mechanism.

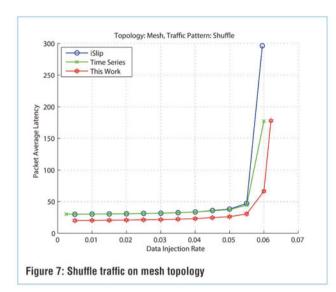

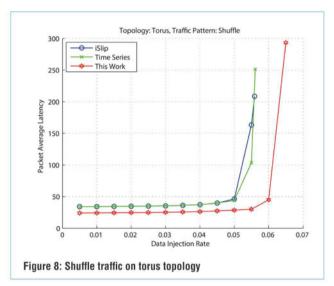

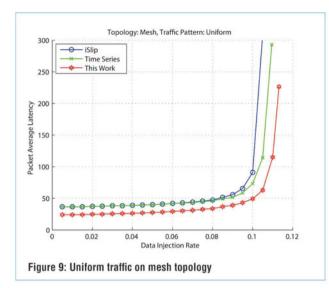

Booksim 2.0, a cycle-accurate NoC simulator, was used to perform estimates of network throughput and average latency. The results were compared with TS-Router and iSlip respectively. The default configurations of the simulator are shown in Table 1. If these configurations are modified in a specific simulation, they will be mentioned to avoid confusion.

The evaluation of the network's average packet latency versus traffic injection rate is iterative, when changing the traffic injection rate on every simulation run; the synthetic traffic

| Topology          | Mesh            |

|-------------------|-----------------|

| K                 |                 |

| N                 |                 |

| Routing Function  | Dimension Order |

| Number of VCs     |                 |

| VC Buffer Size    |                 |

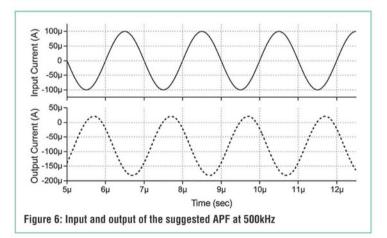

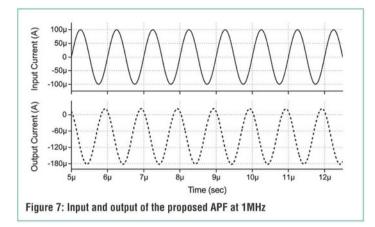

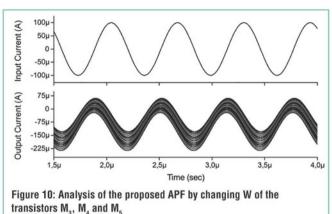

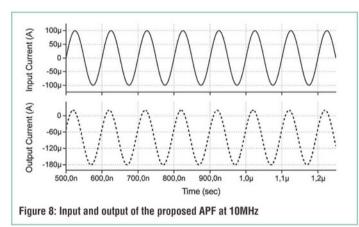

| Packet size       |                 |