www.electronicsworld.co.uk

May 2016 Volume 122 Issue 1961

# **Electronics** VOR THE ESSENTIAL ELECTRONICS ENGINEERING MAGAZINE

2.51

1.5ppm/°C 0.5ppm<sub>p-p</sub>Noise

**Solving Data** Acquisition Compatibility **Problems** with Linear Technology

TTTT

# **SPECIAL REPORT EMBEDDED DESIGN**

Interfaces

V<sub>IN</sub> up to 40V

- Peripherals

- FPGAs

- Software

Technology Newly developed SiC analogue circuit is op-amp-like

6651

2.5 Vout -10 to +10mA

**Regular column** Integrating pyroelectric sensors in wireless designs

# Products IoT hardware, software and applications

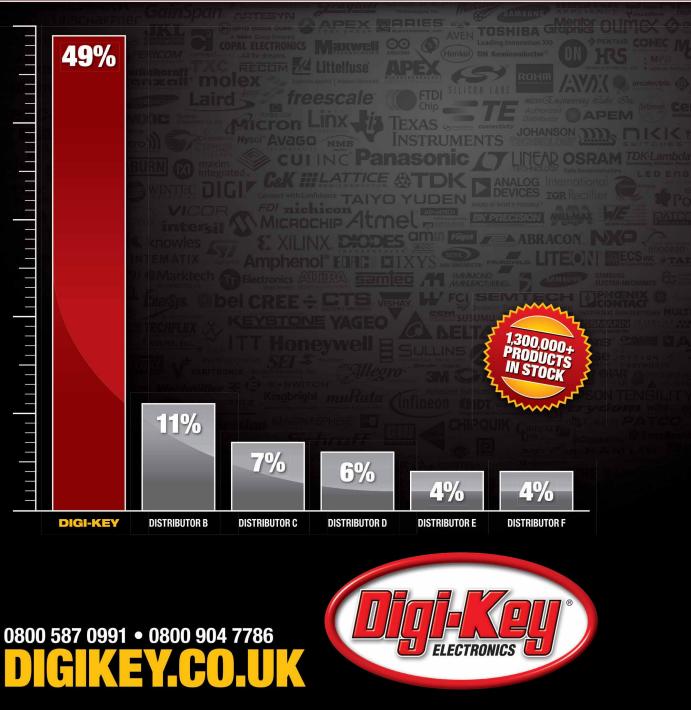

# **BEST OF CLASS: BROADEST OVERALL PRODUCT SELECTION**

Source: AspenCore 2015 Design Engineering and Supplier Interface Study

4.8 MILLION PARTS ONLINE 650+ INDUSTRY-LEADING SUPPLIERS 100% AUTHORIZED DISTRIBUTOR

\*A shipping charge of £12.00 will be billed on all orders of less than £50.00. All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in British pound sterling and include duties. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2016 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

Mecsn CEDA Becia

Cover supplied by LINEAR TECHNOLOGY More on pages 8-9

# FEATURES

# 18 FPGA DESIGN FOR SOFTWARE ENGINEERS

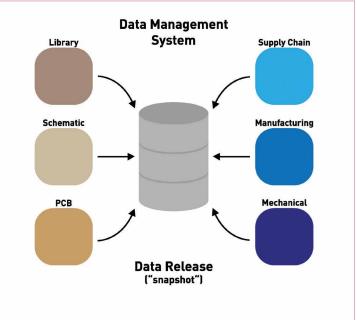

New FPGA design methodology enables software engineers to build high-performance computing engines, using familiar tools and techniques. By **Stephane Monboisset**, Marketing and Business Development Director at PLDA Group

# 22 GETTING THE BEST OUT OF PERIPHERALS

**Mark Pallones**, Team Lead at Microchip Technology, discusses how to configure and integrate peripherals on 8-bit mid-range microcontrollers

# 26 SOFTWARE PACKAGES FOR PCB DESIGN ENVIRONMENTS

By Robert Huxel, Technical Marketing Manager for EMEA at Altium

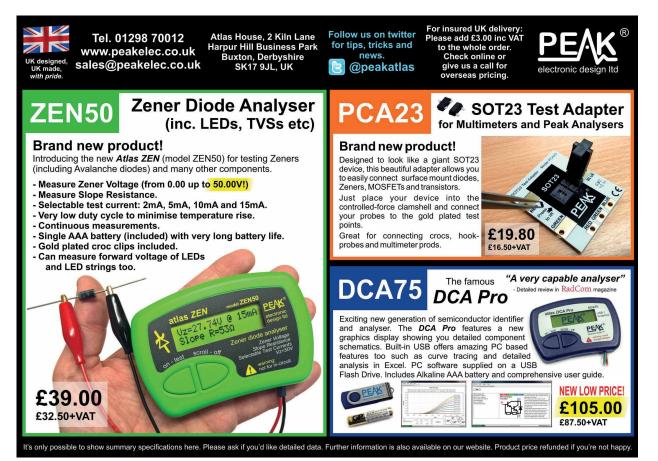

# **30** ONE-WIRE UNIVERSAL LCD INTERFACE

**Professor Dogan Ibrahim** of the Near East University, Cyprus, describes how a text-based LCD can be controlled by sending ASCII commands over just a single data line

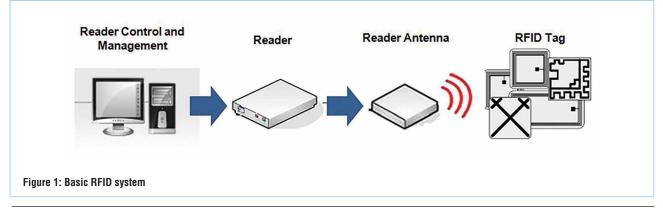

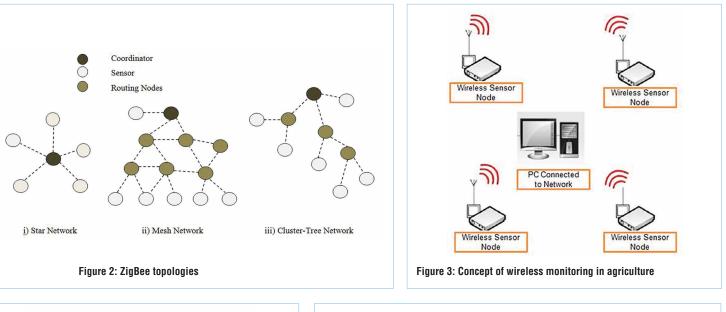

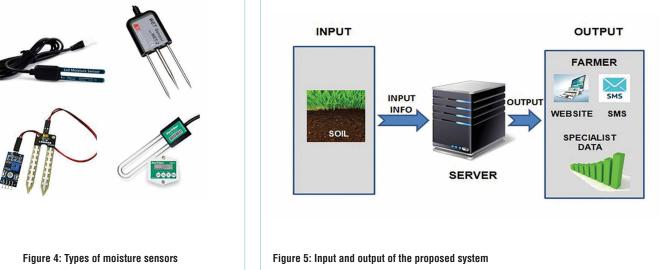

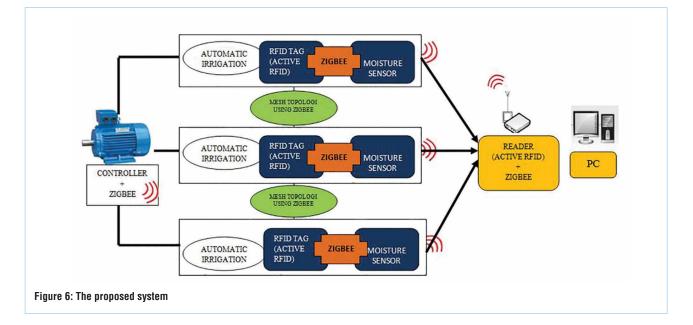

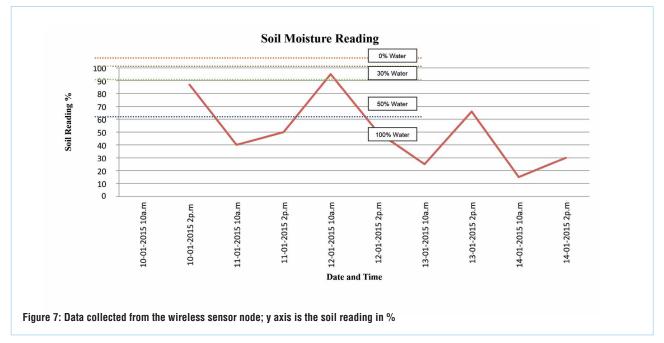

# **34** IMPLEMENTATION OF EMBEDDED ACTIVE RFID AND WIRELESS MESH NETWORK

By **Nursyahida Mohd Noor** and **Che Zalina Zulkafli** from Sultan Idris Education University, Malaysia

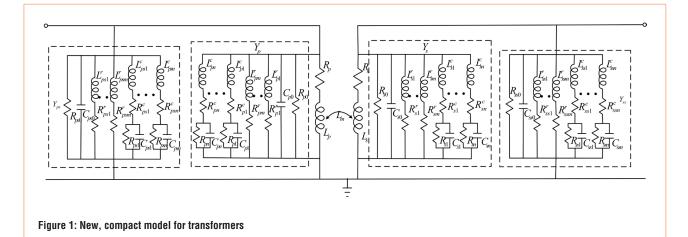

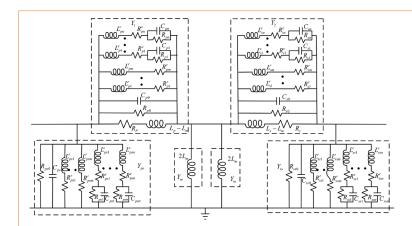

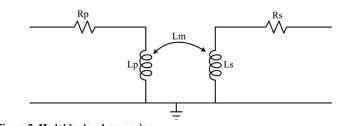

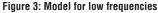

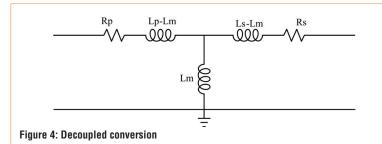

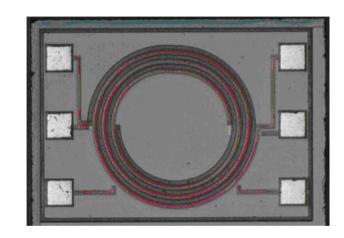

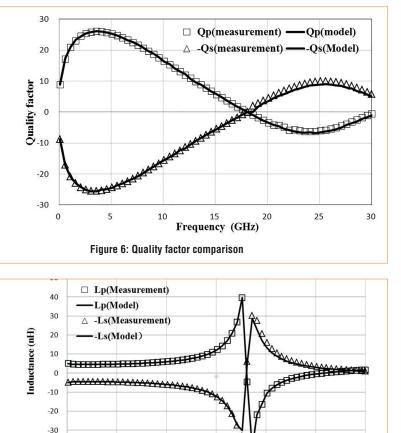

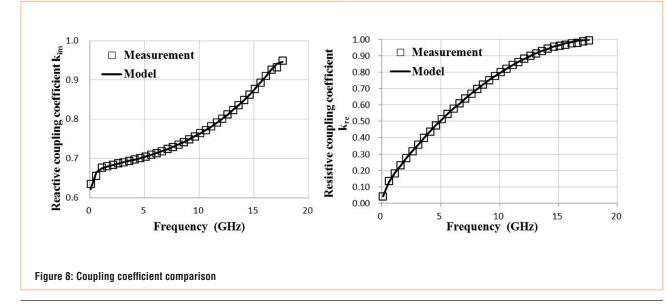

# **38** NEW MODEL FOR ON-CHIP STACKED TRANSFORMERS THAT INCLUDES AN LR AND LRC SERIES BRANCHES

By **Minglin Ma, Yuan Chen** and **Zhijun Li** from Xiangtan University and **Xiangliang Jin** from the Hunan Engineering Laboratory for Microelectronics, Optoelectronics and System On A Chip in Xiangtan, China

Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry – particularly as regards electric shock, fire hazards and explosions.

In embedded system design, reality demands that compromises are made at every phase. Tradeoffs between performance, functionality and cost often prevent you from bringing your best ideas to market. We believe there's a better way. That's why we've architected our latest 8-bit PIC® microcontrollers (MCUs) with flexible, "core independent" blocks of hardware intelligence that react quickly, consume very little power and are much more code-efficient than a software-based approach. In essence, Core Independent Peripherals help you easily combine many complex system functions onto a single MCU, increasing speed and flexibility, while reducing power consumption and cost. Design with 8-bit PIC MCUs, and you won't have to compromise.

# FLEXIBLE MADE EASY 8-BIT PIC<sup>M</sup>MICROCONTROLLERS

# Enable system functions with:

Maximum flexibility

▶ Minimum latency

Reduced cost

TREND • 05

# TRENDS IN INDOOR WIRELESS FOR ENTERPRISE BUILDINGS

Over the last several years, wireless operators have focused on delivering cellular services to the largest public access venues - stadiums, arenas and airports - as there it's all about providing high network capacity to a high concentration of subscribers. In US football stadiums, for example, some operators have deployed distributed antenna systems (DAS) with over 60 sectors for each frequency band. This design delivers plenty of capacity to fans for watching video replays and other data-intensive applications. Future upgrades for adding more capacity and frequency bands will be necessary, but solid foundations for wireless are already in place.

The next frontier for indoor wireless are the mid- and large-size enterprise buildings - office complexes, high-rise apartments and commercial buildings - which are typically privately owned. The challenges of deploying wireless in private venues are significantly different in terms of the customers and channels involved, as well as the technical requirements. The most significant difference is the operators' willingness - or lack thereof - to fund these systems.

The operators recognise they need to invest in wireless for large public venues because their subscribers demand services there. But the return on investment for private enterprises is less certain, so their willingness to fund in-building wireless in private enterprises is not as strong, particularly as they pursue other investments such as new spectrum, acquisitions and network virtualisation.

The enterprises will likely need to invest in equipment themselves. This is a very different model and, overall, there is no consistent process to help enterprises know how to acquire and deploy a system successfully. Even if an enterprise is willing to fund a system, an operator has to provide the radio and backhaul to their network. The process for getting approval differs from one operator to another, making the situation daunting and confusing for many.

This is partly due to private enterprises generally having to deal with IT organisations, not directly with the RF managers from major network operators who are intimately familiar with cellular communications; a significant learning curve stands between these worlds. Enterprises typically have little to no understanding of cellular. They like it no more complicated than Wi-Fi – and, unfortunately, that generally isn't the case. The IT installation companies they know are probably only slightly more knowledgeable about cellular, too.

To remedy this barrier to in-building wireless in the enterprise space, vendors need to provide wireless systems that look and act more like the infrastructure that IT managers

The next frontier for indoor wireless are the midand large-size enterprise buildings – office complexes, high-rise apartments and commercial buildings – which are typically privately owned

know. Many, like CommScope, are doing exactly that. DAS continues to be enhanced to better meet the needs of commercial buildings. Small cells offer a great alternative for cost-effective coverage for enterprises, particularly for single-operator applications with a limited number of frequency bands. Managing interference inside buildings can be challenging, but newer solutions address this issue. The key stakeholders in the enterprise need a bit of a mind-set change, too. Recent research commissioned by CommScope found that just over half (56%) of building managers, facilities managers, real-estate managers and architects consider mobile connectivity for building's tenants as a factor when working on projects. However, almost three quarters (73%) of the same respondents cited it as an 'important' or 'very important' factor.

There is a disconnect here. Building owners and managers have to ensure that tenants are always connected in today's increasingly mobile, data-intensive era, future-proofing the buildings for tomorrow. Better planning for indoor wireless networks, beginning in the earliest design phase, would help ensure adequate wireless coverage and capacity. Deployment in the building construction phase can avoid significant disruption to tenants when systems must be retro-fitted, as well as saving on the associated costs. The sooner architects, building owners and managers start planning for wireless, the easier it is to deliver high-quality, high-bandwidth networks.

This year we expect to see more enterprises start to invest in wireless systems. Early adopters will lead the evolution to a new model where building owners and IT managers take the lead in buying and deploying in-building wireless solutions. DAS and small cells will continue to evolve to support this important market segment. The needs of mobile users in commercial spaces are too great to ignore. The paradigm shift to new funding models and ways of thinking about wireless systems is already underway in North America.

@electrowc

By Matt Melester, Senior Vice President and General Manager for distributed coverage and capacity solutions at CommScope (www.commscope.com)

EDITOR: Svetlana Josifovska Tel: +44 (0)1732 883392 Email: svetlanaj@sjpbusinessmedia.com

SALES: James Corner Tel: +44 (0)20 7933 8985 Email: jamesc@electronicsworld.co.uk

Philip Woolley Tel: +44 (0)20 7933 8989 Email: philipw@sjpbusinessmedia.com

DESIGN: Tania King

PUBLISHER: Wayne Darroch

ISSN: 1365-4675

PRINTER: Buxton Press I td

SUBSCRIPTIONS: Subscription rates 1 year: £65 (UK); £94 (worldwide) Tel/Fax +44 (0)1635 879361/868594 Email: electronicsworld@circdata.com www.electronicsworld.co.uk/subscribe

2nd Floor. 52-54 Gracechurch Street London, EC3V 0EH

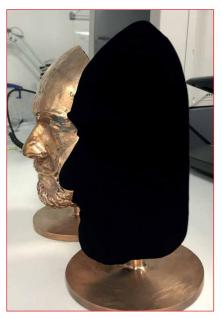

# THE WORLD'S BLACKEST MATERIAL IS NOW AVAILABLE IN SPRAY FORM

Many new applications – including consumer products – can now benefit from the world's blackest surfacecoating material called Vantablack, thanks to an innovative new spray-paint version believed to be the blackest ever created.

Vantablack's nanomaterial structure absorbs virtually all incident light; it was designed to optimize the performance of precision optical systems. Now, the material's developer, UK-based Surrey NanoSystems, has created a version that can be sprayed on to objects, rather than being grown using a chemical vapour deposition (CVD) process.

The new nanomaterial spray-paint is called Vantablack S-VIS, and it greatly widens the range of applications, making it possible to coat much larger and more complex shapes and structures, as well as many new materials, including engineering polymers.

Even though the material is applied using a simple spraying process, it traps 99.8% of incident light hitting its surface. A surface coated with Vantablack S-VIS looks very odd to the human eye, often described by observers as appearing like a two-dimensional gap or "black hole". The only other commercially available material in the world that is darker is the original Vantablack, which set a world record for blackness when it was launched, as it traps 99.965% of incident light in the visible spectrum.

Vantablack was originally developed for aerospace engineering applications, such as satellite-based optics like star trackers and earth observation imaging and calibration systems. It increases the sensitivity of these optical systems by improving the absorption of stray ultraviolet, visible and infrared light. It is some 17 times less reflective than the current super-black paint used on the Hubble space telescope for minimizing stray light.

The active element of the Vantablack S-VIS spray-paint is a carbon nanotube material. The super-black coating is applied using a patented manufacturing and spray-painting process, combined with pre- and post-spray steps developed to produce extreme levels of absorption.

Two 3D masks of a face, one covered in Vantablack S-VIS

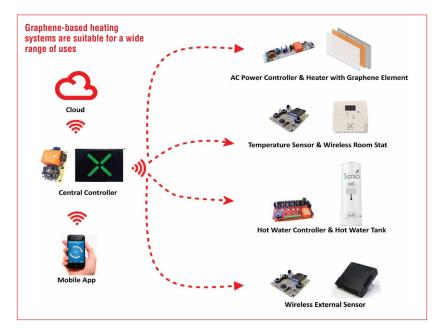

# WORLDS' FIRST GRAPHENE-BASED COMMERCIAL HEATING SYSTEM IS BEING TRIALLED NOW

UK-based technology firm Xefro is the first to use graphene in a commercial heating system. It harnesses a single-atom-thick material for heating elements that offers extremely efficient energy transfer – 100% of electrical energy is converted into heat, with the potential of reducing energy costs up to 70%.

The Xefro intelligent heating system consists of a central heating controller that communicates via RF signals with hot water controllers and various zones, each consisting of a radiator or at least one heating element with AC power controller and temperature sensors. The user interface for the entire system is via a mobile app.

European Circuits Limited (ECL) will design the hardware and software for the system, as well as manufacture it. The system is currently undergoing trials.

# **GRAPHENE PROPERTIES**

- Graphene is suitable for use in heating systems due to several of its properties, including:

- High surface area it generates heat extremely efficiently;

- Low thermal mass it offers instant heat, without any waste;

- High conductivity, since electrons travel at 1/10 the speed of light.

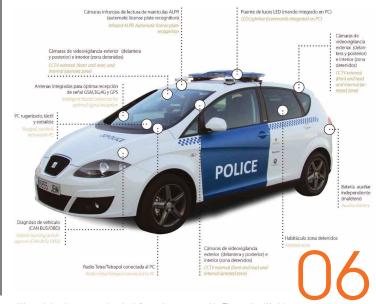

# FICOSA TRANSFORMS POLICE CARS INTO MOBILE POLICE STATIONS

Barcelona-based high-tech connectivity company Ficosa has created the most advanced police car in the world (right), turning it into a mobile police station.

The patrol car's centre console has been equipped with a 10-inch touchscreen laptop, a 3G/4G Telefónica connection for sending images, video and data in real time, and an automatic license plate reader (ALPR), which digitizes and encodes licence plate images, verifying them with a central database. The vehicle also has three video surveillance cameras located at the front and rear of the car and a cabin camera. An integrated antenna system using fractal technology enhances the vehicle's connectivity.

The Connected Police Car project is a collaboration between Ficosa and Telefónica, and is currently in pilot phase, which consists of several such cars being used throughout Spain. After the trial period, up to 200 hightech patrol cars are expected to be introduced to the streets of Spain.

"We have been working on this project for more than three years," said Xavier Pujol, Ficosa's CEO. "The Connected Police Car is an important step in enabling policemen to carry out different procedures without having to be at the police station, as well as offering them new tools to facilitate their work."

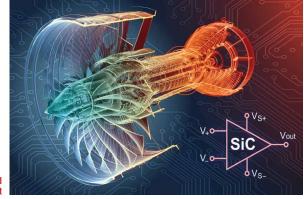

# INDUSTRY AND ACADEMIA TEAM DEVELOPS SIC-BASED ANALOGUE CIRCUIT

Raytheon UK and Newcastle University have produced silicon-carbide-based (SiC) analogue circuitry with op-amp-like characteristics for high-temperature and harsh-environment monitoring applications

"To date, the focus on silicon carbide semiconductors has been power electronics and exploiting the material's ability to dissipate internally-generated heat," said Dr Alton Horsfall, the Reader in Semiconductor Technology at Newcastle University. "For this project we've focused on creating circuitry that can operate in high temperature and other harsh environments. This could lead to condition-monitoring circuitry mounted on gas turbines or within the primary coolant loop of a nuclear reactor, which runs at about 350°C."

At the heart of the circuit is a lateral small-signal Junction Field Effect Transistor (JFET), which offers a significant improvement in reliability in hostile environments due to a lack of a gate oxide layer. This enables greater stability in the threshold voltage and a

### New SiC-based analogue circuit

reduction in intrinsic noise, making these structures ideally suited for the realization of high-temperature, low-noise amplifier circuits. The current circuit is a fully differential, three-stage amplifier, with a source follower final stage, optimised to operate on a  $\pm$ 15V supply.

Modifications enable voltage supplies of  $\pm45\text{V}$  for increased headroom of the circuit.

Laboratory tests have shown the amplifier circuit has an open circuit gain of over 1500 at room temperature. A high temperature gain of 200 has been recorded at 400°C, but this is limited by the passive components used in the circuit. The amplifier was recently monolithically integrated into a single chip.

"We believe this amplifier circuit represents the furthest anyone has gone down the lab-to-fab route. In this instance, it is Newcastle University's design expertise and understanding of harsh environments, combined with our silicon carbide processing expertise, that have the potential to result in the full commercialization of a high-temperature version of a fundamental electronic building block, the humble op-amp," said Phil Burnside, Business Development Manager of Raytheon UK.

# SOLVE DATA ACQUISITION COMPATIBILITY PROBLEMS By Brendan Whelan, Design Manager, Signal Conditioning Products, Linear Technology

odern data acquisition and signal generation systems are both sophisticated and refined. Decades of IC and application development and generations of designs have optimized performance and features, while broadening both. New designs must differentiate from the prior with well-chosen combinations of performance, size, supply range, stability, and more. Simultaneously,

high performance integrated circuits such as DACs, ADCs and voltage references have been pushed to the limit for performance. Concerning the voltage reference, often design choices must be made between precision and features. When highest performance is required, flexibility and compatibility can be lacking.

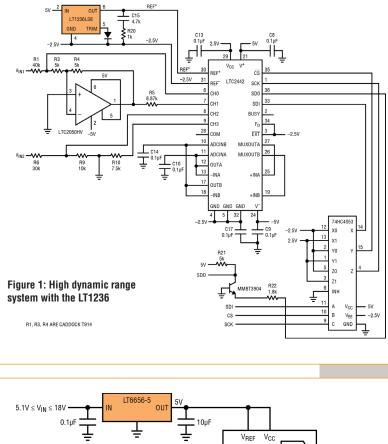

Historically, the highest precision and most stable systems have been designed using deep buried Zener references, as shown in Figure 1. The combination of low drift, high stability and low noise enables systems with both high dynamic range and good stability. However, Zeners are generally not suitable for most new systems. They require significant supply voltage to operate, and many designs are optimized only for particular systems, such as those with greater than 10V supplies, large available board area, and well-understood load impedance. These assumptions are rarely applicable in many new designs. Furthermore, there has been little new development using Zener architectures, so more commonly used reference voltages less than 5V, such as 4.096V, 2.5V and 1.25V, are rare.

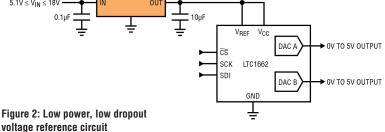

In contrast, bandgap voltage references have long been the best choice for a combination of features and performance. The bandgap architecture, while sacrificing some stability as compared to the Zener architecture, has made it possible to design references with many useful features, including low dropout, wide temperature range, low power, small size, wide operating range and wide load current capability. These features have given rise to a host of high-performance LDO regulators as well as precision voltage references. The relatively low bandgap voltage of approximately 1.2V facilitates the design of products with many output voltages, including 1.25V, 2.048V, 2.5V, 3V, 3.3V, 4.096V, 5V and 10V. It also makes it possible to operate from a supply of only a few millivolts above the output voltage, as in Figure 2.

For voltage references, the largest error is usually the temperature coefficient (TC). For many precision systems, a voltage reference with 20ppm/°C temperature coefficient is appropriate. However, over an industrial temperature range (-40°C to 85°C), this temperature coefficient would give a maximum error of 2500ppm, or 0.25%. By comparison, the error due to the initial accuracy (0.1%), thermal hysteresis (usually around 100ppm) and long-term drift (50ppm/ $\sqrt{(kHr)}$  is small. While sufficient for many industrial and medical systems, precision applications such as test and measurement, as well as wide temperature range automotive applications, demand better stability.

Over time, bandgap performance has improved, and in some cases exceeded buried Zener stability and noise. New architectures, processes and manufacturing techniques have pushed the limits of precision and stability. Where previous "precision" bandgap references might have boasted 20-50ppm/°C temperature coefficient, newer products provide temperature stability of less than 5ppm/°C. Simultaneously, the range of features has been preserved or improved.

Such is the case for the LT6657, a high precision bandgap voltage reference. The LT6657 provides a new alternative, giving highest precision while retaining significant flexibility for a wide array of system requirements and limitations.

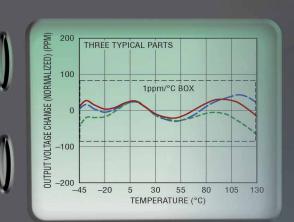

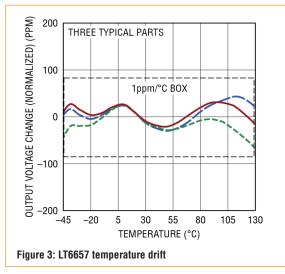

With a temperature coefficient of 1.5ppm/°C, the LT6657 is the lowest temperature coefficient bandgap voltage reference. Highorder temperature compensation keeps the output voltage error low and predictable over temperature (Figure 3), while state of the art manufacturing ensures consistent performance from part to part and lot to lot. To ensure that every device meets this high level of performance, the LT6657's temperature coefficient is guaranteed by 100% five-temperature testing. From -40°C to 125°C, the LT6657 guarantees less than 250 parts per million of error due to temperature drift.

It should be noted that a box is included in Figure 3 to indicate 1ppm°C of error. A typical LT6657 unit fits well within this box, allowing for reasonable yield to the 1.5ppm/°C limit in automated production testing.

Adding to the overall stability are low thermal hysteresis and excellent long-term drift stability. These measures predict how well the system will stay within specification over time and temperature cycles. For systems that are located remotely or difficult to calibrate, lower thermal hysteresis and long-term drift translates to fewer calibration events, saving time and expense. While typical values in the electrical table provide helpful guidance, it is never clear if these represent a mean, a deviation, or a single unit. Linear Technology provides substantial data to give meaningful guidance when designing with voltage references. Long-term drift and hysteresis distribution data is available in the LT6657 data sheet showing that both are low and consistent.

Another aspect of voltage reference performance is noise. Many systems are not sensitive to long-term drifts such as temperature or aging, but require very low noise to enable high-resolution measurements. With the LT6657, noise performance is comparable to some of the best low-noise buried Zener references. At only 0.5ppm, the noise is appropriate for many high dynamic range systems. The LT6657 produces only 1.25 $\mu$ V peak-to-peak noise in 0.1Hz to 10Hz for a 2.5V reference voltage. Wideband noise is also low, at 0.8ppm (2 $\mu$ V) RMS to 1 kHz. The low noise of the device makes it a good candidate for high dynamic range and very low noise systems. To illustrate the importance of this low noise, a 20-bit converter with 5V full-scale input has an LSB of only 4.8 $\mu$ V (~1ppm).

In addition to the low temperature drift, high stability and low noise, the LT6657 adds further features. The LT6657 requires only 50mV of headroom for operation. It is possible to power a 2.5V reference from less than 2.6V with no DC load, or less than 3V with a heavy DC load current. The supply range extends to 40V with less than 1ppm/V of line regulation error and excellent ripple rejection, allowing the flexibility to power the reference from almost any available power supply which is a big differentiator over a Zener reference.

As with most of Linear Technology's recent voltage reference products, the LT6657 exhibits low output impedance over frequency. This reduces the effect of changing load over frequency and helps prevent signals present at the load from backfeeding the reference and causing interference, errors or noise. This feature is critical for reference settling when driving a high performance analog to digital converter (ADC), or surviving operational tests such as bulk current injection in automotive systems. In addition, the LT6657 is designed to drive large output capacitance. Given that many high-performance ADCs draw large charge-injection currents from the voltage reference during sampling, the combination of fast settling and the ability to remain stable by design into a large charge-reservoir capacitor gives this voltage reference an edge in squeezing the best performance from a high dynamic range converter.

The LT6657 also has ample drive capability, and can source and sink up to 10mA of load current, with less than 1ppm per milliamp of load regulation error. This load-driving capability enables the LT6657 to bias a variety of sensors, drive difficult ADC reference inputs, drive multiple ADCs and DACs, or power a small subsystem with reference-grade precision. This littleutilized feature can help a system designer make the most of board area and power dissipation by merging the power and reference functions in some small data acquisition systems. It is ideal when the ADC or DAC uses the same voltage for both power and reference voltages; the small MSOP package of the LT6657 adds to the space-savings. Furthermore, the LT6657 includes current and thermal protection to avoid damage from excessive load during fault conditions.

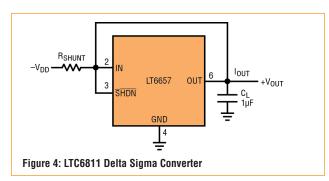

Finally, the LT6657 can operate as a shunt reference. One benefit of shunt-mode operation is the ability to create a negative voltage reference. Shunt mode operation also allows the LT6657 to work from a very high supply voltage or to operate from the lowest possible dropout voltage. Figure 4 shows a positive shunt configuration for the LT6657.

In conclusion, the LT6657 offers high precision, low noise and high stability, combined with the flexibility provided by its

many features. The device's features enable design of a system that is power and area efficient, compatible with a wide range of supply voltages and environmental conditions, and capable of the highest precision, stability and dynamic range. The additional features and performance of this groundbreaking voltage reference, combined with manufacturing quality, make it ideal for many application circuits.

# Linear Technology (UK) Ltd • Tel: 01628 477066 Email: uksales@linear.com • www.linear.com

# Building your own peripherals

BY **LUCIO DI JASIO**, MCU8 BUSINESS DEVELOPMENT MANAGER AT MICROCHIP TECHNOLOGY

uring the Microchip Masters Conference last summer (held annually in the warmth of Phoenix, Arizona), my seven-year-old son Luca and I participated in a father/son event. It was great to work together on a project, developing a simple talking robot – not much more than a PIC board in a cardboard box and a servo to move the lid. We called it the

"Cookie Monster" (see Figure 1). Luca was a bit too young to contribute to the coding part but he provided the key inspiration, recorded the voice of the monster, did an accurate drawing of the assembly and wiring, and decorated it in true 'Sesame Street' style.

It was impressive to see how much excitement a single moving part – the servo – could generate! Luca went on for hours telling everybody about the little monster and making practical demonstrations – eating 'cookies' and even fingers too, in case of slow reflexes.

So, thinking about next year, I figured it could be even more fun teaching an eight-year-old how to build a new robot using two, three, four or even eight or more servos.

I quickly realized though that beside the cost (local shops sell micro servos, like the one we used for the cookie monster, for less than 5 Euros), a limiting factor could be the number of servo channels available on a low-cost PIC microcontroller. In particular, I was planning to again use the MPLAB Xpress cloud IDE so the project could easily be replicated by other father-andson teams in minutes, without lengthy and complex software installations.

The MPLAB Xpress evaluation board (see Figure 2) featuring a PIC16F18855, a 28-pin device loaded with many core independent peripherals, looked like a promising replacement for the previous year's 20-pin prototype.

# Servo Control

In practice, controlling a servo is as simple as generating a PWM signal where the period can be anything between 4ms and 20ms, but it is the  $T_{on}$  time that controls the actual position of the servo actuator; a centre position is usually achieved with  $T_{on}$  of 1.5ms. Increasing the duration up to 2.5ms will produce a rotation of the actuator up to 90 degrees (clockwise), while decreasing it to 0.5ms will produce an opposite (anti-clockwise) 90-degree rotation. Controlling multiple servos then requires just an equal number of PWM modules, all linked to a single timer providing the common period.

The PIC16F18855 has only five Capture Compare and PWM modules (CCP1 through CCP5), I used the PWM function.

There are two more PWM proper modules (PWM6 and PWM7); I am not sure if the odd number was intentionally chosen by the device architect to tease, but it sure felt like a challenge.

### **Home-Made PWM**

One can nowadays find an endless list of examples online illustrating how to produce the servo PWM timing in software by "bit banging" an I/O pin using a timer (optionally an interrupt) and a lot of CPU cycles. But while I will confess doing that in the past, it did feel like a huge waste of the microcontroller resources. Besides, since I was planning to implement a few extra functions (ultrasonic range detection. audio playback, etc.), bit-banging would definitely not be the way to go. It was time to put the core independent peripherals of the PIC16F18855 to work! After all, some of the timers on the device (the even numbered ones) have been enhanced with so-called HLT capabilities. Despite the cryptic acronym - HLT stands for Hardware Limit Timer (as if that made it any clearer) - these new timers can operate automatically as monostable circuits. Instead of simply generating an interrupt as the (8-bit) timer matches the period register value, they can produce an output signal that can be routed directly to a pin or other internal logic. They can also re-arm automatically in sync with other timers via a (re-)trigger input.

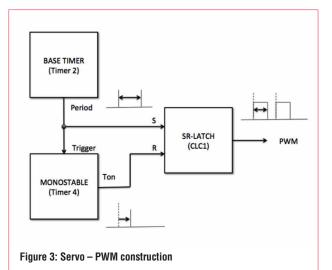

To complete a new PWM module then, all we need is a single flip-flop, a Set Reset or SR-Latch to be precise. Luckily, this is a function already found in the Configurable Logic Cells, of which the PIC16F18855 has no less than four.

Figure 3 illustrates how the three elements: Timer2, HLT (aka Timer4) and the SR-latch combine to form a new PWM module.

### **Quick Configuration With MCC**

Creating a new project using the MPLAB Xpress IDE takes seconds and is as easy as opening a browser, entering the MPLAB Xpress URL: https://mplabxpress.microchipcom and logging in to your own MyMicrochip account.

Thanks to the MPLAB Code Configurator, populating the project with the correct initialization code for the device and all the required peripheral drivers is a matter of minutes and a few mouse clicks. Here's the procedure, step by step:

- Select the System Module configuration.

- Accept the default configuration: 4MHz, internal clock.

- Add sequentially all the CCP and PWM modules to the project resources.

- Add Timer2 and Timer4 to the project resources.

- Add CLC1 to the project resources.

- Configure Timer 2 as the time base for all servo PWMs. This requires selecting the 'Roll Over Pulse' mode and using FOSC/4 as the clock input (see Figure 6).

- Configure Timer4 as a monostable. This requires selecting the monostable mode, selecting the Timer2\_postscaled trigger input and start on rising edge (of the trigger) as the start/stop option (see Figure 7).

- Configure all CCP modules to operate as PWMs with Timer2 as the time base.

- Configure all PWM modules to use Timer2 as the time base.

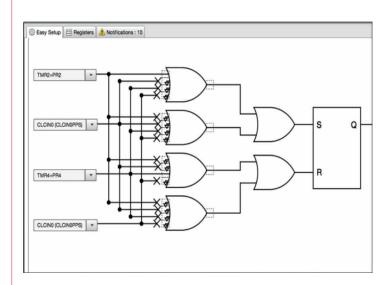

- Configure CLC1 as the SR-Latch and connect the first and the third input gate multiplexers respectively to the Timer2 output and Timer4 output (see Figure 8).

- Select the Pin Manager configuration table and assign all output pins as you see fit. Note that the new PWM will be the output function of CLC1 (see Figures 4 and 5).

The PIC16F18855 has PPS (peripheral pin select), so there's plenty of flexibility on where to connect each servo output function. You can use the mikroBUS connector or simply the external ring of contacts of the MPLAB Xpress evaluation board.

Eventually I decided to add a serial port connection so I could conveniently control all eight servo/PWM outputs from a terminal program. For that you will need to:

- Add the EUSART module to the project resources list.

- Select to the preferred baud-rate for your application (9,600 baud is a good default) and enable the 'continuous receive' function (add the transmit function if you want to receive feedback from the board as well).

• Enable the 'STDIO redirection to the USART' to be able to use the standard C library I/O functions (printf, putch, getch). With the "Generate" button, the MPLAB Code Configurator

will produce the configuration files and place them in the project sources. We are now ready to start focusing on the core of the application.

### In 10 Lines Of Code

The MCC-generated drivers provide the

$\label{eq:pwmx_DutyValueSet() function to control the duty cycle} (T_{_{on}} \, duration) \, of the CCP modules.$

Please note that, as of this writing, MCC rev 3.03 uses a different function-naming convention for the PWM modules, using the PWMx\_LoadDutyValue() instead.

Figure 2: MPLAB Xpress Evaluation board

| Package: | UQFN28   | -   | Pin No:  | 27 | 28 | 1  | 2   | 3   | 4 | 7 | 6 | 18 | 19 | 20 | 21  | 22   | 23 | 24 | 25 | 8  | 9   | 10       | 11  | 12 | 13 | 14 | 15 |

|----------|----------|-----|----------|----|----|----|-----|-----|---|---|---|----|----|----|-----|------|----|----|----|----|-----|----------|-----|----|----|----|----|

|          |          |     |          |    |    |    | POF | T A | • |   |   |    |    |    | POR | RT B | •  |    |    |    | _   |          | POR | TC |    |    |    |

| Module   | Function | D   | irection | 0  | 1  | 2  | 3   | 4   | 5 | 6 | 7 | 0  | 1  | 2  | 3   | 4    | 5  | 6  | 7  | 0  | 1   | 2        | 3   | 4  | 5  | 6  | 7  |

| CCP1     | CCP1     | out | tput     |    |    |    |     |     |   |   |   | î. | â  | î. | î.  | ì    | î. | ì. | Ъ  | î. | î.  | <b>ì</b> | 6   | ĵ. | î. | î. | î  |

| CCP2     | CCP2     | out | tput     |    |    |    |     |     |   |   |   | î. | î. | â  | ì   | ì    | Ъ  | ì. | Ъ  | î  | î.  | î.       | î.  | î. | ì  | ì  | ì  |

| CCP3     | CCP3     | out | tput     |    |    |    |     |     |   |   |   | Ъ  | Ъ  | Ъ  | â   | î.   | Ъ  | Ъ  | Ъ  | ĥ  | ĵu. | î.       | Ъ   | 6  | 'n | î. | î  |

| CCP4     | CCP4     | out | tput     |    |    |    |     |     |   |   |   | î. | î. | Ъ  | î.  | â    | ъ  | Ъ  | 6  | î. | î.  | î.       | 1   | Ъ  | î. | î. | Ъ  |

| CCP5     | CCP5     | out | tput     | î. | Ъ  | Ъ  | ì.  | 6   | Ъ | Ъ | Ъ |    |    |    |     |      |    |    |    | î. | ĵ.  | ì        | ì   | î. | â  | î. | î. |

| CLC1     | CLC1OUT  | out | tput     | 2  | ъ  | î. | 2   | 2   | 2 | 1 | 3 |    |    |    |     |      |    | 1  |    | î. | î.  | â        | 3   | 3  | î. | 3  | ъ  |

Figure 4: MCC pin manager

| Pin Na▲ | Module | Function | Custom Name | Start High | Analog | Output       | WPU          |

|---------|--------|----------|-------------|------------|--------|--------------|--------------|

| RA7     | CLC1   | CLCIN1   | RA7         |            |        |              | $\checkmark$ |

| RA7     | CLC1   | CLCIN0   | RA7         |            |        |              | $\checkmark$ |

| RA7     | TMR2   | T2IN     | RA7         |            |        |              | $\checkmark$ |

| RB1     | CCP1   | CCP1     | PWM1        |            |        | $\checkmark$ |              |

| RB2     | CCP2   | CCP2     | PWM2        |            |        | $\checkmark$ |              |

| RB3     | CCP3   | CCP3     | PWM3        |            |        | $\checkmark$ |              |

| RB4     | CCP4   | CCP4     | PWM4        |            |        | $\checkmark$ |              |

| RB7     | CLC1   | CLCIN3   | RB7         |            |        |              | $\checkmark$ |

| RB7     | CLC1   | CLCIN2   | RB7         |            |        |              | $\checkmark$ |

Figure 5: Pin module configuration

Eventually, our eighth PWM will be controlled via the Timer4 period register, accessible via the TMR4\_LoadPeriodRegister() function.

Since the original PWM functions assume a 10-bit input value, while the Timer4 period is only an 8-bit value, we can achieve an identical control function by simply shifting left by two positions the same control value as shown in Listing 1.

#include "mcc\_generated\_files/mcc.h"

```

void main(void)

uint8_t i, duty[8];

SYSTEM_Initialize();

while (1) // main loop

{

if (getch() != '\02') // start of text

```

continue;

for (i=0; i<8; i++) duty[i] = getch();

// values from 32 to 156 correspond to 0 to 180deg

```

if (getch() == '\03') { // end of text

putch('\06'); // ack

PWM1_DutyValueSet(duty[0]<<2);</pre>

PWM2_DutyValueSet(duty[1]<<2);</pre>

PWM3_DutyValueSet(duty[2]<<2);</pre>

PWM4_DutyValueSet(duty[3]<<2);</pre>

PWM5_DutyValueSet(duty[4]<<2);</pre>

PWM6_LoadDutyValue(duty[5]<<2);</pre>

PWM7_LoadDutyValue(duty[6]<<2);</pre>

TMR4_LoadPeriodRegister(duty[7]);

}

}

}}

Listing 1: Displaying the pattern for digit '1' side by side

```

{

As you can see from the top of the main loop, I have opted for implementing a very (very!) simple serial communication protocol with the MPLAB Xpress board. A 'Start of Text' (ASCII 0x02 or CTRL-B) character is used to prefix a string of eight characters, interpreted directly as T<sub>on</sub> values. A space (ASCII 0x20) will correspond to a maximum-left position. Upper-case alphabetical characters will produce increasingly larger rotations to the right. Lower-case alphabetical characters will rotate even farther to the right and so on. An 'End of Text' (ASCII 0x03 or CTRL-C) character is expected to terminate the string that is eventually acknowledged sending back the Ack (ASCII 0x06 or CTRL-F) value.

Build the project and program the MPLAB Xpress evaluation board using the 'Make and Program' button from the MPLAB Xpress IDE toolbar.

If all's well, you'd be able to immediately verify the presence of a default 50%-duty-cycle PWM signal on each chosen output pin. Any connected servo will position itself to a mid-right position.

By connecting a terminal to the MPLAB Xpress virtual communication port and playing with the command strings you can test the effectiveness of all eight modules.

For example, enter the following string on your terminal:

CTRL-B A B C D E F G H CTRL\_C

The Xpress board with reply with:

# CTRL-F

This should position all eight servos at slightly increasing angles (1.4-degrees apart), starting from approximately 45 degrees from the left-most position.

### In Closing

Adding an eighth PWM module is quite simple. The question then becomes: where is the limit? Can we do nine, ten, perhaps twelve PWMs?

I'll leave you with this challenge in the assumption that you will try to use the many more timers (2x SMT, 2x HLT, NCO...) and configurable logic cells available to create even more interesting core-independent solutions.

The new PWM module we just assembled has the right resolution and uses no additional CPU cycles, leaving all the processing power of the PIC core available for other tasks the little robot will need to perform this summer.

Stay tuned. ●

| Enable Time  | er               |   |                    |                  |                               |            |

|--------------|------------------|---|--------------------|------------------|-------------------------------|------------|

| Timer Clock  |                  |   | Timer Period       |                  |                               |            |

| Clock Source | FOSC/4           | - | Timer Period       | 16 us ≤          | 4.096 ms                      | ≤ 4.096 ms |

| Postscaler   | 1:1              | * | Actual Period 4.0  | 96 ms (Period    | calculated via PR Register vi | alue)      |

| Prescaler    | 1:4              | - | Ext Reset Source   | T2CKIPPS pin     | *                             |            |

| Polarity     | Rising Edge      | * | Control Mode       | Roll over pulse  | *                             |            |

| Enable Pr    | escaler O/P Sync |   | Start/Reset Option | Software control | -                             |            |

| Enable Cl    | ock Sync         |   |                    |                  |                               |            |

| Enable Time  | er Interrupt     |   | -                  |                  |                               |            |

Figure 6: Timer2 configuration

|              | gs               |   |                    |                     |                        |         |            |

|--------------|------------------|---|--------------------|---------------------|------------------------|---------|------------|

| Enable Time  | ər               |   |                    |                     |                        |         |            |

| Timer Clock  |                  |   | Timer Period       |                     |                        |         |            |

| Clock Source | FOSC/4           |   | Timer Period       | 16 us ≤             | 2.048 ms               |         | ≤ 4.096 ms |

| Postscaler   | 1:1              |   | Actual Period 2.0  | 48 ms (Perio        | d calculated via Timer | Period) |            |

| Prescaler    | 1:4              | * | Ext Reset Source   | TMR2_postscaled     | í .                    |         |            |

| Polarity     | Rising Edge      | * | Control Mode       | Monostable          |                        | *       |            |

| Enable Pr    | escaler O/P Sync |   | Start/Reset Option | Starts on rising ec | ge on TMR4_ers         |         |            |

| Enable Cl    | ock Sync         |   |                    |                     |                        |         |            |

| Enable Time  | er Interrupt     |   |                    |                     |                        |         |            |

|              |                  |   |                    |                     |                        |         |            |

Figure 7: Timer4 configuration

Figure 8: CLC1 configuration

# Using pyroelectric sensors in embedded applications

# BY DR DOGAN IBRAHIM, PROFESSOR AT THE NEAR EAST UNIVERSITY, CYPRUS

yroelectric sensors are also known as 'passive infrared' sensors – PIR for short, or presence detectors; they detect thermal radiation.

Infrared radiation has wavelengths longer than visible light but shorter than microwaves. When objects generate heat they also generate infrared radiation. Although this radiation

cannot be seen, it can be detected easily using transducers to convert the infrared signal to detectable voltage. Humans emit infrared radiation at a wavelength of 10µm at normal body temperature.

# **Pyroelectric Detectors**

Pyroelectric is not same as thermoelectric. In a thermoelectric device (e.g. a thermocouple), voltage is generated at a junction of dissimilar metals at different temperatures. In a pyroelectric device a surface charge is generated when the device is exposed to infrared radiation; the amount of charge depends on the amount of radiation hitting the device surface. In short, whenever there is a change in infrared radiation striking the detector, there is a voltage generated at the detector terminals.

Pyroelectric detectors will only respond to changes in incoming radiation levels. These detectors are capable of sensing IR sources, their size, temperature, direction of motion, speed of movement, wavelength and emissivity.

A pyroelectric detector is made of infrared sensitive crystalline material such as lithium tantalite deposited on both faces of the detector; it's easy to think of the pyroelectric detector as a flatplate capacitor. In practical detectors an FET is used as a buffer, and a shunt resistor is used to convert the FET current to output voltage, which is then amplified to useful levels. In addition, since the detector is sensitive to wide range of radiation, a filter window is added to make the detector more sensitive to human detection.

In practise, dual- or quad-element detectors are used to detect the direction of movement and also eliminate environmental noise and thus increase the sensitivity. In a two-element detector both elements detect the same amount of IR from the walls, doors, etc. When the body of a person or animal passes by, one element detects this and causes a positive differential change. When the person leaves, the reverse happens, resulting in a negative differential change. Additionally, a plastic plano-convex Fresnel lens is added to the front of the PIR detector, with its focal length chosen to increase the sensitivity to human body radiation (8-14 $\mu$ m, strongest at 9.4 $\mu$ m). The Fresnel lens provides a wider field of view to the sensor.

Figure 1 shows the internal structure of a typical pyroelectric

detector housed in a metal can.

In addition to tracking movements of people and animals, some other common application areas for PIR detectors include automatic building light and door control, flame detection, thermal imaging, infrared-based missile guidance systems, medical applications, industrial control for heat leakages, gas detection and pollution monitoring and IP cameras.

# **Advantages And Disadvantages**

Pyroelectric detectors have traditionally been sensitive to ambient light reflections, such as those from bright-coloured objects and strong ambient light sources (direct sunlight, for example).

In general, the advantages and disadvantages of these detectors can be summarized as follows:

# **Advantages**

- Low power consumption;

- Low cost;

- Small size;

- Easy to set up and use;

- Compatible to microcontroller interfacing;

- Easy human or animal detection.

# Disadvantages

- Sensitive to strong ambient light;

- · Sensitive to unwanted sources of thermal radiation;

• Short detection range;

- Insensitive to stationary objects;

- Narrow sensor field of view.

# **Microcontroller-Based Example**

A microcontroller-based wireless pyroelectric detector system is easily designed using standard off-the-shelf components. In this application the system detects the presence of someone in a room and sends signals to a remote station to activate the lights in that room for a pre-set time, using a relay. After this time the lights automatically turn off.

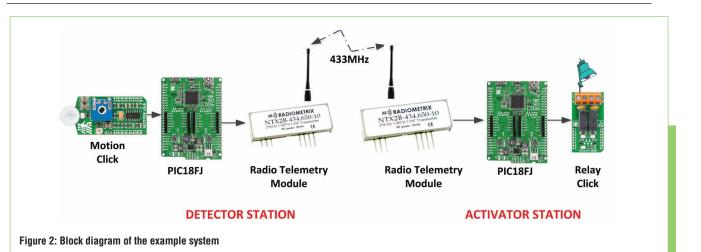

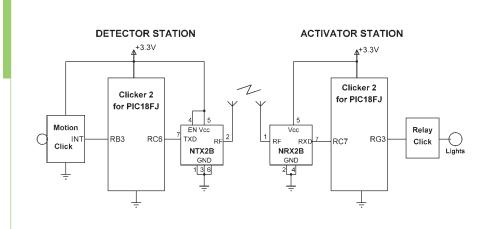

As shown in Figure 2, the system has two parts: detector station and activator station. At the detector station there is a small PIR detector

board with its output fed to a microcontroller development board. An RF transmitter module then receives commands from the microcontroller and sends them to the receiver at the activator station. There's another microcontroller development board at this station that is connected to lights in a room. Once a movement is detected inside the room, upon receiving a command, the lights turn on for two minutes. After this time they turn off automatically, ready for the next activation.

In other applications the lights can be replaced by other devices, such as alarm generators for example.

### **The Hardware**

Figure 3 shows the system's circuit diagram. A Motion Click board from mikroElektronika is used as a PIR detector. This board carries a PIR500B pyrometer sensor and a BISS0001 IC that generates a logic pulse when exposed to infrared light. The duration of this pulse can be set by external resistor and capacitor pair.

The maximum range of the sensor is up to four metres, although an on-board potentiometer can be used to adjust the detection range (some industrial sensors have ranges over 10m). In this example, the output of the Motion Click board (INT) is connected to pin RB3 of the development board.

Any type of microcontroller can be used in this design since

### Figure 3: System circuit diagram

the processing speed, memory requirements or I/O pin numbers are not limiting factors. In this design, a Clicker 2 for PIC18FJ (Figure 4) type microcontroller development board (based on the PIC18F87J50 microcontroller operating at 8MHz) is used, with the Motion Click board plugged-in to mikroBUS socket 1 on the detector side. On the activator side, a Relay Click board is connected to mikroBUS socket 1 of a similar development board. The output of the development board (RG3) is connected to the Relay Click board. The lights to be controlled are connected to the relay terminals. The click boards are powered from the development boards.

The NTX2B transmitter (Figure 5) and compatible NRX2B receiver (Figure 6) modules are also used in this design.

Readers should note that other communications technologies such as Wi-Fi, Bluetooth, ZigBee, etc, can also be used in wireless pyroelectric projects. The choice depends on factors such as cost, reliability, security and ease of use.

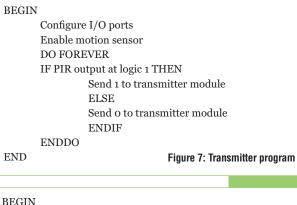

# **The Software**

The software in this example is based on the mikroC Pro for PIC language. Figure 7 shows detector station operation as a program description language. Here, after configuring the input-output ports, the motion sensor is enabled and the program enters a loop, inside which the output voltage of the PIR detector is checked

# Trying to keep a low profile?

Ranging from 40W to 112.5W with convection cooling and up to 225W with forced air cooling. Relec Electronics has a range of open frame ac dc power supplies on a 4" x 2" footprint with a height profile of just 25.4mm for those designs where a low profile is critical. All feature high efficiency with low standby power consumption and a universal ac input. Single fixed outputs range from 12 to 48Vdc on the lower power units and 12 to 58Vdc on the 112.5/225W unit.

Approved to IEC, EN, UL 60950-1 2nd edition, class II safety standards, the 40W & 60W PSU's have an optional function ground enabling them to meet class I when this is connected. Hold up time is between 10 and 16ms; the outputs are fully protected against over voltage and short circuits.

These power supplies are ideally suited for telecom, datacom and a wide range of industrial applications. For further information on the 40W MPE-S040, 60W MPE-T060 or 112.5/225W ABC225 series, view the Relec website or contact us directly.

# POWER DISPLAYS EMC

# www.relec.co.uk

Tel: 01929 555800 e-mail: sales@relec.co.uk

Figure 4: Clicker 2 for PIC18FJ development board

Figure 5: NTX2B transmitter module

Figure 6: NRX2B receiver module

and a signal sent to the transmitter module if a movement is detected. This process is repeated continuously.

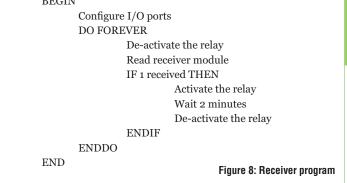

The operation and transmitter programs are similar; see Figure 8. The input-output ports are configured at the beginning of the program. The main program loop is executed endlessly, inside of which the output of the receiver module is checked and the relay activated if a valid command is received from the transmitter module. The relay stays energised for two minutes. After this time, the relay automatically releases so the system is ready for the next activation.

For further details of our extensive product range please call or email us on: T +44 (0)20 8905 7273 E sales@olson.co.uk www.olson.co.uk

# NEW FPGA DESIGN METHODOLOGY ALLOWS SOFTWARE ENGINEERS TO BUILD HIGH-PERFORMANCE COMPUTING ENGINES, USING FAMILIAR TOOLS AND TECHNIQUES. BY **STEPHANE MONBOISSET**, MARKETING AND BUSINESS DEVELOPMENT DIRECTOR AT PLDA GROUP

ooming demand for data services in cloud-based storage and analytics is driving computing loads that are beyond the capabilities of conventional CPUs. Current CPUs' limited capacity for parallelisation means having to add extra processors and more virtual machines, driving costs and power consumption

to unacceptable levels. However, data-centre equipment manufacturers already know that massive parallelism is possible with field programmable gate arrays (FPGAs), which will help achieve the processing performance and I/O bandwidth needed to keep pace with such demands and within a highly efficient power

budget. Traditionally, however, implementing a hardware computing platform in an FPGA has been a complex challenge.

# **Moving On To Software**

Although some recent FPGA-design methodologies incorporating High-Level Synthesis (HLS) tools and software

programming languages such as OpenCL, C and C++ have simplified the task, they have not eliminated the need for specialist FPGA-design expertise. There is need for high-level workflow that enables software engineers to use the FPGA as a software-defined computing platform, without the pain of hardware design. Hence, such a workflow should be able to:

- 1. Create functional hardware from pure software code;

- 2. Incorporate existing hardware IP blocks if needed;

- Infer and create all of the support hardware (interfaces, control, clocks, etc.);

- Support the use of commercial, off-the-shelf (COTS) boards and custom platforms;

- 5. Eliminate hardware debug by ensuring the generated hardware is correct;

- 6. Support debug of functional blocks using standard software debug tools only.

Consider a software algorithm comprising two basic functions:

Traditionally, se menting a hardware as uting platform in an FPGA a a cen a complex challence th

data is processed into one function and then sent to another for further processing. From a software perspective, this implementation is as simple as a call to Function1(), followed by a separate call to Function2() using pointers to the location of the data to be processed.

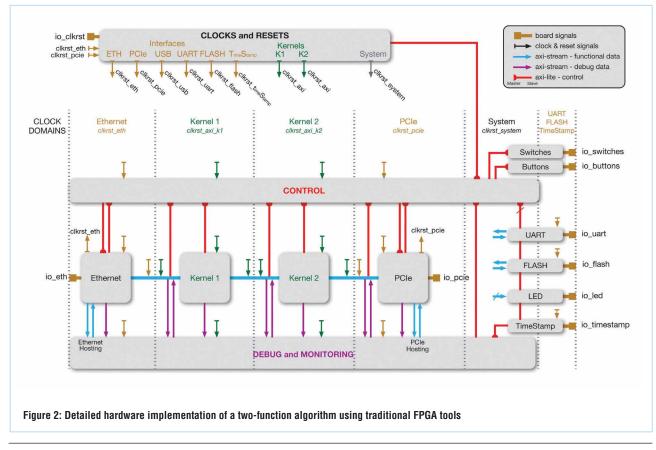

Implementing such an algorithm on an FPGA-based hardware platform without the

right hardware abstraction tool flow would require the software developer to come up with a hardware design resembling that in Figure 2, where Kernel 1 and Kernel 2 are the respective hardware implementations of Function 1 and Function 2.

The hardware design would need to include both control and data planes. The control plane is the execution engine that generates clocks and resets, manages system startup, orchestrates data plane operations and performs housekeeping functions. The data plane instantiates and connects the processing elements, Kernel 1 and Kernel 2, as well as the necessary I/O interfaces required to read data in and write processed data out. In the example shown in Figure 2, those interfaces are Ethernet and PCI Express (PCIe).

May 2016

### **Familiar Challenges**

A software developer without specific hardware expertise could generate Kernel 1 and Kernel 2, using a high-level synthesis tool such as Xilinx's Vivado HLS to compile the software functions Function1() and Function2() as written in C or C++ into FPGA hardware descriptions in VHDL or Verilog. However, the non-algorithmic elements of the design, such as interfaces, control, clocks and resets cannot be generated with HLS tools. Hardware designers would need to create these as custom hardware description language functions or IP. The job of sourcing those elements and connecting them poses yet another challenge, as some elements may not be readily available or may have different types or sizes of interface, as well as different clocking requirements, specific startup sequences and so on.

Implementing the design presents equally tough challenges. These include mapping the design onto the resources of the selected FPGA platform, generating the appropriate constraints and confirming that those constraints are met after logic synthesis and implementation on the FPGA hardware. An experienced hardware designer has been known to take weeks to achieve even the simplest design of a new piece of FPGA hardware.

### **New Approach**

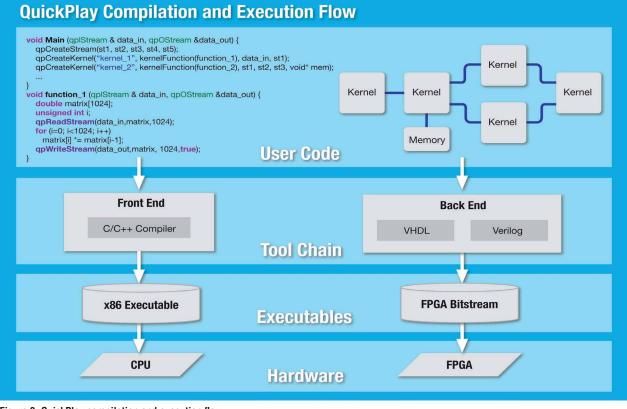

PLDA Group, a developer of embedded IP, has created QuickPlay to allow software developers to accomplish these tasks and, hence, implement applications intended for CPUs, partially or fully, on FPGA hardware. In this software-centric methodology, the designer first develops a C/C++ functional model of the hardware engine and then verifies the functional model with standard C/C++ debug tools. The target FPGA platform and I/O interfaces (PCIe, Ethernet, DDR, QDR, etc.) are then specified and the hardware engine compiled and built.

For this process to work seamlessly, the generated hardware engine must be guaranteed to function identically to the original software model. This means the model must be deterministic, in order to yield the same results as the hardware, however fast that hardware implementation may run. Unfortunately, most parallel systems suffer from non-deterministic execution. Multithreaded software execution, for example, depends on the CPU, on the OS and on unrelated processes running on the same host. Multiple runs of the same multithreaded program can have different behaviours.

Such non-determinism in hardware would require debugging the hardware engine itself, at the electrical waveform level. This would defeat the purpose of a tool aimed at software developers, but QuickPlay's dataflow model guarantees deterministic execution regardless of the execution engine. The model consists of concurrent functions, called kernels, communicating with streaming channels, which correlates well with how a software developer might sketch an application on a whiteboard. The contents of any kernel can be arbitrary C/C++ code, third-party IP, or even HDL code.

The QuickPlay design flow is straightforward as shown in Figure 3.

# **The Design Flow**

- 1. **Stage 1:** Pure software design. The FPGA design is created by adding and connecting kernels in C and specifying the communication channels, using the host development software. The QuickPlay IDE provides a C/C++ library and API to create kernels, streams, streaming ports and memory ports, and to read and write to and from streaming ports and memory ports.

- 2. **Stage 2:** Functional verification ensures that the software model works correctly. The model is compiled on the desktop and executed with a test program that sends data to the inputs, verifying the correctness of the outputs.

- 3. **Stage 3:** The FPGA hardware is then generated from the software model. At this stage the target FPGA, and also the physical interfaces and protocols to map to the design input and output ports, are selected using simple drop-down menus.

- 4. **Stage 4:** System execution is similar to functional verification, except that the FPGA design runs on the selected FPGA board, while the host application still runs in software. Real data can be streamed in and out of the FPGA board. Many more tests can be run at this stage than during functional verification.

- 5. **Stage 5:** System debug. Debugging at the hardware level is never necessary, even if a bug is discovered after executing a function in hardware, because QuickPlay guarantees functional equivalence between the software model and hardware implementation. Thus any bug in the hardware version also exists in the software version.

6. **Stage 6:** (Optional) Optimization. While the entire infrastructure built by QuickPlay is highly efficient in terms of performance and utilization, the overall quality of the design will depend on the quality of the user-created kernels. As generic C code will not produce the most efficient hardware implementation, there are a few techniques and guidelines that software developers can follow to greatly improve the efficiency of the HLS generated code. Further optimization can also be done by using Xilinx Vivado HLS or by recoding certain kernels in HDL.

This simple methodology opens up FPGA-based computing to a large segment of software engineers, who can now do their modelling in software, using familiar techniques, then build the system and test in hardware. No other tool has taken this approach as far and offers a framework where software engineers can design and debug exclusively at the source level.

The efficiency of the hardware generated also makes QuickPlay a great tool for hardware engineers to save weeks or months of design effort by letting QuickPlay take care of the mundane hardware design tasks, while they concentrate on their true value add: the processing kernels.

QuickPlay's dataflow model of computation makes it ideal for a large number of FPGA applications, whether for pure CPU co-processing, pre- or post-processing of acquired data by a CPU, or simply in systems with no CPU involved, for example in applications such as networking, broadcast, vision, medical, wireless and more.

# Figure 3: QuickPlay compilation and execution flow

HP 34401A Digital Multimeter 6 ½ Digit

HP 54600B Oscilloscope Analogue/Digital Dual Trace 100MHZ

| LAMBDA GENESYS       | PSU GEN100-15 100V 15A Boxed As New              | £325      |

|----------------------|--------------------------------------------------|-----------|

| LAMBDA GENESYS       | PSU GEN50-30 50V 30A                             | £325      |

| HP34401A             | Digital Multimeter 6.5 digit                     | £275-£325 |

| HP33120A             | Function Generator 100 microHZ-15MHZ             | £260-£300 |

| HP53131A             | Universal Counter 3GHZ Boxed unused              | £500      |

| HP53131A             | Universal Counter 225MHZ                         | £350      |

| HP54600B             | Digital Oscilloscope 100MHZ 20MS/S               | from £75  |

| IFR 2025             | Signal Generator 9kHz - 2.51GHZ Opt 04/11        | £900      |

| Marconi 2955B        | Radio Communications Test Set                    | £800      |

| R&S APN62            | Syn Function Generator 1HZ-260KHZ                | £195      |

| Fluke/Philips PM3092 | Oscilloscope 2+2 Channel 200MHZ Delay etc        | £250      |

| HP3325A              | Synthesised Function Generator                   | £195      |

| HP3561A              | Dynamic Signal Analyser                          | £650      |

| HP6032A              | PSU 0-60V 0-50A 1000W                            | £750      |

| HP6622A              | PSU 0-20V 4A Twice or 0-50V 2A Twice             | £350      |

| HP6624A              | PSU 4 Outputs                                    | £350      |

| HP6632B              | PSU 0-20V 0-5A                                   | £195      |

| HP6644A              | PSU 0-60V 3.5A                                   | £400      |

| HP6654A              | PSU 0-60V 0-9A                                   | £500      |

| HP8341A              | Synthesised Sweep Generator 10MHZ-20GHZ          | £2,000    |

| HP83731A             | Synthesised Signal Generator 1-20GHZ             | £1,800    |

| HP8484A              | Power Sensor 0.01-18GHZ 3nW-10uW                 | £75       |

| HP8560A              | Spectrum Analyser Synthesised 50HZ - 2.9GHZ      | £1,250    |

| HP8560E              | Spectrum Analyser Synthesised 30HZ - 2.9GHZ      | £1,750    |

| HP8563A              | Spectrum Analyser Synthesised 9KHZ-22GHZ         | £2,250    |

| HP8566B              | Spectrum Analsyer 100HZ-22GHZ                    | £1,200    |

| HP8662A              | RF Generator 10KHZ - 1280MHZ                     | £750      |

| Marconi 2022E        | Synthesised AM/FM Signal Generator 10KHZ-1.01GHZ | £325      |

| Marconi 2024         | Synthesised Signal Generator 9KHZ-2.4GHZ         | £800      |

| Marconi 2030         | Synthesised Signal Generator 10KHZ-1.35GHZ       | £750      |

| Marconi 2305         | Modulation Meter                                 | £250      |

| Marconi 2440         | Counter 20GHZ                                    | £295      |

| Marconi 2945         | Communications Test Set Various Options          | £2,500    |

| Marconi 2955         | Radio Communications Test Set                    | £595      |

| Marconi 2955A        | Radio Communications Test Set                    | £725      |

| Marconi 6200         | Microwave Test Set                               | £1,500    |

| Marconi 6200A        | Microwave Test Set 10MHZ-20GHZ                   | £1,950    |

| Marconi 6200B        | Microwave Test Set                               | £2,300    |

| Marconi 6960B with   | 6910 Power Meter                                 | £295      |

|                      |                                                  |           |

MARCONI 2955B Radio Communications Test Set FLUKE/PHILIPS PM3092 Oscilloscope 2+2 Channel 200MHZ Delay TB, Autoset etc

| Tektronix TDS3012<br>Tektronix 2430A<br>Tektronix 2465B<br>Cirrus CL254 | Oscilloscope 2 Channel 100MHZ 1.25GS/S<br>Oscilloscope Dual Trace 150MHZ 100MS/S<br>Oscilloscope 4 Channel 400MHZ<br>Sound Level Meter with Calibrator | £450<br>£350<br>£600<br>£40 |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Farnell AP60/50<br>Farnell H60/50                                       | PSU 0-60V 0-50A 1KW Switch Mode<br>PSU 0-60V 0-50A                                                                                                     | £195<br>£500                |

| Famell B30/10                                                           | PSU 30V 10A Variable No Meters                                                                                                                         | £300<br>£45                 |

| Farnell B30/20                                                          | PSU 30V 20A Variable No Meters                                                                                                                         | £75                         |

| Farnell XA35/2T                                                         | PSU 0-35V 0-2A Twice Digital                                                                                                                           | £75                         |

| Farnell LF1                                                             | Sine/sq Oscillator 10HZ-1MHZ                                                                                                                           | £45                         |

| Racal 1991                                                              | Counter/Timer 160MHZ 9 Digit                                                                                                                           | £150                        |

| Racal 2101                                                              | Counter 20GHZ LED                                                                                                                                      | £295                        |

| Racal 9300                                                              | True RMS Millivoltmeter 5HZ-20MHZ etc                                                                                                                  | £45                         |

| Racal 9300B                                                             | As 9300                                                                                                                                                | £75                         |

| Black Star Orion                                                        | Colour Bar Generator RGB & Video                                                                                                                       | £30                         |

| Black Star 1325                                                         | Counter Timer 1.3GHZ                                                                                                                                   | £60                         |

| Ferrograph RTS2                                                         | Test Set                                                                                                                                               | £50                         |

| Fluke 97                                                                | Scopemeter 2 Channel 50MHZ 25MS/S                                                                                                                      | £75                         |

| Fluke 99B                                                               | Scopemeter 2 Channel 100MHZ 5GS/S                                                                                                                      | £125                        |

| Gigatronics 7100                                                        | Synthesised Signal Generator 10MHZ-20GHZ                                                                                                               | £1,950                      |

| Panasonic VP7705A                                                       |                                                                                                                                                        | £60                         |

| Panasonic VP8401B                                                       | TV Signal Generator Multi Outputs                                                                                                                      | £75                         |

| Pendulum CNT90                                                          | Timer Counter Analyser 20GHZ                                                                                                                           | £750                        |

| Seaward Nova                                                            | PAT Tester                                                                                                                                             | £95                         |

| Solartron 7150                                                          | 6 1/2 Digit DMM True RMS IEEE                                                                                                                          | £65                         |

| Solartron 7150 Plus                                                     | as 7150 plus Temp Measurement                                                                                                                          | £75                         |

| Solatron 7075                                                           | DMM 7 1/2 Digit                                                                                                                                        | £60<br>£600                 |

| Solatron 1253                                                           | Gain Phase Analyser 1mHZ-20KHZ<br>PSU 0-35V 0-2A 2 Meters                                                                                              | £600<br>£30                 |

| Tasakago TM035-2                                                        |                                                                                                                                                        | £30<br>£160-£200            |

| Thurlby PL320QMD<br>Thurlby TG210                                       | PSU 0-30V 0-2A Twice<br>Function Generator 0.002-2MHZ TTL etc Kenwood Badged                                                                           | £160-£200<br>£65            |

|                                                                         | Function Generator 0.002-200 E TTL etc Kenwood Bauged                                                                                                  | 100                         |

|                                                                         |                                                                                                                                                        |                             |

# STEWART OF READING

17A King Street, Mortimer, near Reading, RG7 3RS Telephone: 0118 933 1111 Fax: 0118 9331275 USED ELECTRONIC TEST EQUIPMENT Check website www.stewart-of-reading.co.uk

Innovation in a 🕀

compact package

# SMALLER - LIGHTER - FASTER

ODU AMC High-Density is a robust miniature connector series that fulfills all the demands of the modern military equipment. The compact and lightweight connector solutions offer an excellent transmission performance, easy handling and high reliability.

- 🔒 Break-Away for maximum safety

- 😌 2 up to 40 contacts

- Watertight protection class IP 68

- 🕀 USB 2.0 + USB 3.0 data transfer

- 🕂 🕞 > 5,000 mating cycles durability

ODU-UK Ltd. Phone: +44 1509 266433 sales@odu-uk.co.uk www.odu-uk.co.uk

A PERFECT ALLIANCE.

# GETTING THE MOST OUT OF PERIPHERALS

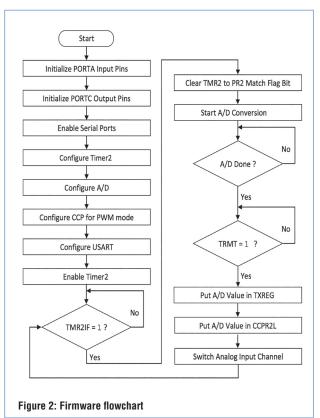

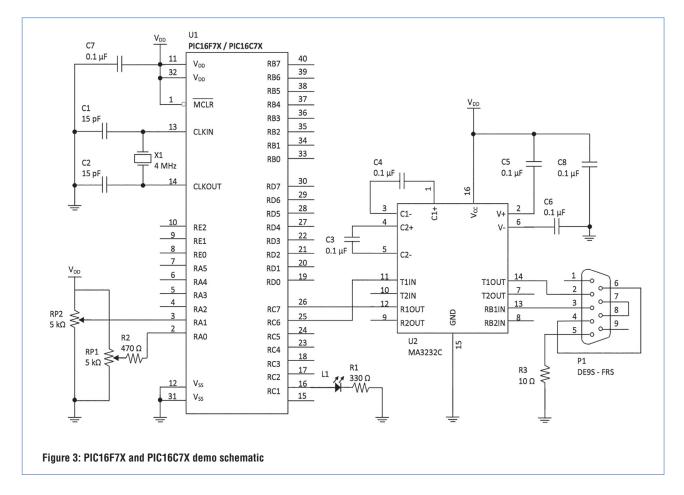

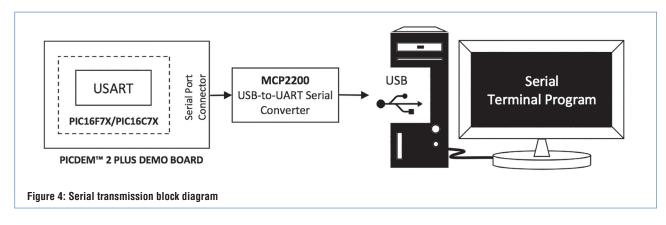

MARK PALLONES, TEAM LEAD AT MICROCHIP TECHNOLOGY, DISCUSSES HOW TO CONFIGURE AND INTEGRATE PERIPHERALS ON 8-BIT MID-RANGE MICROCONTROLLERS

o get the most out of modern microcontrollers, it is necessary to ensure that its peripherals are properly configured. Sometimes this involves configuring them one step at a time before putting them together. This is particularly important when the microcontroller is chosen

because its peripherals match the application; without care, the peripherals may not provide the desired output.

As an example, look at the PIC16F7X and PIC16C7X families of 8-bit mid-range microcontrollers from Microchip. The PIC16F7X is a flash device and the PIC16C7X is a onetime-programming (OTP) device. The peripherals for both devices include an analogue-to-digital converter (ADC), timers, capture-compare PWM (CCP) and the universal synchronous asynchronous receiver transmitter (USART).

# **ADC Module**

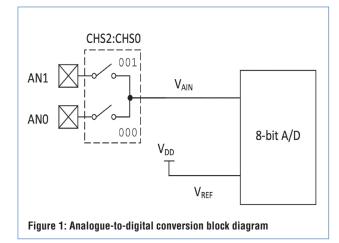

The ADC module converts an analogue input signal into a corresponding 8-bit digital number. The output of the internal sample-and-hold circuit is input to the converter,

which generates the result via successive approximation.

The analogue reference voltage is software-selectable to either the device's positive supply voltage (VDD) or the voltage level on the Vref pin. The ADC has the unique feature of being able to operate while the device is in sleep mode. The block diagram of the circuit is shown in Figure 1.

The module has three registers, the two control registers are ADcono and ADcon1 and the single result register is ADres. ADcono controls the operation of the ADC module.

This register is used to select the conversion clock frequency and the analogue channel. It is where the start and end of conversion are determined. ADcon1 configures the functions of the port pins. The microcontrollers have either five or eight I/O pins that can be configured as analogue inputs.

After ADcono and ADcon1 are configured, the go/done bit in ADcono is set to a one to start the conversion and then monitored to track when the conversion is complete. At that stage the result is loaded into the ADres register, the go/done bit is cleared and the A-D interrupt flag bit (ADif) is set.

To get the most out of modern microcontrollers, it is often necessary to ensure that its peripherals are properly configured

Simple code is available that reads the ADres register and passes it to the USART and CCP modules. Switching between the two analogue input channels is done by changing the value of the CHS2:CHS0 bits of the ADcono register. Figure 1 only shows AN1 and AN0, but any of the analogue input channels can be selected via CHS2:CHS0.

# Timers

The microcontrollers have three timer modules – timero, timer1 and timer2 – each can generate an interrupt to indicate that an event, such as a timer overflow, has occurred. Timero is a simple 8-bit timer-counter. Timer1 is a 16-bit timer-counter consisting of two readable and writable 8-bit registers.

Timer2 is an 8-bit timer with a pre-scaler, post-scaler and period register. Using the pre-scaler and post-scaler at their maximum settings, the overflow time is the same as that of a 16-bit timer. Timer2 is the PWM time-base when the CCP module is used in the PWM mode.

For PWM mode, the registers to be configured are the timer2 period register (PR2), timer2 control register (T2con) and PIR1 register. The PWM output has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is inverse of the period, specified by writing to the PR2 register.

In addition, there are two capture-compare PWM (CCP) modules, each containing a 16-bit register that can operate as a 16-bit capture register, a 16-bit compare register or a 10-bit PWM master-slave duty cycle register. The CCP modules are identical in operation except for the special event trigger.

# **USART**

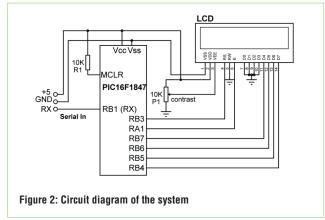

The USART module is one of the two serial I/O modules, the other being the SSP. The USART is also known as a serial communications interface, or SCI. It can be configured as a full-duplex asynchronous system that can communicate with peripheral devices such as personal computers, or as a half-duplex synchronous system that communicates with peripheral devices such as A/D or D/A integrated circuits and serial EEPROMS.