July 2016 Volume 122 Issue 1963 £5.60

# Electronics WORLD

## Powering Noise-Sensitive Analog/RF Applications by Linear Technology

120 100 Vour Down to DV @ 200mA (dB) PSRR ( 13042 1.8V to 20V NIN 40 Ultralow Noise ILIM PGFB 100 <sup>10k</sup> 100k FREQUENCY (Hz) 1M 10M 2 AVIANS Output Noise 2 AVIA HZ Spot Noise 2 AVIA HZ Spot Noise SPECIAL REPORT POWER Power management Parasitics Inverters

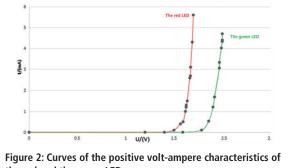

Technology Whiter than white – a new generation of LEDs

NEW Regular column: Embedded design

Products

Latest generation of oscilloscopes and 'scope features

## IMMEDIATE SHIPMENT FROM THE WORLD'S LARGEST SELECTION OF ELECTRONIC COMPONENTS

## 0800 587 0991 • 0800 904 7786 **DIGIKEY CO.UK**

ㅋㅋ

SHIPPING

State.

4.8 MILLION PARTS ONLINE 650+ INDUSTRY-LEADING SUPPLIERS 100% AUTHORIZED DISTRIBUTOR

A shipping charge of £12.00 will be billed on all orders of less than £50.00. All orders are shipped via UPS for delivery within 1-3 days (dependent on final destination). No handling fees. All prices are in British pound sterling and include duties. If excessive weight or unique circumstances require deviation from this charge, customers will be contacted prior to shipping order. Digi-Key is an authorized distributor for all supplier partners. New product added daily. © 2016 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

CTRONICS

Π

Π

00,000+ ODUCTS Stock

#### REGULARS

#### 05 TREND

Disruptive technologies drive automotive lighting industry growth

#### 06 TECHNOLOGY

10 REGULAR COLUMN: MCUS by Lucio di Jacio

14 NEW REGULAR COLUMN: EMBEDDED DESIGN by Dr Dogan Ibrahim

#### 49 **PRODUCTS**

50 **NEW** EVENT LISTINGS

#### Cover supplied by LINEAR TECHNOLOGY More on pages 8-9

#### FEATURES

18

#### THE FUTURE OF ETHERNET

By **Ron Wilson**, Technical Writer, Intel Programmable Solutions Group

### 20 POWER MANAGEMENT FOR FPGA, GPU AND ASIC SYSTEMS

By **Afshin Odabaee**, Business Manager for µModule Power Products at Linear Technology

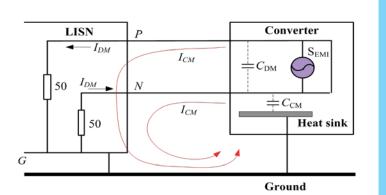

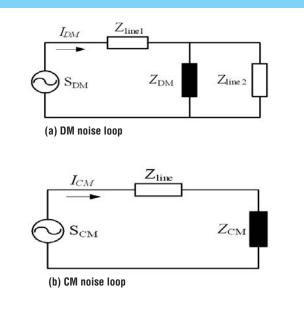

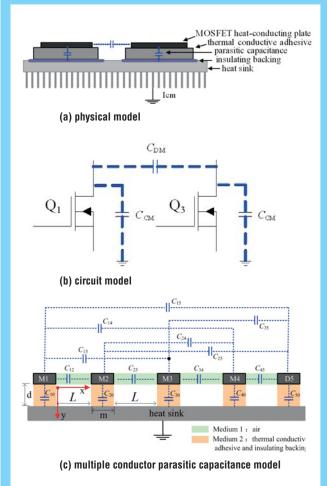

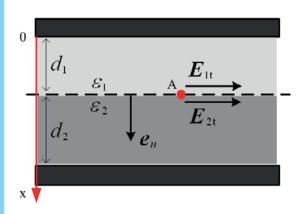

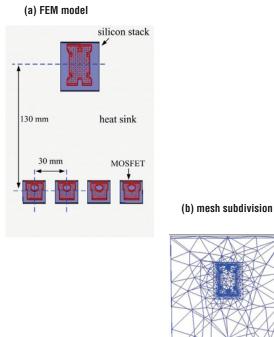

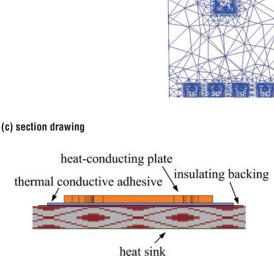

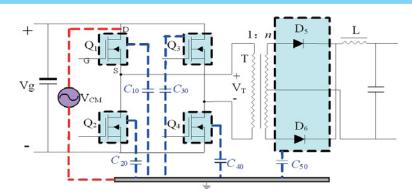

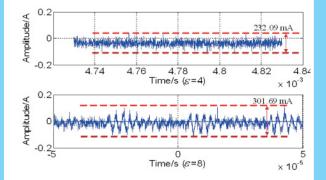

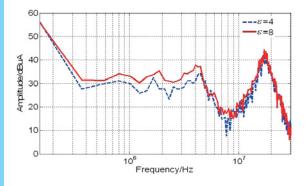

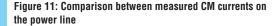

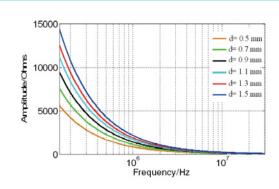

24 ESTIMATION OF PARASITIC PARAMETERS AND EMI IMPROVEMENT OF A FULL-BRIDGE PWM CONVERTER SYSTEM IN THE ELECTRIC VEHICLE

By **Quandi Wang** and **Qingsong Liu** from Chongqing University, China

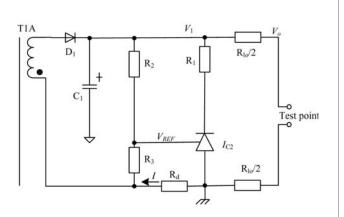

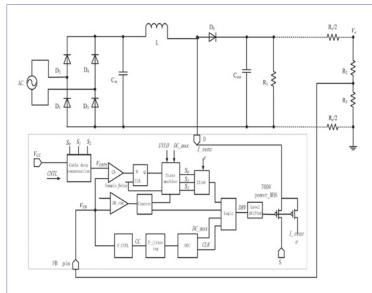

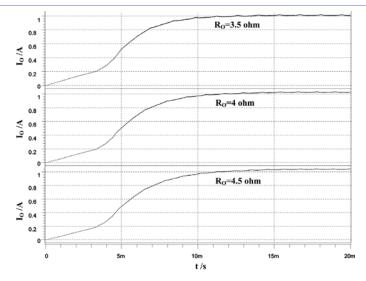

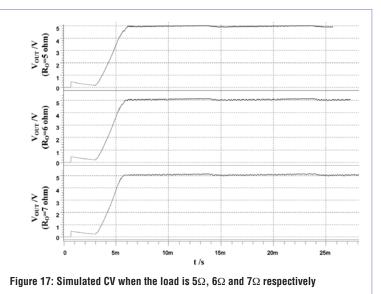

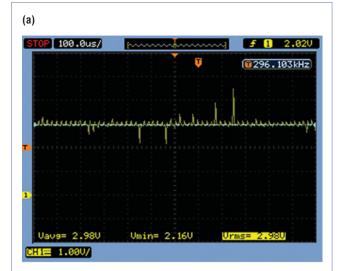

### **30** OUTPUT CABLE VOLTAGE DROP COMPENSATION CIRCUIT WITH STATE MACHINE

**Ling-Feng Shi, Sen Chen** and **Xiu-Jie** Hu of Xidian University, China, present a novel output cable voltage drop compensation circuit

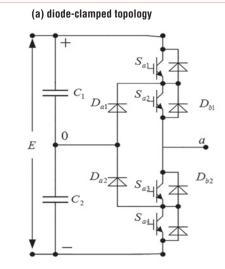

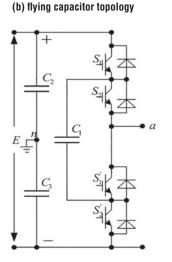

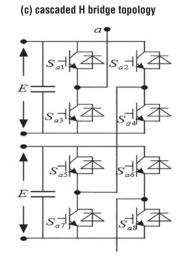

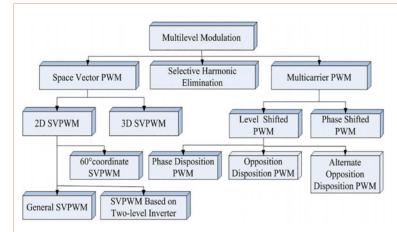

40 REVIEW OF MULTILEVEL INVERTER TOPOLOGIES, CONTROLS AND APPLICATIONS By Lu Zheng, Ouyang Honglin and Xiao Muxuan from Hunan University, China

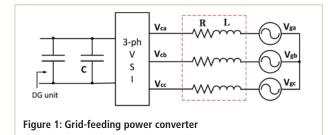

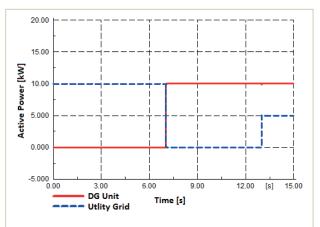

42 IMPROVED POWER FLOW CONTROL SCHEME FOR A GRID-CONNECTED MICROGRID

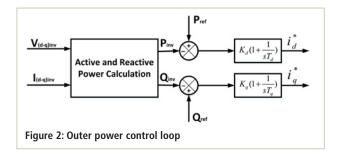

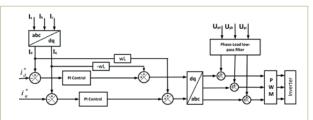

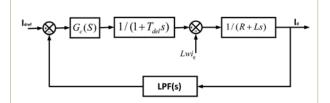

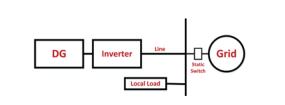

Amirreza Naderipour, Abdullah Asuhaimi Mohd Zin and Mohd Hafiz Bin Habibuddin from Universiti Teknologi Malaysia present a dual-loop power-flow control method for a grid-connected microgrid

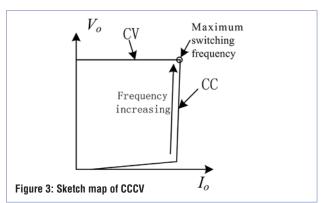

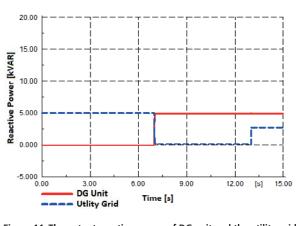

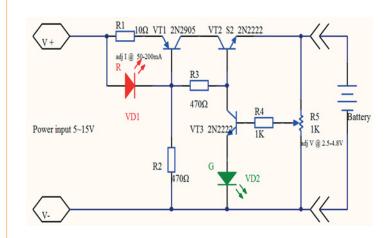

### 46 NOVEL RECHARGEABLE BATTERY CHARGE INDICATION CIRCUIT

By **Lin Zhiqi** and **Zhao Jiangtuo** of Changchun University of Technology in China design a two-stage charging indication circuit based on constant current and constant voltage

Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry – particularly as regards electric shock, fire hazards and explosions.

## **NEW!** IP67 rated 12 to 36 watt encapsulated AC-DC power supplies for harsh environments!

OME

### Features

- 90-264VAC universal AC input

- Compact dimensions PS12MK 56x39x26mm,

PS20MK 64x47x28mm, PS36MK 133x50x34mm

- Single DC outputs of 5, 9, 12, 15 or 24V

- IP67 fully encapsulated and waterproof

- Fixing holes for wall or chassis mounting

- Input and output connectors optional

Comes with 400mm flying leads as standard

- No Load Power Consumption ≤0.3W max

- EN60950 & EN55022 safety & EMC standards (cTUVus approvals pending)

- Ideal for CCTV or LED applications

- Class II safety, no earth connection required

- · CE marked and full safety approvals

| Output Voltage & Current Ratings |            |           |             |           |            |  |  |  |  |  |

|----------------------------------|------------|-----------|-------------|-----------|------------|--|--|--|--|--|

| MODEL                            | OUTPUT     | MODEL     | OUTPUT      | MODEL     | OUTPUT     |  |  |  |  |  |

| PS12MK-05                        | 5VDC 2A    | PS20MK-05 | 5VDC 3A     | PS36MK-05 | 5VDC 5A    |  |  |  |  |  |

| PS12MK-09                        | 9VDC 1.2A  | PS20MK-09 | 9VDC 2A     | PS36MK-09 | 9VDC 4A    |  |  |  |  |  |

| PS12MK-12                        | 12VDC 1.0A | PS20MK-12 | 12VDC 1.5A  | PS36MK-12 | 12VDC 3A   |  |  |  |  |  |

| PS12MK-15                        | 15VDC 0.8A | PS20MK-15 | 15VDC 1.2A  | PS36MK-15 | 15VDC 2.4A |  |  |  |  |  |

| PS12MK-24                        | 24VDC 0.5A | PS20MK-24 | 24VDC 0.83A | PS36MK-24 | 24VDC 1.5A |  |  |  |  |  |

www.powersolve.co.uk Email: sales@powersolve.co.uk Tel: 44-1635-521858

TREND **05**

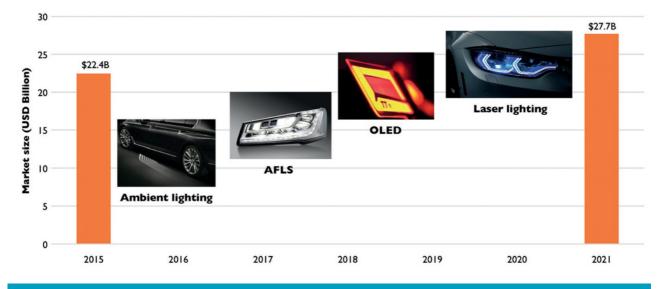

### DISRUPTIVE TECHNOLOGIES DRIVE AUTOMOTIVE LIGHTING INDUSTRY GROWTH

The car is not just a simple mode of transport any more. In addition to security and autonomous driving features, car manufacturers are considering more and more functionalities to promote vehicles as custom and fashion items.

During the last few years, the progress of electronic, optoelectronic, software and various digital technologies, along with social changes, have added additional pressure on car manufacturers to transform their offerings and business models faster than ever before. In this context, automotive OEMs not only have to remain focused on their core competencies, but also develop new ones to remain competitive. One field where they might be requiring specific expertise is automotive lighting.

The lighting market for automotive applications will reach a compound annual growth rate (CAGR) of 23.7% by 2021, becoming nearly a \$28bn market, according to French analysis house Yole Développement, that Automotive OEMs not only have to remain focused on their core competencies but they also have to develop new ones to remain competitive

prepared a report on this subject, called *"Automotive Lighting: Technology, Industry and Market trends".*

The growing role of design in automotive lighting and the introduction of new functionalities such as ambient, rear, fog, turn signal, parking, low/high beam and day-running lights are seen as the main reasons for their success.

In its report, Yole discusses the companies behind this growth, type of lighting technologies available – LEDs, OLEDs, halogen lighting, etc., and their impact on the supply chain, but also which one of these are likely to address market needs the most.

#### Automotive lighting market size 2015-2021

Yole Développement is an industry analysis house based in Lyon, France (www.yole.fr)

#### EDITOR:

Svetlana Josifovska Tel: +44 (0)1732 883392 Email: svetlanaj@sjpbusinessmedia.com

#### SALES:

James Corner Tel: +44 (0)20 7933 8985 Email: jamesc@electronicsworld.co.uk

Philip Woolley Tel: +44 (0)20 7933 8989 Email: philipw@sjpbusinessmedia.com

**DESIGN:** Tania King

PUBLISHER: Wayne Darroch

ISSN: 1365-4675

#### PRINTER: Buxton Press Ltd

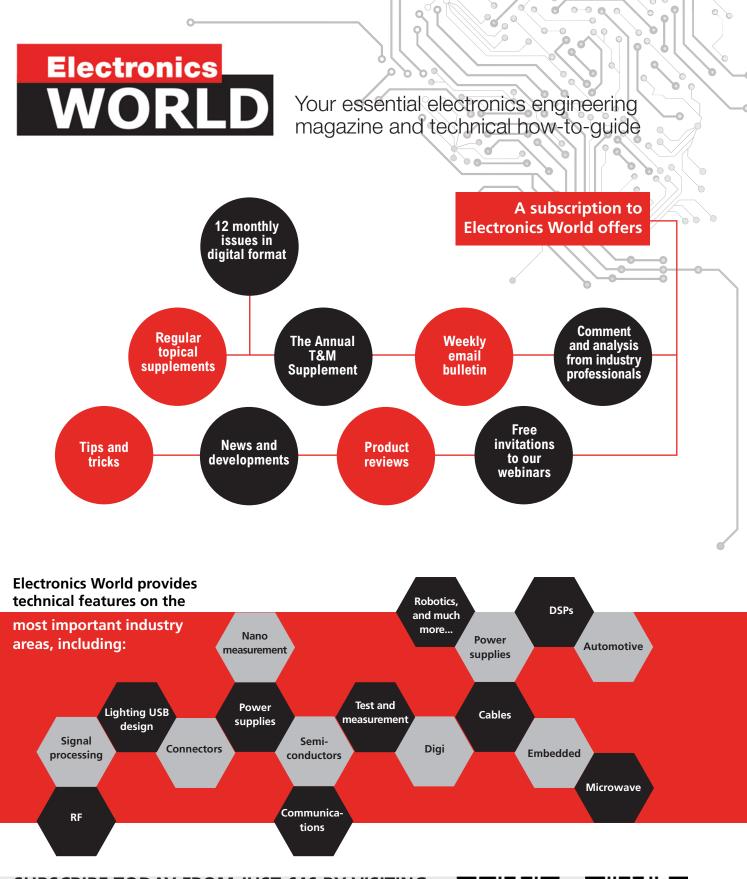

#### SUBSCRIPTIONS: Subscription rates:

1 year: £65 (UK); £94 (worldwide) Tel/Fax +44 (0)1635 879361/868594 Email: electronicsworld@circdata.com www.electronicsworld.co.uk/subscribe

2nd Floor, 52-54 Gracechurch Street, London, EC3V 0EH

www.electronicsworld.co.uk

### DECADES-OLD LED COLOUR CONSISTENCY PROBLEM SOLVED BY EYE 'CONES' RESEARCH

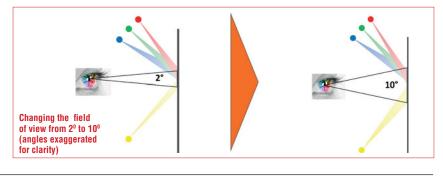

Osram Opto Semiconductors has applied the latest findings of physiological research into how the human eyes perceive colour to solve an 85-year-old challenge of why the same light from two different LED light sources measured to be exactly the same can still appear different.

The phenomenon of colour perception versus reality colour measurement of different light sources has been well-known to scientists for decades. In general lighting, this occurs when there are several LED white light sources in the same space, such as spotlights, wallwashers and downlights.

In 2015 the International Commission of Illumination (CIE 170-2:2015) published a new colour space based on extensive research. Beside the physiological meaningful axis of the colour space, the most important improvement is the definition for a 10° observer view. Osram has applied these findings to the general lighting market with significant success.

"Colour coordinates in general lighting are typically measured with the CIE 1931 2° colour space. It is assumed that the blue, green and red cones that are responsible for colour perception in our eyes are evenly distributed and that the colour perception over viewing angle is constant. In reality this is not the case, and pigment density varies significantly over the field of view's size," said Alexander Wilm, Applications Manager at Osram Opto Semiconductors. "Most people have had this peculiar experience without realising, and it has a big impact on many markets. In retail and museum applications, for example, colour inconsistency is not an option and is often unpleasant, as it doesn't show an object in the best possible and consistent illumination. The world's greatest modern artists also want their work to be viewed as they had originally intended." Osram solved the problem by complementing the CIE 1931 2° xy colour space with the CIE 2015 10° u'v'. By assessing the colour consistency not only at 2° field of view but also at a significantly larger 10° field of view, the measurement and binning – when LEDs' variety of factors are measured for each individual component under the exact same conditions regarding temperature voltage, etc – provides a more accurate assessment of colour discrepancies under realistic observation conditions.

The resulting TEN° binning feature has already been implemented in Osram's new Soleriq S 13 LED type, achieving unprecedented colour consistency under LED lighting.

m m m

### Rittal – The System.

Faster – better – everywhere.

# Power distribution from the smallest to the largest.

POWER DISTRIBUTION

FRIEDHELM LOH GROUP

**ENCLOSURES**

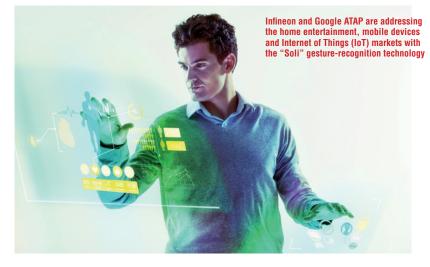

### GOOGLE ATAP AND INFINEON ADVANCE THEIR PARTNERSHIP IN "SOLI" RADAR TECHNOLOGY

Gesture-controlled smartwatch and wireless speaker were demonstrated at "Google I/O" for the first time in May in Mountain View, California. Both devices use technologies from Infineon Technologies and Google ATAP to recognize gestures that completely replace switches and buttons.

"Gesture sensing offers a new opportunity to revolutionize the human-machine interface by enabling mobile and fixed devices with a third dimension of interaction," said Ivan Poupyrev, Technical Project Lead at Google ATAP. "This will fill the existing gap with a convenient alternative to touch- and voice-controlled interaction."

Infineon and Google ATAP believe gesturecontrolled devices are a perfect fit for home entertainment, mobile devices and the Internet of Things (IoT). The jointly developed 'Soli' technology uses radar chips from Infineon and Google ATAP's software and interaction protocols.

"Sophisticated haptic algorithms combined with highly integrated and miniaturized radar chips can foster a huge variety of applications," said Andreas Urschitz, President of the Power Management and Multimarket division at Infineon. "Our goal is to

create a new market standard with compelling performance and new user experience, developing a core technology to enable augmented reality and IoT."

Whilst virtual reality technologies could already visualize new realities, users could not interact with these realities. The 60GHz radar application

developed by Google and Infineon bridges that gap, acting as the technology at the heart of the new-generation augmented reality.

"Since mankind started using tools over two million years ago, this is the first time in history that tools adapt to their users, rather than the other way round," added Urschitz.

### POWERING NOISE-SENSITIVE ANALOG/RF APPLICATIONS

#### By Amit Patel, Senior Design Engineer, Power Products, Linear Technology Corporation

W

hen it comes to powering noise-sensitive analog/RF applications, low dropout (LDO) linear regulators are generally preferred over their switching counterparts. Low-noise LDOs power a wide range of analog/RF designs, including frequency synthesizers (PLLs/VCOs),

RF mixers and modulators, high-speed and high-resolution data converters (ADCs and DACs) and precision sensors. Nevertheless, these applications have reached capabilities and sensitivities that are testing the limits of conventional low-noise LDOs.

For instance, in many high-end VCOs, power supply noise directly affects the VCO output phase noise (jitter). Moreover, to meet overall system efficiency requirements, the LDO usually post-regulates the output of a relatively noisy switching converter, so the high-frequency power supply rejection ratio (PSRR) performance of the LDO becomes paramount.

With its ultralow output noise and ultrahigh PSRR performance, the LT3042 can directly power some of most noise-sensitive applications while post-regulating the output of a switching converter, without requiring bulky filtering.

#### Performance, Robustness & Simplicity

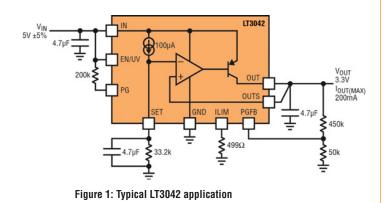

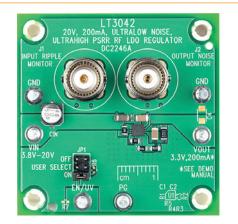

The LT3042 is a high-performance low-dropout linear regulator featuring Linear Technology's ultralow noise and ultrahigh PSRR architecture for powering noise-sensitive applications. Even with its high performance, the LT3042 maintains simplicity and robustness. Figure 1 is a typical application and Figure 2 shows a complete demonstration circuit. The LT3042's tiny 3mm × 3mm DFN package and minimal component requirements keep overall solution size small.

Designed as a precision current reference followed by a high performance voltage buffer, the LT3042 is easily paralleled to increase output current, spread heat on the PCB and further reduce noise – output noise decreases by the square-root of the number of devices in parallel. Its current-reference-based architecture offers wide output voltage range (oV to 15V) while maintaining unity-gain operation, thereby providing virtually constant output noise, PSRR, bandwidth and load regulation, independent of the programmed output voltage.

In addition to offering ultralow noise and ultrahigh PSRR performance, the LT3042 includes features desired in modern systems, such as programmable current limit, programmable power good threshold and fast start-up capability. Furthermore, the LT3042 incorporates protection features for batterypowered systems. Its reverse input protection circuitry tolerates negative voltages at the input without damaging the IC or developing negative voltages at the output – essentially acting as if an ideal diode is connected in series with the input. In battery backup systems where the output can be held higher than the input, the LT3042's reverse output-to-input protection circuitry prevents reverse current flow to the input supply. The LT3042 includes internal foldback current limit, as well as thermal limit with hysteresis for safe-operating-area protection.

#### **Ultralow Output Noise**

With its 0.8 $\mu$ VRMS output noise in 10Hz-100kHz bandwidth, the LT3042 is the industry's first sub-1 $\mu$ VRMS noise regulator. This opens up applications previously not possible, or otherwise required expensive and bulky filtering components.

The SET pin capacitor (CSET) bypasses the reference current noise, the base current noise (of the error amplifier's input stage) and the SET pin resistor's (RSET) inherent thermal noise. With a  $22\mu$ F CSET, the output noise is under  $20nV/\sqrt{Hz}$  at 10Hz. But, capacitors can also produce 1/f noise, particularly electrolytic capacitors. To minimize that, use ceramic, tantalum or film capacitors on the SET pin.

Actively driving the SET pin with either a battery or a lower noise voltage reference reduces noise below 10Hz. Doing so essentially eliminates the reference current noise at lower frequencies, leaving only the extremely low error amplifier noise. This ability to drive the SET pin is another advantage of the current-reference architecture. The integrated RMS noise also improves as the SET pin capacitance increases, dropping below 1 $\mu$ VRMS with just 2.2 $\mu$ F CSET.

Increasing SET pin bypass capacitance for lower output noise generally leads to increased start-up time, which is alleviated by the LT3042's fast start-up circuitry, easily configured using two resistors.

#### Ultrahigh PSRR Performance

LT3042's high PSRR is important when powering noisesensitive applications. Unlike conventional LDOs, whose PSRR performance deteriorates into the 10s of dB as you approach dropout, the LT3042 maintains high PSRR at even low inputto-output differentials. LT3042 maintains 70dB PSRR up to 2MHz with only 1V input-to-output differential and almost 60dB PSRR up to 2MHz at a mere 600mV input-to-output differential. This capability allows the LT3042 to post-regulate switching converters at low input-to-output differentials – for high efficiency – while its PSRR performance satisfies the requirements of noise-sensitive applications.

#### **Post-Regulating a Switcher**

In applications where the LT3042 is post-regulating the output of a switching converter to achieve ultrahigh PSRR at high frequencies, care must be taken with the electromagnetic coupling from the switching converter to the output of the LT3042. In particular, while the "hot-loop" of the switching converter should be as small as possible, the "warm-loop" (with AC currents flowing at the switching frequency) formed by the switcher IC, output inductor and output capacitor (for a buck converter) should also be minimized, and it should either be shielded or placed a couple of inches away from ultralow noise devices like the LT3042 and its load. While the LT3042's orientation with respect to the warm-loop can be optimized for minimum magnetic coupling, in practice, it can be challenging to achieve 80dB of rejection simply with optimized orientation multiple iterations of the PC board may be required.

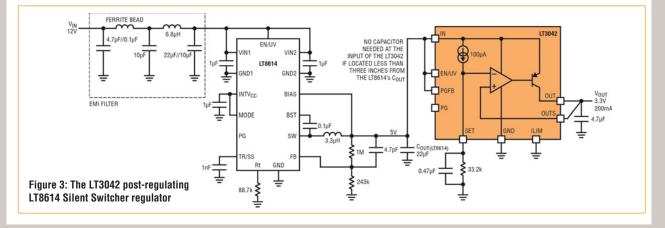

Consider Figure 3, where the LT3042 is post-regulating the LT8614 Silent Switcher regulator running at 500kHz with an EMI LT3042 input significantly attenuates the very high frequency power filter at switching regulator input. With the LT3042 located just one to two inches from the switching converter and its external components, almost 80dB rejection at 500kHz is achieved without any shielding.

To achieve this performance, no additional capacitor - other than the 22µF at switcher's output - is placed at the input of the LT3042. However, even placing a small 4.7µF capacitor directly at the input of the LT3042 results in over 10× degradation in PSRR.

This is peculiarly counter-intuitive - adding input capacitance generally reduces output ripple - but at 80dB rejection, the magnetic coupling, which is usually insignificant, resulting from moderately high frequency (500kHz) switching currents flowing though this 4.7µF capacitor, significantly degrades output ripple. While changing the orientation of the 4.7µF input capacitor and the traces connecting the switcher's output to this capacitor help minimize magnetic coupling, it remains rather difficult to achieve nearly 80dB of rejection at these frequencies, not to mention the multiple PC board iterations it may require.

The relatively high input impedance of the LT3042 prevents highfrequency AC currents from flowing into its input terminal. Given that the LT3042 is stable without an input capacitor if located within three inches of the pre-regulating switching power supply's output capacitor, to achieve best PSRR performance, we recommend not placing a capacitor at the LT3042's input, or minimizing it.

Figure 2: LT3042 demonstration circuit

A couple of inches of trace inductance connecting the LT8614 to the switch transition spikes. Some spikes still propagate to the output due to magnetic coupling from the LT8614's hot-loop. Optimizing the LT3042 board orientation reduces the remaining spikes.

For perspective, trying to achieve 80dB rejection at 500kHz without using the ultrahigh PSRR LT3042 LDO is a tall order. Alternatives don't measure up. For instance, an LC filter would require nearly 40µH of inductance and 40µF of capacitance to achieve 80dB rejection at 500kHz, adding large, expensive components. Costs and board real estate aside, the LC can resonate if not properly damped, adding complexity. Using an RC filter is untenable, requiring impractical resistance to achieve 80dB rejection. Similarly, using conventional LDOs require cascading at least two of them to achieve 80dB rejection at 500kHz, which requires additional components and cost, and degrades the dropout voltage. Additionally, these alternatives also require attention to magnetic field couplings; in particular, high-frequency AC currents must be minimized.

Owing to its ultrahigh PSRR over a wide frequency range, the LT3042 allows lower frequency operation of the upstream switching converter - for improved efficiency and EMI - without requiring any increase in filter component size for powering noisesensitive applications.

#### Linear Technology (UK) Ltd • Tel: 01628 477066 Email: uksales@linear.com • www.linear.com

## Simplifying Capacitive Touch Sensing

BY **LUCIO DI JASIO**, MCU8 BUSINESS DEVELOPMENT MANAGER AT MICROCHIP TECHNOLOGY

ver the past ten years the progress in capacitive touch technology has been nothing short of spectacular. The technology is now a common requirement for many consumer, home appliances and automotive applications.

Whilst projective capacitive sensing is used in small and large (2D input) surfaces, and advanced DSP techniques are used to provide

gesture recognition (3D input), the vast majority of capacitive sensing applications still revolve around much simpler solutions to replace a few buttons in a user interface, possibly with a slider (1D)

or two. Here, despite the apparent simplicity, there seems to be an infinite appetite for customization defying any attempt by silicon manufacturers to standardize solutions around a few fixed-function devices.

Microcontrollers are used extensively to provide the required flexibility but the technology, whilst widely understood in its basic physics principles, is far from trivial in practice. Further, the precise nature of measurements and timings

Figure 1: MPLAB Xpress Evaluation Board

make capacitive sensing a rather core-/performance-intensive task.

This article will explore a novel approach to the problem using the Core Independent peripherals of modern microcontrollers to reduce the core workload and make the application not only simpler but also more accurate and responsive. We will use the MPLAB Xpress cloud toolchain (to avoid lengthy installations), the MPLAB Xpress evaluation board for rapid prototyping and the MPLAB Code Configurator (MCC) for a quick configuration of all required microcontroller peripherals.

#### **Capacitive Sensing**

When it comes to measuring accurately a (very small) capacitive value with a low-cost microcontroller, there are a number of techniques possible but, whilst most have been explored over the past decade, only a few have survived. The Capacitive Voltage Divider (or CVD) is the most prominent, used extensively and with excellent results by developers worldwide.

The physical principle at the root is the "conservation of charge". A reference capacitor of known value ( $C_o$ ) is charged by applying a given voltage ( $V_o$ ) to its plates. Laws of physics state that the charge Q present on its plates is now proportional to the product of the capacity  $C_o$  and applied voltage  $V_o$ .

#### $\mathbf{Q} = \mathbf{C}_{o} * \mathbf{V}_{o}$

A capacitor of unknown value  $(C_x)$  can first be discharged completely and later connected in parallel to the reference capacitor. Since charge is not destroyed or created in the process, the resulting parallel circuit will settle to a voltage proportional to the sum of the two capacitors  $C_0 + C_x$ .

#### $\mathbf{Q} = (\mathbf{C}_{o} + \mathbf{C}_{x}) * \mathbf{V}_{x}$

By measuring  $\mathbf{V}_{\mathbf{x}}$  we can deduce the value of the capacitor under measure:

#### $C_x = C_o * (V_o/V_x - 1)$

In touch-sensing applications we are actually interested in the relative value of the capacitance measured rather than its absolute value, so the exact value of  $C_o$  is not critical as long as it is reasonably constant over time and temperature. If the charging voltage is simply  $V_{dd}$  (3V or 5V) then the voltage measurements can be performed using an analogue-to-digital converter (ADC) peripheral commonly found on any microcontroller.

#### **Capacitive Sensing With A Microcontroller**

In practical implementations, the sensing capacitor ( $C_x$ ) is realized with a small pad (the approximate size of a fingertip) on the printed circuit board, and its value depends both on the area and the material (air) dielectric characteristic as it couples with a reference ground plate. When a finger is pressed against the surface (or in its proximity), the dielectric characteristic is changed (our body is 90% water), resulting in a more or less pronounced change in capacitance.

This would seem trivial to measure if it wasn't for the fact that

the capacitance values involved are minuscule. A typical sensor capacitance is in the order of ten picoFarads (10pF) or less, the same order of magnitude of most parasitic effects (couplings) between traces on a PCB. The capacitiance changes in the vicinity of a finger are only a fraction of that value. It follows that there is a seemingly infinite number of ways noise can get injected into such measurements and wreak havoc.

Many embedded developers who tried to hack together a capacitive sensor found a quick and exhilarating success when testing it on their bench for the first time, only to spend months – if not years – to turn that prototype into a repeatable (manufacturable) and robust embedded application.

Expert touch-sensing developers have distilled a set of rules over the years for optimal PCB layout design (a fundamental step in every touch design) and filtering techniques that enhance the noise immunity of the system. These techniques are all based on the need for a large number of measurements in the shortest possible time.

Since each measurement is composed of a complete sequence (charge, discharge, connect in parallel, convert), even when a fast ADC is used there is still a considerable amount of work that needs to be coordinated and precisely timed by the microcontroller. It is here that smart Core Independent peripherals can make a considerable difference.

#### **ADC With Computation**

In the latest PIC16F18855 family (featured on the MPLAB Xpress Evaluation board) we find a new type of ADC module enhanced specifically to relieve the core from some trivial but otherwise time-consuming tasks that are commonly found in most embedded applications.

The new module adds two post-processing stages to the conversion front-end. First, each conversion result can be accumulated (signed 16-bit math) for a given number of times; the result can then be compared against a pair of threshold values so that an event (or an interrupt) is generated only when a specific condition is identified – a value inside/outside the given window.

Further, conversions can be triggered automatically (based on a number of internal or external events), and a "pre-charging" mechanism has been specifically designed to support the CVD technique so the ADC module sample-and-hold capacitor can be used as reference capacitor ( $C_0$ ) for a completely automatic and fully-integrated sequence.

The use of the new ADCC module results in a massive reduction in the core workload during capacitive-sensing acquisition. Once the input channel is selected, by connecting the ADCC input multiplexer to the desired pin/pad, the module will operate independently for milliseconds before returning an averaged output value ready to be used by the detection algorithms to implement the button or slider functionality desired. This can result in the ability to support a larger number of buttons/inputs, an increase in resolution for proximity detection applications or, even more importantly, a considerable reduction in power-consumption.

| 🕃 Easy Setup 📃 Regist                  | ters 🧘 N    | otifications : 1 |         |             |                 |               |              |

|----------------------------------------|-------------|------------------|---------|-------------|-----------------|---------------|--------------|

| Enable ADC                             | mode        | -                |         |             |                 |               |              |

| ▼ ADC                                  |             |                  |         |             |                 |               |              |

| ADC Clock                              |             |                  | _       | Result Alic | anment          | right         | ·            |

| Clock Source                           | FOSC/AD     | сік і            | -       | Positive R  | eference        | VDD           | -            |

| Clock                                  | FOSC/2      |                  | -       | Negative r  | eference        | nce VSS       |              |

|                                        | 500.0 ns    |                  |         | Auto-conv   | version Trigger | disabled      | -            |

| Sampling Frequency<br>Conversion Time  |             | z<br>D = 5.75 us |         | Finable     | le Continous Op | peration      |              |

| Acquisition Time 0 ≤                   | 8           |                  | ≤ 255   | V Enab      | le Double Samp  | le            |              |

| Computation Feature  Error Calculation | First deriv | ative of Single  | measure | ment -      | •               |               |              |

| Setpoint 0 ≤                           | 0           |                  | ≤ 655   | 35          |                 |               |              |

| Threshold Interrupt                    | enabled     |                  |         | -           |                 |               |              |

| Lower Threshold 0 ≤                    | 0           |                  | ≤ 655   | 35          |                 |               |              |

| Upper Threshold 0 ≤                    | 0           |                  | ≤ 655   | 35          |                 |               |              |

| Repeat 0 ≤                             | 8           |                  | ≤ 255   |             |                 |               |              |

| Acc Right Shift 0 ≤                    | 0           |                  | ≤ 5     |             |                 |               |              |

| ▼ CVD Features                         |             |                  |         |             |                 |               |              |

| Precharge                              |             |                  |         |             | Guard Ring      | polarity      | digital_high |

| Precharge Time                         | 0 ≤         | 4                |         | ≤ 255       | Hold Previou    | us Sample of  | ADFLTR       |

|                                        |             | VDD              |         | -           | Enable          | Intial Accumu | lator clear  |

| Precharge Polarity                     |             | 100              |         |             |                 |               |              |

| Precharge Polarity                     | echarge     | 100              |         |             |                 |               |              |

| 🔅 Easy Setup 📄 Registers              | A Notifications :  | 2              |   |                |

|---------------------------------------|--------------------|----------------|---|----------------|

| Hardware Settings                     |                    |                |   |                |

| Mode asynchronous 💌                   |                    |                |   |                |

| Enable EUSART                         | Baud Rate:         | 9600           | * | Error: 0.160 9 |

| Enable Transmit                       | Transmission Bits: | 8-bit<br>8-bit | * |                |

| Enable Wake-up                        | Reception Bits:    |                | * | ]              |

| Auto-Baud Detection                   | Clock Polarity:    | Non-Inverted   | * | ]              |

| Enable Address Detect                 | Enable Continu     | ous Receive    |   | -              |

| Enable EUSART Interrupts              |                    |                |   |                |

| <ul> <li>Software Settings</li> </ul> |                    |                |   |                |

| Redirect STDIO to USART               | r                  |                |   |                |

| Software Transmit Buffer Size         | 8 💌                |                |   |                |

| Software Receive Buffer Size          | 8 -                |                |   |                |

Figure 3: USART configuration

Figure 4: mTouch evaluation kit – 8 pads board

| Package:     | SOIC28 | *     | Pin No:   | -  | 18 | 19 | 20 | 21  | 22    | 23 | 24 | 25 | 8  | 9  | 10   | 11  | 12   | 13 | 14 | 15 | 2  |

|--------------|--------|-------|-----------|----|----|----|----|-----|-------|----|----|----|----|----|------|-----|------|----|----|----|----|

|              |        |       |           | A. |    |    |    | Por | t B 🔹 |    |    |    |    |    |      | Por | tC . |    |    |    | E  |

| Module       | Fun    | ction | Direction | -  | 0  | 1  | 2  | 3   | 4     | 5  | 6  | 7  | 0  | 1  | 2    | 3   | 4    | 5  | 6  | 7  | 3  |

|              | ADCA   | СТ    | input     |    | î. | î  | ì  | ì   | â     | ъ  | î. | î. | î. | 2  | î.   | î.  | ì    | î. | ì  | ì  | Г  |

|              | ADGR   | DA    | output    |    |    |    |    |     |       |    |    |    | ì  | ì  | ô    | ъ   | 6    | ъ  | î. | ì  |    |

| ADCC .       | ADGR   | DB    | output    |    |    |    |    |     |       |    |    |    | ì  | ì  | b în | î.  | î.   | î. | ì  | ì  |    |

| ADCC *       | ANx    |       | input     |    | ъ  | ъ  | î. | 'n  | Ъ     | ъ  | ъ  | 6  | î. | î. | 6    | ъ   | 2    | ъ  | 6  | ì  |    |

|              | VREF+  | •     | input     |    |    |    |    |     |       |    |    |    |    |    |      |     |      |    |    |    |    |

|              | VREF-  |       | input     |    |    |    |    |     |       |    |    |    |    |    |      |     |      |    |    |    |    |

|              | RX     |       | input     |    | î. | î. | î. | ì   | î.    | 6  | î. | ì  | î. | â  | î.   | î.  | ì    | 3  | ì  | ì  | Г  |

| EUSART *     | ТХ     |       | output    |    | ъ  | ъ  | î. | ъ   | ъ     | ъ  | ъ  | î. | â  | ì  | î.   | ъ   | 6    | ъ  | î. | ì  |    |

| OSC .        |        |       |           |    |    |    |    |     |       |    |    |    |    |    |      |     |      |    |    |    |    |

| D- 14- 4-1   | GPIO   |       | input     |    | ъ  | ъ  | ъ  | ъ   | ъ     | ъ  | ъ  | ъ  | ъ  | ъ  | ъ    | ъ   | 2    | ъ  | 6  | ì. | î. |

| Pin Module * | GPIO   |       | output    |    | 6  | ъ  | 6  | 6   | 3     | ъ  | ъ  | 2  | ъ  | 2  | ъ    | 2   | 3    | 3  | 6  | â  | ì  |

| RESET        | MCLR   |       | input     |    |    |    |    |     |       |    |    |    |    |    |      |     |      |    |    |    | 6  |

#### Figure 5: Pin Manager grid

Figure 6: Terminal screen capture

#### **Touch Express**

Using the MPLAB Xpress cloud tool chain and the MPLAB Xpress little evaluation board we can test the effectiveness of the ADCC module in just minutes to get a feel for the performance achievable.

- After logging into your own myMicrochip account, create a new project for the PIC16F18855 device and launch the MPLAB Code Configurator.

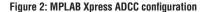

- Select the ADCC module, then select the following options (see Figure 2).

- Choose the Averaging mode.

- Select the internal oscillator (FOSC/2) as the clock source.

- Select the right-hand alignment of the conversion results and

make  $V_{dd}$  and  $V_{ss}$  the positive and negative internal references.

- Enable Continuous operation so the ADCC will perform rapid bursts of conversions as fast as possible.

- Enable the Double Conversion Sample mode, activating a differential CVD sampling technique.

By swapping (alternating) the role of the two capacitors (precharging the external unknown first and discharging it on an empty reference capacitor), it is possible to obtain a *differential* measurement, effectively cancelling out a number of noise sources and increasing measurement resolution substantially.

Expanding the Computation Features section of the configuration window, select the following options:

- Make the error calculation the First Derivative of Single Measurement (also part of the differential technique described above).

- Enable the Interrupt threshold.

- Set the repeat count to 8 (larger values are possible, but won't be needed, as we will soon see).

- Expand the CVD Features section of the configuration window and select the following options:

- Set the precharge time to 4 (clock ticks).

- Set the precharge polarity to VDD (first).

- Enable Inverted precharge.

- Set the guard ring polarity to digital high.

- Set the additional Sample Capacitor to 5(nF); you might try with different values to optimize resolution depending on the size of the sensing pad.

- Add the EUSART module to the project and configure it for the desired baud rate (see Figure 3).

#### Wiring Up The Demo

For demo purposes any size and shape capacitive touchpad will do, but since the little Xpress evaluation board has none of its own, you will need to either clip on a small metal plate to the RC7 pin or recycle one (for example, I had an old mTouch evaluation kit DM183026, so I simply re-cycled the little daughter board with 8 square pads – see Figure 4 – for my own convenience.)

Next, enter the Pin Manager window (grid, see Figure 5) and select the desired I/O pins to connect:

- sensor input to RC7 (a convenient pin positioned at the top right corner of the Xpress evaluation board).

- ADGRDA output to pin RC2 (this will be connected to the terminals marked GND or similar layer on the sensor board PCB, if available).

Note that both the RC7 and RC2 pins must be configured as analogue inputs with digital output functions so the ADCC module can automatically perform the correct CVD pre-charge sequence.

Finally let's configure the UART (TX) output to  $RC_0$ , conveniently connected internally to the serial to USB bridge on board.

#### In 10 Lines Of Code

With a click of the "Generate" button, the MPLAB Code Configurator

will produce the configuration files and place them in the project sources. We are now ready to start focusing on the core of our demo application.

#define TOUCH 0x17 // pin RC7

void main(void)

```

ł

```

SYSTEM\_Initialize();

ADCON3bits.ADSOI = 1; // stop sampling after interrupt

ADCC\_StartConversion(TOUCH); // select channel \_delay\_ms(500); int base = ADACC; // detect base value

while (1)

{ ADCC\_StartConversion(TOUCH); // select channel \_delay\_ms(100); printf("%d\n", base - ADACC); } }

#### Listing 1: Automatic CVD Conversion

The ADCC configuration we obtained with the MPLAB Code Configurator is already providing all that's required to perform a burst of 8 (pairs of differential) conversions, each composed of the complete CVD precharge, discharge, parallel and A/D conversion steps with the correct timing. So all that's left for our main application (as seen in Listing 1) is to select the desired input channel and invoke repeatedly the ADCC\_StartConversion() function.

Reading the output on your terminal application (see Figure 6) will give you a rough idea of the kind of resolution achievable with the suggested configuration.

The values captured whilst I repeatedly touched the sensor (larger values) clearly show a remarkable dynamic range of more than 10 bits. This gives us the confidence that following filtering and event detection logic we might want to turn this demo into a real touch application, with more than sufficient resolution to operate reliably and with large noise margins.

#### In Closing

The MPLAB Code Configurator and the flexibility of the Core Independent Peripherals (ADCC) make it easy for us to completely automate the most core-intensive part of the capacitive touch sensing technology (CVD). Whilst we still need to use the greatest care in designing a proper board layout and add the desired touch detection logic, we have considerably simplified the task at hand and can now focus all our resources and efforts on the development of the actual end application.

#### RIA12 compliant train-borne dc dc converter

MORNSUN\*

The URB series from Mornsun are a range of rugged ultra-wide input dc dc converters, when used in combination with the specially designed FC series input filters they conform to the challenging requirements of EN50155 and RIA12 for train-borne applications.

Available in 3 input ranges: 24Vdc input (range 9 to 36Vdc) 48Vdc input (range 18 to 75Vdc) 72V, 96V, 110V & 120Vdc input (range 40 to 160Vdc) Output voltages: 3.3V, 5V, 9V, 12V, 15V & 24Vdc Power rating: 6W, 10W, 15W & 20W Mounting: PCB; chassis mount or DIN rail Efficiency: 90% Isolation: 1.5kVdc **Cooling:** convection Protection: reverse polarity; output short circuit; over voltage Lead time: 4 weeks

By virtue of their design for the harsh environment of the railway, they are also suitable for many other applications requiring a compact rugged dc dc solution. Applications include: passenger reading lights; on-board Wi-Fi; passenger USB hubs; sensor control modems.

The URB series and the filters are very competitively priced, for further information or to discuss your application please contact our technical sales team.

#### **POWER DISPLAYS EMC**

### www.relec.co.uk

Tel: 01929 555800 e-mail: sales@relec.co.uk

## **Light sensors**

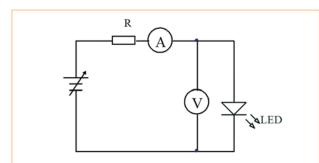

#### BY DR DOGAN IBRAHIM, PROFESSOR AT THE NEAR EAST UNIVERSITY, CYPRUS

t is important to be able to measure and adjust the ambient light for visual comfort in everyday activities, such as whilst using a computer, reading a book, watching television, cooking, eating and so on.

Light has a very wide spectrum, although in this article we are only interested in visible light

in the wavelength range of 390nm (violet) to 700nm (red), all that is necessary in everyday life.

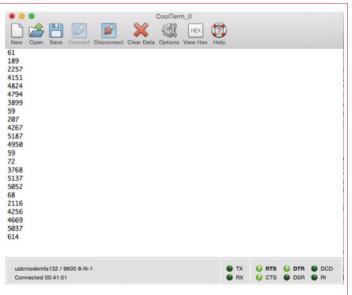

Figure 1 shows the definition of some of the commonly used SI light units. The amount of light being given off in all directions by a light source is known as 'luminous flux', measured in units

Figure 1: Some commonly used light units

of lumens. Table 1 gives the light outputs of some commonly used incandescent light bulbs in lumens. For example, a 60W incandescent light bulb emits about 800 lumens. In 2010, European Union legislation took effect, requiring that all light bulbs must be labelled in terms of their luminous flux outputs (in lumens) instead of electric power (watts).

| Incandescent bulb (watts) | Minimum output (lumens) |

|---------------------------|-------------------------|

| 40                        | 450                     |

| 60                        | 800                     |

| 75                        | 1100                    |

| 100                       | 1600                    |

| 200                       | 3100                    |

| 300                       | 4000                    |

#### Table 1: Light output of incandescent light bulbs

The amount of light incident on a surface is known as 'illuminance' and is measured in units of lux, where lux is the number of lumens falling on a square meter of surface, which in numerical terms is 1 lux = 1 lumen/m<sup>2</sup>. One-candela (1cd) lightsource produces 1 lux of light at one meter distance. Lux is the unit used commonly when measuring and specifying the visual comfort levels in an area.

Luminance is measured in  $cd/m^2$  and indicates how bright a surface appears when looking at it; basically, it is the reflection from a flat diffuse surface. For example, the brightness of a computer display is measured by its luminance.

Illumination from the sky varies at different times of day and at different seasons, as shown in Table 2 in lux.

| Sky condition | Illumination (lux) |  |

|---------------|--------------------|--|

| Full daylight | 10700              |  |

| Overcast      | 1050               |  |

| Dark day      | 105                |  |

| Twilight      | 10                 |  |

| Full moon     | 0.2                |  |

| Quarter moon  | 0.02               |  |

#### Table 2: Illumination from the sky

Although natural illumination from the sky can be bright, it is not usually available inside a building. It is the design engineer's task to make sure that right level of light reaches inside a

building for visual comfort of the occupants. The amount of light required inside a building depends on what tasks are performed there. For example, a watchmaker or a place where electronic components are assembled requires much brighter light than a supermarket. Table 3 gives a list of the recommended illumination levels for different activities. Notice that where possible the actual illumination level is measured on a surface where work is carried out.

| Activity                            | Minimum illuminance (lux) |

|-------------------------------------|---------------------------|

| Watch making and jewellery          | 1500-2000                 |

| Electronics assembly                | 1000                      |

| General computer work, reading/writ | ing 500                   |

| Libraries, lecture theatres         | 300                       |

| Restaurants, warehouses             | 200                       |

| Corridors, changing rooms           | 100-150                   |

| Tunnels, night time parks           | 50                        |

#### Table 3: Recommended illumination levels inside a building

#### **Light Sensors**

A light sensor detects the presence of light (usually visible light) and provides some kind of output of a value proportional to the measured ambient light. Although there are some light sensors with digital outputs, most are simple resistors, also known as a light dependent resistor (LDR), whose resistance changes depending on the light intensity striking the surface of the sensor.

Light sensors are used in embedded applications such as light meters designed to measure light levels inside a building (e.g. an office or a factory), light-sensitive switches and alarms, and so on. In this article we will focus on low-cost analogue light sensors in microcontroller-based embedded applications.

#### **Digital Sensors**

Digital light sensors are accurate devices allowing exact light measurements, usually in the range 0.1-40,000 lux. Most are sensitive to both visible and infrared light sources. Some sensors (e.g. TSL2561) have built-in ADC converters, enabling them to be interfaced with any microcontroller, even if the microcontroller has no ADC converters. Depending on the

type, the operating voltage can be 3.3V or 3-5V, with current consumption of around 0.5mA when active. Some digital light sensors give square-wave outputs where the frequency is proportional to the measured light level. TSL2561 is a 6-pin active device with I2C-type output where the measured light level can be read by addressing the device via the I2C interface.

#### **Analogue Sensors**

An LDR has the property that in the dark its resistance is very high, usually in the range of mega-ohms, but when exposed to light the resistance drops sharply to a few  $k\Omega$ , or even lower, depending on device intensity of the light source and sensitivity.

The main advantages of LDRs are their very low cost and ease of use in embedded applications.

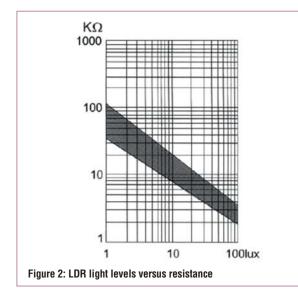

Figure 2 plots the light level against resistance of a typical LDR.

#### **Designing A Simple Light Meter**

Here we present the design of a simple microcontroller-based light meter for measuring ambient light and displaying it on an LCD in lux. The meter has a limited range and gives only approximate results, i.e. it's not meant to be a professional-grade device. For more accurate results, a photodiode or a digital light sensor is recommended.

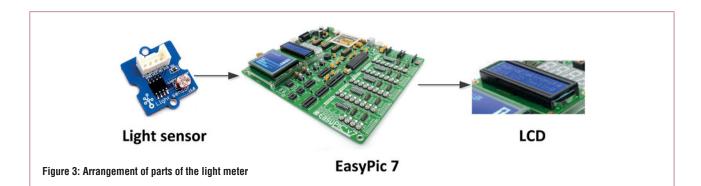

Figure 3 shows the arrangement of the example system. The ambient light level is sensed using a Grove light sensor module (available at www.seeedstudio.com), which provides an analogue output voltage proportional to the measured light level. The ADC channel ANo of a PIC microcontroller receives this voltage and, after some processing, displays the actual light level in lux.

This light meter can also be used in an embedded circuit as a light-dependent switch, to be activated at a predefined level of ambient light.

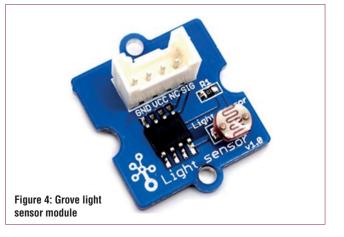

#### The Grove Light Sensor Module

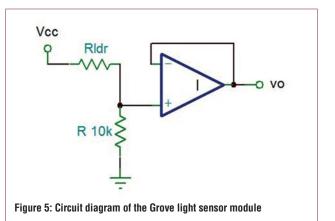

This is a low-cost small module with GL5528 LDR light sensor on board (see Figure 4). As shown in Figure 5, a unity-gain operational amplifier buffer provides the module's output voltage. The relationship between output voltage and measured light level can be derived as follows:

Because of the voltage-divider resistors at the positive input of the op-amp, the op-amp's output voltage is simply given by:

$$V_o = \frac{V_{CC}R}{R + R_{IDR}} \tag{1}$$

or,

$$R_{LDR} = \frac{R(V_{CC} - V_o)}{V_o}$$

(2)

Assuming a 10-bit ADC with 1023 quantization levels and reference voltage  $V_{cc}$ , the relationship between the output voltage  $V_o$  and its digital value *r* read by the microcontroller is given by:

$$V_{o} = \frac{rV_{CC}}{1023}$$

(3)

Substituting in Equation 2 we have,

1

$$R_{LDR} = \frac{R(1023 - r)}{r} \tag{4}$$

But, since R is 10k, the value of the LDR in  $k\Omega$  is found with Equation 5. Notice that the power supply voltage  $V_{cc}$  is eliminated from the equation, whose solution depends only on the digital value read from the ADC and the value of the voltage

divider resistor R used:

$$R_{LDR} = \frac{10 \times (1023 - r)}{r}$$

(5)

After finding the value of the LDR (in  $k\Omega),$  we can calculate the light level:

$$Lux = \frac{120}{R_{LDR}} \tag{6}$$

Thus, we use Equation 5 initially to determine the LDR resistance, and Equation 6 to calculate and display the light level in lux.

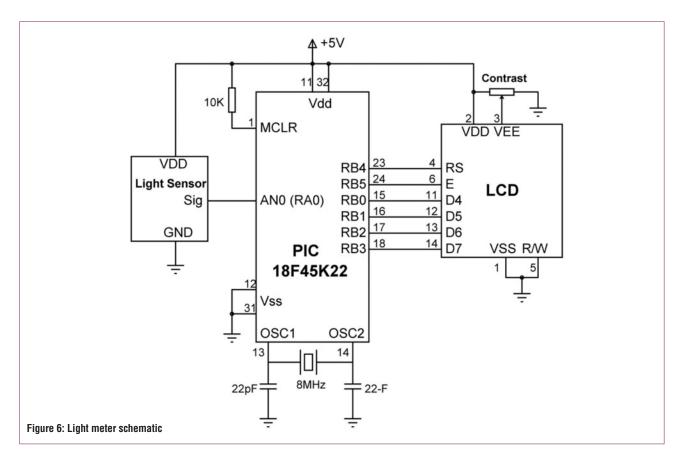

Figure 6 shows the schematic diagram of the light meter. The EasyPIC V7 development board is used in the design (performance is not an important factor in this design, and any other microcontroller can be used as long as there is at least one ADC channel and a digital port with at least 6 pins to connect the LCD). This development board is equipped with a PIC18F45K22 medium-performance PIC microcontroller, with an 8MHz crystal. In addition, the board contains rich features that make it an ideal development board for those wishing to learn and experiment with PIC microcontrollers.

The light-sensor module is connected to analogue input ANO (port RAO) of the PIC18F45K22 and is powered from the +5V supply of the development board. The 2x16 character LCD is connected to the microcontroller's PORTB to display the light level in real time, its contrast being adjusted with a potentiometer. The LCD is operated in 4-bit mode to minimize I/O port pin-count.

#### The Software

Listing 1 shows the software for the light meter. The program was written using the mikroC Pro for PIC language and the integrated development environment (IDE). At the beginning of the program the connections of the LCD to PORTB are defined. The main program starts by configuring PORTB as a digital port (ANSELB = 0) and then initializing the LCD library. The main program is then executed in an endless loop formed using a while statement. Inside this loop the output of the light sensor is read through analogue input channel ANo using statement ADC\_ Read(0) and the digital value read is then converted into physical units of lux using Equations 5 and 6. Notice that for accuracy the calculation is done using floating point arithmetic. The value is then converted into a string variable (Txt) using statement FloatToStr so it can be displayed on an LCD. Any leading spaces are removed from this variable using statement Ltrim, and statement Lcd\_Out is called to display the light level starting from the LCD's first row and first column, followed by text "LUX". This process is repeated endlessly at one-second intervals, and is only terminated if stopped by the user.

// LCD module connections sbit LCD\_RS at RB4\_bit; sbit LCD\_EN at RB5\_bit; sbit LCD\_D4 at RB0\_bit; sbit LCD\_D5 at RB1\_bit; sbit LCD\_D6 at RB2\_bit; sbit LCD\_D7 at RB3\_bit;

sbit LCD\_RS\_Direction at TRISB4\_bit; sbit LCD\_EN\_Direction at TRISB5\_bit; sbit LCD\_D4\_Direction at TRISB0\_bit; sbit LCD\_D5\_Direction at TRISB1\_bit; sbit LCD\_D6\_Direction at TRISB2\_bit; sbit LCD\_D7\_Direction at TRISB3\_bit; // End LCD module connections

#### void main()

<

unsigned int r; float RLDR, LUX; unsigned char Txt[14]; ANSELB = 0;LCD\_Init(); while(1) { r = ADC\_Read(o); // Read from analogue ANo  $\overline{\text{RLDR}} = 10.0^{*}(1023.0 - r) / r;$ // Calculate the LDR resistance LUX = 120.0 / RLDR; // Calculate the LUX value LCD\_Cmd(\_LCD\_CLEAR); // Clear LCD FloatToStr(LUX, Txt); // convert into string LTrim(Txt); // Remove leading spaces Lcd\_Out(1,1,Txt); // Display result Lcd\_Out\_Cp("LUX"); // Display the unit Delay\_Ms(1000); // Wait 1 second }

Listing 1: Program listing of the light meter

## **THE FUTURE OF ETHERNET**

#### BY RON WILSON, TECHNICAL WRITER, INTEL PROGRAMMABLE SOLUTIONS GROUP

Ethernet was developed at Xerox's Palo Alto Research Center (PARC) to replace an earlier network with a shared co-axial cable on which all devices were peers. The key enabler of its wider success was the decision to submit Ethernet to the Institute of Electrical and Electronics Engineers (IEEE) standards process. Each development since has drawn on a methodical process of convening a task group, defining requirements and organizing development, with the outputs being proven in interoperability testing workshops. This gives Ethernet a huge advantage in emerging applications.

IEEE 802.3 Ethernet standards define the bottom two layers of the network protocol stack: layer 2, the media access control (MAC); and layer 1, the sub-layers that are together known as the physical layer (PHY). Other networking layers above Ethernet (IP, TCP, etc) are specified and standardized independently. Once a standards working group defines a new combination of medium and data rate, all the protocol layers implemented above Ethernet become available for use in the new applications area.

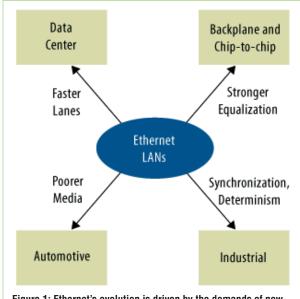

Figure 1: Ethernet's evolution is driven by the demands of new applications [Source: Altera]

#### PHY

New applications tend to demand new approaches to implementing the physical layer. Channel negotiation, signalling methods and transmitter/receiver equalization all need to be updated to squeeze more information per second through current and new communication channels.

One example of this process at work is the development of a standard for 10Gbit/s backplane interconnects, known as 10GBASE-KR. Here the attraction of Ethernet is to reduce the number of signals crossing a backplane, standardize the PHY hardware and use standard protocols to set up channels and move data.

The challenge of implementing 10GBASE-KR is to achieve 10Gbit/s data rates not over a finely-tuned medium such as highquality co-ax, but over a channel composed of a mix of circuit-board traces, vias, connectors and backplane runs of differing lengths and electrical characteristics. In this environment, each transmitter and receiver must adjust its equalization independently, demanding many tap-adaptive receiver equalizers and new channel-training sequences.

The technology behind 10GBASE-KR is also being used for chipto-chip connections on circuit boards, to replace multiple parallel connections with fewer, faster serial links, thus reducing pin count, board congestion and failure rate. In advanced system-on-a-chip (SoCs), the extra die area to support the extra transceivers may be less expensive than implementing the many pins of a parallel connection.

#### **Faster Ethernet**

The use of Ethernet in data centres, which need much greater bandwidths between server racks, is driving the development of faster version of the standard. The idea is to increase the maximum speed of a single Ethernet lane from 10Gbit/s to 25Gbit/s, and then to 50Gbit/s and 100Gbit/s, using binary or multi-level modulation signalling. This will require better transceivers and new generations of test equipment. The 25Gbit/s lanes will enable data centres to upgrade their existing top-of-rack cabling from 10Gbit/s to 25Gbit/s, or from 10/40Gbit/s to 50/100Gbit/s.

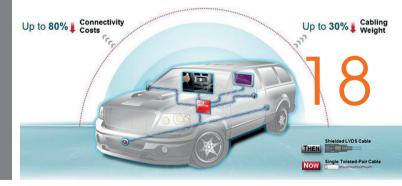

#### **Vehicle Ethernet**

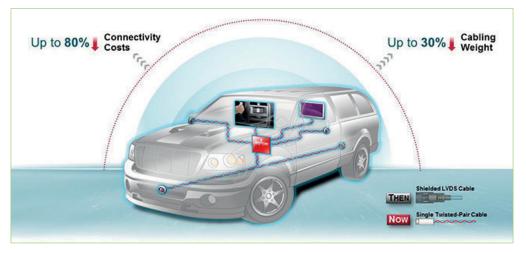

Cars now have so much electronic interconnect that cabling has become an important part of vehicle cost, weight and reliability. This makes the promise of Ethernet – one shared medium and protocol for all data – extremely attractive.

The challenge here is that the best bearer medium in most cars is unshielded twisted pair (UTP), with all its issues of uniformity, impedance and noise-susceptibility. Automotive designers already face these issues in low-speed CAN buses, which is why the Open Figure 2: BroadR-Reach promises a single, lightweight and inexpensive network on which all the disparate systems in a car can converge [Source: Broadcom]

Alliance has launched the BroadR-Reach standard to run 100Mbit/s Ethernet over UTP.

Using BroadR-Reach PHYs and standard 100Mbit/s Ethernet switch chips, automotive designers hope to concentrate all the interconnect for engine, brake, steering, chassis, lighting, safety, convenience, infotainment and driver-assistance electronics in a few networks (Figure 2). They will then move toward a single, partitioned network architecture and, perhaps eventually, to one network per vehicle.

Automotive Ethernet means linking engine, brake and chassis controllers, which introduces three requirements that Ethernet doesn't fully address yet: synchronicity, frame delay determinism and security.

These relatively tightly-coupled systems often need to synchronize everything on the network to one clock, so that, for example, the order in which events were sensed or commands given can be preserved. This has to happen despite the fact that the communications medium is a best-effort frame-transmission network without a shared real-time clock or quality-of-service guarantee.

These issues are, up to a point, solvable in the Ethernet stack, especially in closed, short networks such as those in a car, and standards groups have also added other solutions to the Ethernet protocol stack.

Synchronicity is addressed in the IEEE 1588-v2 (2008) Precision Time Protocol (PTP) standard, which distributes time-synchronization PTP packets across Ethernet, so that every interface on the network agrees on the time, down to millisecond or even tens-of-nanosecond levels of accuracy.

The 1588 protocol requires time stamping of PTP packets sent periodically between a 1588 master clock generator and all the 1588 network nodes at the Ethernet entry and exit ports. It can be implemented in the upper protocol layers, above the Ethernet MAC, with standard Ethernet PHY devices. For applications that need microsecond accuracy, the Ethernet MAC or PHY devices must be altered to improve their time-stamping.

A separate IEEE working group, on Time-Sensitive Networking (TSN), is addressing the frame-deterministic latency issues. TSN will reduce both the latency and uncertainty in the movement of packets over Ethernet by providing 1588-based standards for precise time synchronization at layer 2 (just above the PHY), reserving resources in the network and managing the scheduling and pre-emption of packets.

In some cases, TSN may even make the network provably deterministic. Eventually, measures such as TSN will have to face the stringent functional safety demands of industrial and transportation applications. A formally provable – or at least formally traceable – system may be possible in some cases.

#### Security

Security is another issue Ethernet must face as it evolves, not only in functional-safety situations but in cloud data centres. It will become increasingly important that nodes on the network not be able to monitor the network traffic without permission, and that nodes cannot spoof the identity of another device to send commands.

The privacy issue is partially covered by the fact that Ethernet PHYs scramble data as part of their data-coding algorithms. There are also standards for security in the MAC, IP and application protocol layers, although these are vulnerable to attack. In the long run, Ethernet will need more powerful authentication and encryption.

#### Power

Finally, work is underway to increase Ethernet's ability to deliver power over an active connection and the data rate supported when it is doing so. There are moves to provide up to 100W for industrial applications over a four-pair connection. Speeds will also rise for single-pair, power-over-data-line technology.

These developments reflect the reasons for Ethernet's success to date. Improving signalling, channel modelling and transceiver design enables Ethernet to reach new data rates over a wider range of media. This opens up new applications, whose implementers can build on everything that has gone before and help add new functions to the protocol stack. Some of these increase bandwidth demands even further, while others need new features in the PHY. This virtuous circle, built on an initial decision to open up PARC technology to the wider design community, helps ensure a steadily broadening horizon for Ethernet.

## **POWER MANAGEMENT FOR FPGA, GPU AND ASIC SYSTEMS**

BY **AFSHIN ODABAEE**, BUSINESS MANAGER FOR  $\mu \text{MODULE}$  POWER PRODUCTS AT LINEAR TECHNOLOGY

here are only a few power-management-related design challenges on system boards controlled by FPGAs, GPUs or ASICs, but these challenges can seriously delay release of a system due to repetitive debugging. However, many power and DC/DC regulation issues can be prevented if the same or similar design is

verified by the suppliers of power products and the FPGA, GPU and ASIC manufacturers.

The burden is often on the shoulders of system designers to analyze the problem, then find a solution. These engineers are already immersed in configuring the complex digital portions of the design. Tackling the analogue and power portion becomes a major challenge, since power is not the simple task many designers expect.

#### **A Challenging Task**

Every design task is initially challenging, including power management for a complicated system that may include transceivers, memory modules, sensors, line connectors, a mesh of PCB traces and layers of PCB planes. But haphazardly addressing power management with DC/DC regulators, capacitors, inductors, heat removal and heat sinks, plus component layout, can lead to later design problems. Hasty decisions by the system designer or choosing inferior solutions will at some point inhibit progress, especially at the debugging stage.

The design of any power management circuit can be done with confidence in a systematic and thoughtful way. In other words, it can be simplified if the analysis is accurate and addresses power management related design challenges before PCB assembly. Figure 1: Arria 10 GX FPGA development kit board

Figure 2: Arria 10 SoC development kit board

Moreover, a power management guide is already tested and verified to meet the requirements of the FPGAs, ASICs, GPUs and microprocessors, and the systems that use these and other digital components.

Mapping power management with proven solutions will ensure that the project is initiated with high confidence. Spending less time on debugging power is an important step in quickly turning a design around, from prototype to production.

#### Example: Powering Arria 10 FPGA And SoC

FPGA development kits enable system developers to evaluate the logic without having to design a complete system. Figures 1 and 2 show Altera's new 20nm Arria 10 FPGA and SoC (system-on-chip) development boards, tested and verified by Altera, demonstrating best design practices in layout, signal integrity and power management.

A well-thoughtout power management design can reduce PCB size, weight and complexity, as well as lead to lower power consumption and cooling costs, all essential to achieve optimal system performance. For example, the 0.95V at 105A, supplied by the 12V DC/DC regulator powering the Arria 10 GX FPGA core, has several features that complement the power-saving schemes of the SoC. This includes the DC/DC regulator's integrated 6-bit parallel VID interface used by the Arria 10's SmartVID to control the regulator and reduce FPGA power consumption during both static and dynamic states.

The DC/DC regulator's very low value DC resistance (DCR) current sensing improves efficiency by minimizing power loss in the inductor. Temperature compensation maintains the accuracy or the DCR value at higher inductor temperature.

#### **Customizing The Power Tree**

What if the design's power requirements differ from those of the development kit? In this case, use the LTpowerPlanner PC-based design tool to personalize and optimize a system's power tree.

Start with the suggestions given in the development kit, then easily reorganize power blocks, alter power ratings, compute efficiency and power loss, simulate each power block, select DC/DC regulator part numbers and authenticate a customized solution.

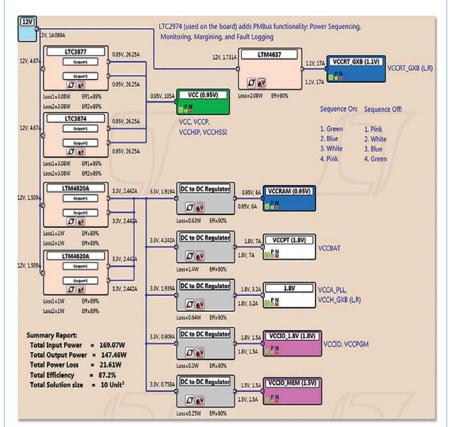

LTpowerPlanner was used to generate the power tree (Figure 3) for the Arria 10 development kit's FPGA and system requirements, and is available within the more encompassing LTpowerCAD design tool (free download from www.linear.com/ltpowercad).

The LTpowerCAD enables users to select specific Linear Technology DC/DC regulators to match a given power specification,

select appropriate components such as inductors, resistors and capacitors, optimize efficiency and power loss, optimize regulator loop stability, output impedance and load transient response, export the design to LTspice, and so on.

This methodical and proven approach simplifies assigning and managing blocks of power in a system with complex multi-voltage rail requirements, needed from the start of a project.

But, what about the more refined, intricate, details? What other power-related topics should a system designer note ahead of time to avoid debugging, spinning the board or, worst case, starting over? Here is a brief discussion of a few of the subjects that typically occupy the time of an engineering team.

#### Capacitors, Transient Response And Output Voltage Ripple

Any load such as a GPU, FPGA or a processor may be subject to randomly high data traffic, experiencing a surge of current that quickly disrupts its steady-state power consumption. This transient in current (or power) consumption affects the output voltage of the DC/DC regulator responsible for powering and regulating the voltage to the load. The output voltage of the regulator droops as it fights to supply the current needed by the device's core, for example, whilst regulating its core voltage. If the regulator is unable to keep up with the demand while supplying the load current, this raises several questions:

- Can the loop response of the regulator be compensated by adjusting the phase margin and bandwidth of the regulator's feedback loop?

- Is a more powerful regulator circuit required?

- Will the addition of more output capacitors remedy the problem? (Capacitors hold charge and help the regulator during load transients.)

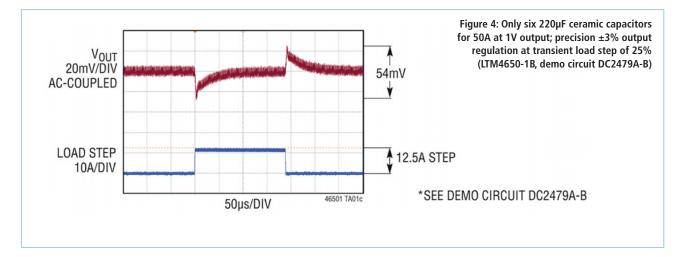

To address these questions is time consuming. These aspects also impact cost and size. There are several power supply design tools that can assist even the inexperienced system engineers. Development boards for FPGAs and supporting engineering materials reduce time spent assessing performance of power management, such as optimizing the transient response and minimizing the number of capacitors needed (Figure 4).

#### Sequencing And Tracking Multi-Voltage Rails

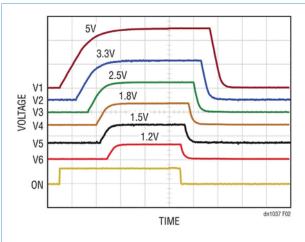

With multiple voltage rails in a system, there is inevitably the question of order. The reverse is also true during system shutdown: which rail is turned off first and which last? The reason is the need for sequential timing between different digital segments of a system, each tasked to perform a job that may

Figure 3: Power tree for Arria 10 GX FPGA board, designed in LTpowerPlanner

depend on the status and "health" of another segment (see Figure 5). For example, should the core voltage be in regulation first, followed by the I/O and then the transceivers? How to ensure one segment does not accidentally start too early or too late and prevent the system from powering up?

Sequencing of power-up is recommended by digital chip suppliers such as Xilinx, Intel (Altera), NXP (Freescale) and others, as is well-known to system engineers. How, then, to best enforce proper sequencing of power for multiple voltage rails?

This task is relatively simple and most DC/DC regulators have this function, sometimes referred to as 'tracking a voltage'. However, knowing how to set up the sequence early in the design and simulate it is most important. It saves retracing PCB layouts or swapping capacitors and resistors later to fix the power-up and power-down timing of the regulators. Performing this exercise early on will enable first-try power-up of a complex multi-rail system.

#### **Scaling Power**

At some point during prototyping most system designers suspect the regulator is unmatched to the load and feature requirements of the system. As a result, most designers over-design, using bigger and more powerful regulators, which occupy more PC board area and cost more, or the load's (FPGA, ASIC, etc) power consumption may be under-reported. A 10A load may suddenly require 30A due to factors such as the number of transceivers in use, faster timing, flow of firmware and algorithms, etc. Is there a way to map the power management, choose the part numbers and do the layout, with assurance that if power requirements change, the change to the power circuit design is simple or at least not overwhelming?

There is a concept of scaling power-up or power-down by adding or removing blocks of regulators. These blocks are pin-compatible, so the layout can be a matter of copying and pasting the same footprint and same part number or device. For example, a power block (or power module) that is capable of delivering 30A per device can have five devices share a current

to deliver 150A (5 x 30A) to a 1V load. The key is to make sure that these power blocks share the current accurately so that no one device is over- or under-used. An over-used device will experience higher temperature rise, possible hot spots and may reach its end of life sooner due to higher thermal stress.

Pin-compatibility is also important because once the layout and pin routing of the device is confirmed, it can be repeated. To ease the prototyping process, using the example of a 150A regulator of 30A per block, a designer can start with all five layouts, populate them and build the board. If board characterization confirms that a lower current, say 115A, is sufficient then instead of five devices, one device for 120A can be removed and prototyping continued.

Or, if after starting with 110A with four devices in mind, you want to build in some insurance, then lay out a fifth socket, leaving it empty and then testing the board. If later during the board evaluation 120A is needed with board at its full usage, then it's simple enough to assemble the fifth power block on to the empty spot without changing the layout and delaying progress.

## **32A RATED PDU** with 32A IEC 60309 (BS4343) Plugs

Part of the extensive range of 32A Rated PDU from Olson Electronics. Available with UK 13A, IEC 60320 C13 and C19 sockets. Options without Meter, Local Power Meters or Remote Power Monitoring

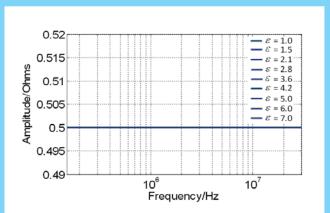

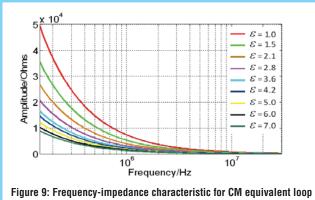

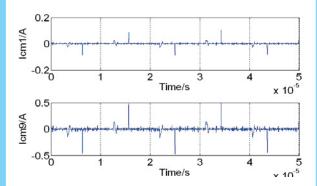

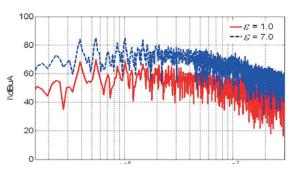

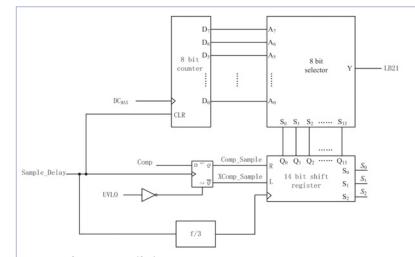

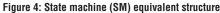

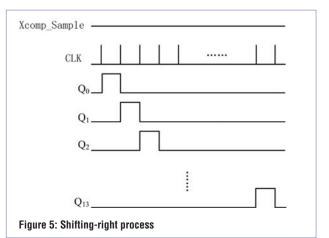

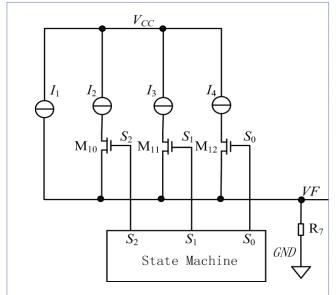

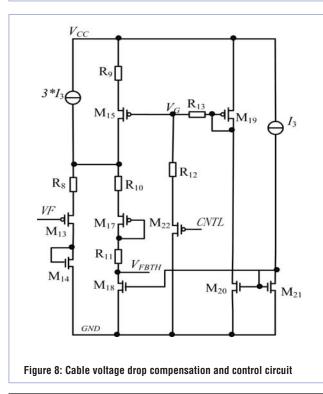

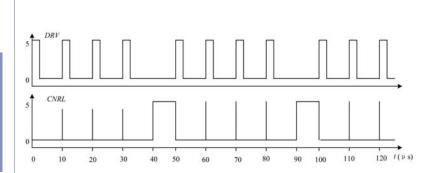

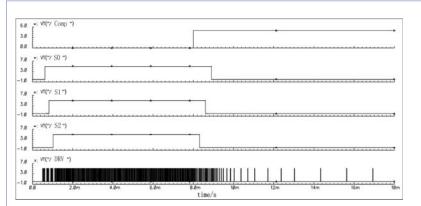

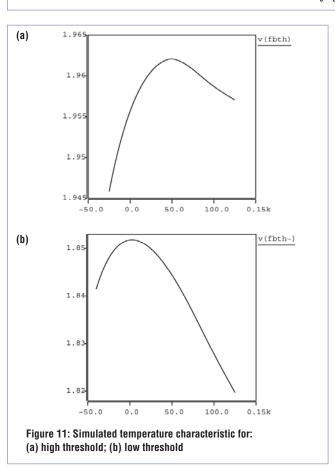

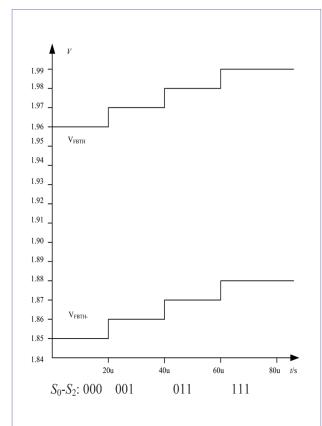

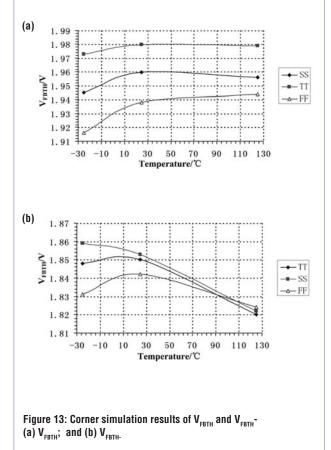

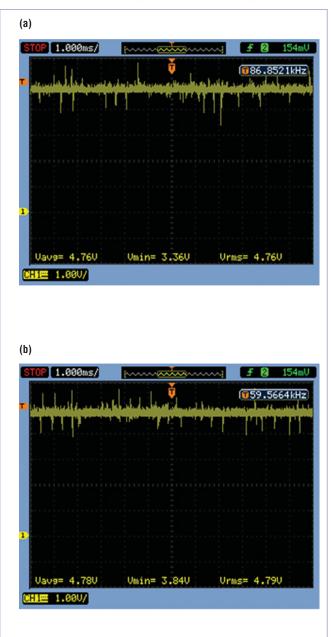

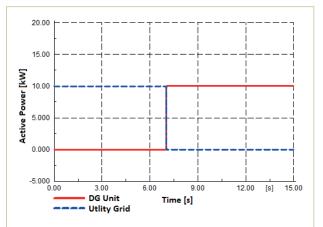

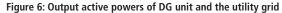

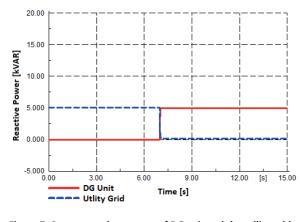

|  | ACCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT<br>CONCEPT |  |  |  |  |  | PM10/LH/32/3M |