£5.90

# Electronics WORLD

THE ESSENTIAL ELECTRONICS ENGINEERING MAGAZINE

TIM9100 EMMERCENTER

is land sealing

DANGER TO LOAD

## Special Report: Low Power Design:

- New field-programmable analogue array

- Line-based compressive sensing

- Energy harvesting

#### **INSIDE THIS ISSUE**

#### Latest

Silicon breakthrough will lead to new high-performance bendable electronics

#### **Embedded**

MicroPython and the Lonely32

#### **Digitisers**

Using probes and sensors with modular digitisers Also inside;

\* CURRENT-MODE

FULL BALANCED

NTH-ORDER

LEAPFROG LADDER

FILTER

## DO YOU WANT THE BEST ELECTRONICS DESIGN SOFTWARE?

#### **FEATURES**

- Schematic Capture

- PCB Layout

- Gridless Autorouting

- 3D Visualization

- M-CAD Integration

- SPICE Simulation

- MCU Co-simulation

- Built in IDE

- Visual Programming

abcenter∧∧

www.labcenter.com

nics

Tel: +44 (0)1756 753440

### **CONTENTS**

#### **REGULARS**

04 > Trend

Future trends in the battery industry

05 > Technology

42 > Products

#### **COLUMNS**

06 > Digitisers

By Oliver Rovini and Greg Tate, Spectrum Instrumentation

08 > PCB cleaning

By Mike Jones, MicroCare

12 > Embedded design

By Dr Dogan Ibrahim, Near East University, Cyprus

16 > MCUs

By Lucio di Jacio, Microchip Technology

#### **FEATURES**

19 > Micropower zero-drift op-amp enables wireless current sense

By Kris Lokere, Strategic Applications Manager, Signal Conditioning Products, Analog Devices

22 > CDTA-based resistorless current-mode full balanced nth-order leapfrog ladder filter

By Jun Xu, Hunan University, China

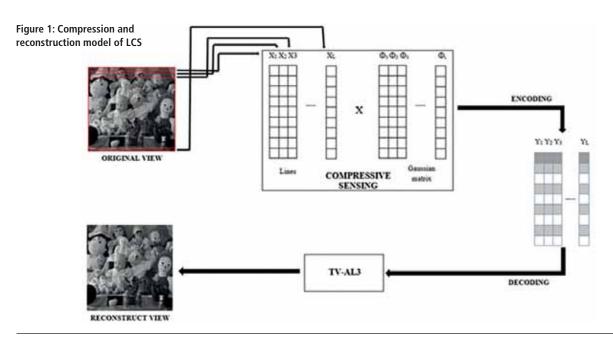

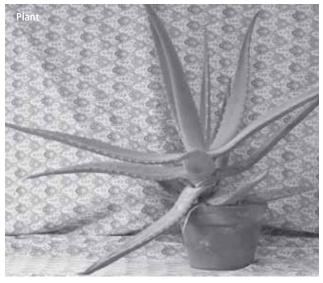

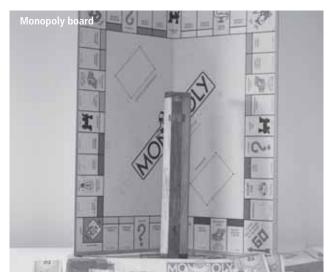

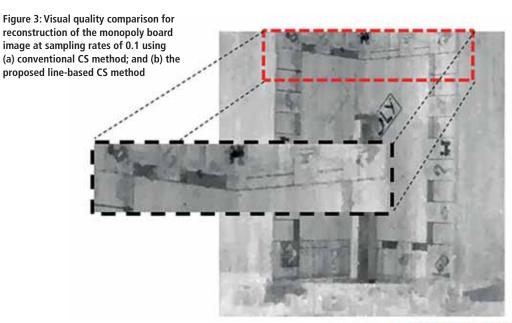

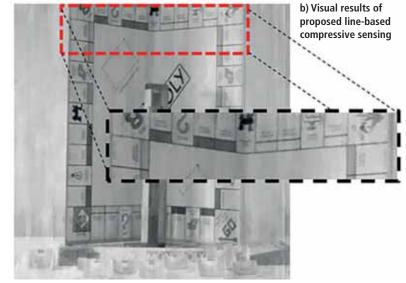

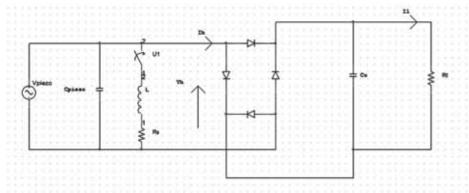

26 > Line-based compressive sensing for low-power visual applications

By Mansoor Ebrahim, Sunway University, Malaysia, and Syed Hasan Adil, Daniyal Nawaz and Kamran Raza, Iqra University, Pakistan

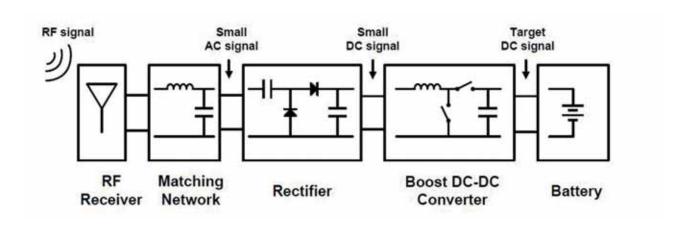

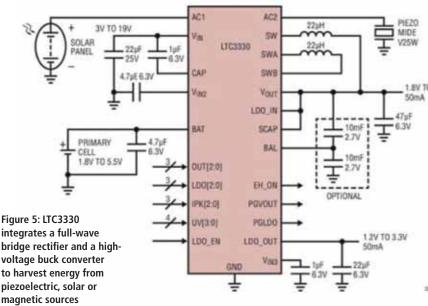

30 > Design of low-power DC-DC converters for energy harvesting

By Maurizio di Paolo, Technical Writer based in Italy

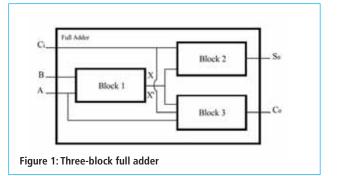

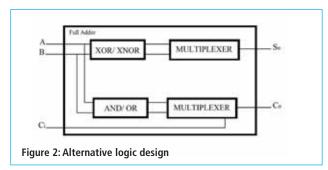

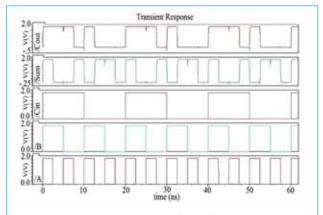

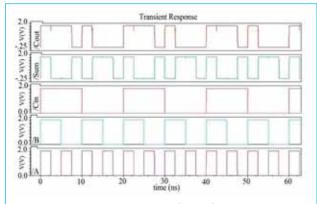

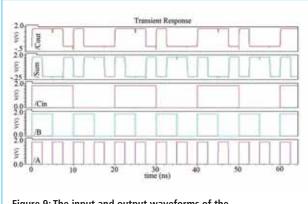

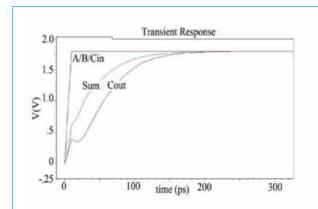

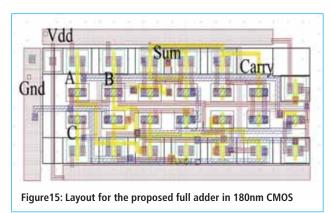

33 > A fully-restored 26-T full adder for energy-efficient arithmetic applications

> By Dr. Shabbir Majeed Chaudhry, Assistant Professor, Department of Electrical Engineering at the University of Engineering and Technology in Taxila, Pakistan

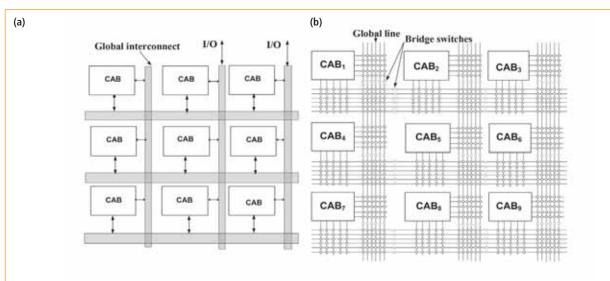

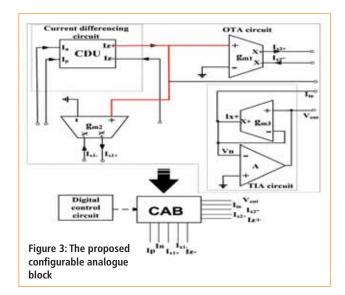

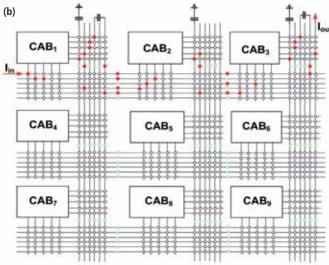

37 > Applications for a new fieldprogrammable analogue array based on current differencing transconductance amplifiers

By Haizhen He and Rongming Luo, Hunan University, Changsha, China

Disclaimer: We work hard to ensure that the information presented in Electronics World is accurate. However, the publisher will not take responsibility for any injury or loss of earnings that may result from applying information presented in the magazine. It is your responsibility to familiarise yourself with the laws relating to dealing with your customers and suppliers, and with safety practices relating to working with electrical/electronic circuitry – particularly as regards electric shock, fire hazards and explosions.

## FUTURE TRENDS IN THE BATTERY INDUSTRY

One could almost see the parallels between diamonds and batteries. A diamond is formed under extremely high pressure and is the world's most valuable gemstone. Likewise, battery technology is developing under increased pressure from end users and manufacturers, while remaining one of the most valuable components in electronic devices.

Three top trends are shaping the way batteries are developed: Safety concerns are leading battery manufacturers to re-think their active materials and cell construction techniques. Increase in wearable devices is driving the trend for batteries with increased power density, and the growing battery 'grey' market is making battery manufacturers conscious of end-user safety.

#### **Safety Concerns**

Recent battery scandals have caused concern about the safety of lithium-ion batteries. The US Federal Aviation Administration (FAA) recently prohibited certain smartphones on their flights, which were at risk of exploding. Design flaws in the battery caused the separator between the positive and negative tabs to break down. This meant the battery short-circuited, overheated, and in some cases caught fire. Following this controversy, researchers at Stanford University suggested introducing flame-retardant material into Li-ion batteries to prevent fires caused by overheating.

Electronic device Original Equipment Manufacturers (OEMs) need to ensure that the batteries they are purchasing meet the latest international standards for safety and performance, which means checking that requirements are met both at a cell- and battery-level.

Suppliers of batteries should work under strict design control because if a seemingly trivial design change has not been properly validated it can have damaging consequences further down the supply chain.

#### **Wearable Devices**

The Consumer Electronics Show (CES) in Las Vegas last January saw an abundance of wearable health and fitness devices. From sleep-tracking headphones to an infrared thermometer with a smartphone app, the show confirmed that the wearable device market continues to grow.

Now, battery manufacturers face the challenge of making smaller batteries that deliver longer runtimes.

To meet this demand, scientists have recently created what has been dubbed the "bendy" battery, a flexible battery containing aluminium and graphite foam, surrounded by liquid salt. The battery has attracted a lot of interest from manufacturers for its lightweight design and potential for use in powering flexible displays. However, there is still a long way to go, as the bendy battery currently only delivers half the voltage of a lithium-ion hattery

#### The 'Grey' Market

The use of batteries for life-critical devices, whether in the medical or military sector, has led to increasing safety and security concerns. This is combined with the global rise in counterfeiting and the battery 'grey' market, with counterfeit goods accounting for almost 2.5% of global imports.

Counterfeit batteries pose a risk of overheating or catching fire, as well as not delivering a reliable performance. To counter this, some battery makers, such as Accutronics, use algorithmic security in their smart batteries; meaning, if a counterfeit battery is inserted into a properly-equipped device, it can display a warning message or shut down completely.

Counterfeit batteries often look identical to branded batteries, so OEMs must look for security features such as this to protect their devices from battery counterfeiting.

#### **Meeting Needs**

The demand for more energy-dense yet smaller batteries means that the battery market is looking for ways to stay ahead of the needs of device OEMs. Also driven by concerns over counterfeiting and the grey market, battery manufacturers are looking to innovate sustainably and safely. It is clear that this pressure is creating a 'diamond' of the global battery market, expected to be worth over \$17bn by 2021.

#### By Michele Windsor, global marketing manager, Accutronics (www.accutronics.co.uk)

#### EDITOR: Svetlana Josifovska

Tel: +44 (0)1732 883392 Email: svetlanaj@electronicsworld.co.uk

#### **SALES: Suzie Pipe** Tel: +44 (0)20 8306 0564

Mobile: +44 (0)7799 063311 Email: suziep@electronicsworld.co.uk

DESIGN: Tania King

PUBLISHER: Wayne Darroch

ISSN: 1365-4675 PRINTER: Buxton Press Ltd

2nd Floor, 52-54 Gracechurch Street, London, EC3V 0EH

#### SUBSCRIPTIONS:

Subscription rates:

UK - 1 year digital only £53.00+VAT

UK - 1 year print and digital sub £68.00

UK - 2 year print and digital sub £109.00 UK - 3 year print and digital sub £143.00

International - 1 year digital only £53.00

International - 1 year print and digital sub £164.00 International - 2 year print and digital sub £290.00

International - 3 year print and digital sub £409.00

Tel/Fax +44 (0)1635 879361/868594

Email: electronicsworld@circdata.com www.electronicsworld.co.uk/subscribe Follow us on Twitter @electrowo

Join us on LinkedIn

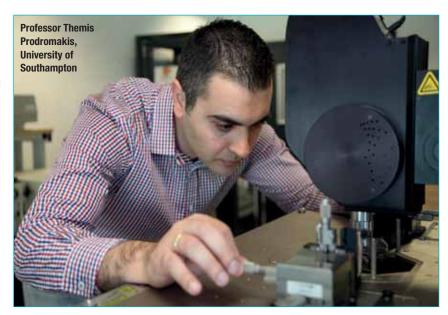

#### SCIENTISTS MANIPULATE THE MEMRISTOR TO CREATE NEW TYPE OF ELECTRONICS

Scientists at the University of Southampton believe that memristors could start a new era of electronics. Being smaller and simpler than transistors, with lower energy and the ability to retain data by 'remembering' the amount of charge that has passed through them, memristors can bring computers that switch on and off instantly and never lose data.

The researchers have found a way to alter memristor resistance and make it store up to 128 discernible memory states per switch, almost four times more than previously reported. They managed to alter the memristor's resistance by reconfiguring its core component, an oxide material.

"This is a really exciting discovery, with potentially enormous implications for modern electronics. By 2020 there are expected to be more than 200 billion interconnected devices within the Internet of Things ecosystem, generating an incredible amount of data that will need processing," said Themis Prodromakis (pictured), Professor of Nanotechnology and EPSRC Fellow at the University of Southampton.

Memristors are a key enabling technology for next-generation chips, which need to be highly

reconfigurable yet affordable, scalable and energyefficient.

Prodomakis added: "Working with industry, we'll bring innovations into new electronic systems that require bespoke customisation, systems that can

be employed in inaccessible environments like inside the human body, space or other remote or harsh locations. At the same time, this technology is ideal for developing novel hardware that can learn and adapt autonomously, much like the human brain."

#### SILICON BREAKTHROUGH COULD LEAD TO HIGH-PERFORMANCE BENDABLE ELECTRONICS

University of Glasgow engineers have developed a new method of creating bendable silicon chips that could pave the way for a new generation of high-performance flexible electronic devices.

The University's Bendable Electronics and Sensing Technologies (BEST) scaled up the established processes for making flexible silicon chips to the size required for delivering highperformance bendable systems in the future.

They made an ultrathin silicon wafer that delivers high-performance computing yet remains flexible. The process has been demonstrated with wafers four inches in diameter, but it can be implemented for larger wafers as well. The team transferred several different types of ultra-thin silicon chips of around 15 microns thick onto flexible substrates; for comparison, a human blood cell is about five microns across.

The scale was proven to be sufficient for

manufacturing ultra-thin silicon wafers capable of

delivering satisfactory computing power.

"Silicon-based circuits have advanced in complexity with remarkable speed since their initial development in the late 1950s, making today's world of high-performance computing possible. However, silicon is a brittle material that breaks easily, which makes it very difficult to use in bendable systems on anything other than nano scale," said Professor Ravinder Dahiya, head of the BEST group.

Flexible electronics is projected to be worth \$300bn by 2028. These systems have many potential applications, including implantable electronics, bendable displays and wearable technology that provides constant feedback on users' health. The BEST group has already made significant progress in wearable technology, including a flexible sensor with accompanying smartphone app that provides feedback on the pH levels of users' sweat.

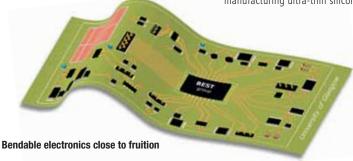

# Using probes and sensors with modular digitisers

BY **OLIVER ROVINI** AND **GREG TATE**. SPECTRUM INSTRUMENTATION

ensors or transducers convert physical phenomena into electrical signals, and probes convert signal levels, change impedances and offer convenient connections; examples include current probes, accelerometers and photomultipliers.

#### **Probes**

Most passive oscilloscope probes work with digitiser inputs, but they change the circuit whilst probing.

Figure 1 shows a 1M $\Omega$  input of a digitiser connected to a measurement point using a coaxial cable. A digitiser's input capacitance is typically about 35pF, and a coaxial cable 10-30pF per foot, which means the total capacitance of this setup is about 95pF, hence the capacitive reactive (Xc) for a 95pF capacitance at 10MHz is:

$$X_{\rm C} = \frac{1}{2\pi f C}$$

Figure 1: Simplified schematic showing a direct connection using a coaxial cable

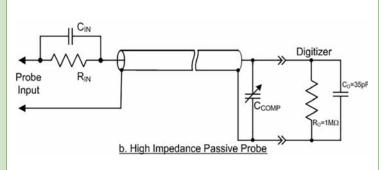

Figure 2: Simplified schematic of a 10:1 high-impedance passive probe

At 10MHz, 95pF results in an impedance of 168 $\Omega$ , which can significantly attenuate the measured voltage. This means that using a shielded cable to connect the digitiser to the device being measured loads down the circuit with this capacitance.

#### High-Impedance Passive Probes

High-impedance passive probes use a capacitively-compensated voltage divider that divides the amplitude by a factor of (typically) ten to one (10:1). This will result in an input capacitance of 10pF minimum with times-ten attenuation, increasing the probe loading resistance by approximately 10x; see Figure 2.

Input capacitance can be further reduced by increasing the probe attenuation, but this will reduce the signal coming into the digitiser and make it more difficult to measure small signals. In practice, 10:1 attenuation generally represents a good compromise between signal amplitude and loading impedance.

A high-impedance passive probe can have a bandwidth of up to 500MHz, and at higher frequencies even a lower value of probe capacitance can be too much. At 500MHz with a 10pF probe capacitance, the input impedance is about 32 $\Omega$ , loading down all but the lowest-impedance circuits; at lower frequencies, this is less of a problem.

The probe also attenuates the input voltage by a factor of 10, which must be accounted for in the digitiser output.

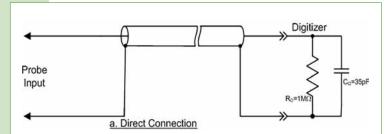

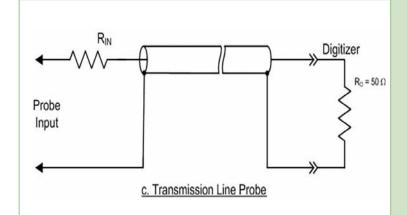

#### Transmission-Line (Low Capacitance) Probes

High-frequency measurements require probes with very low input capacitance, which can be drastically reduced by considering the coaxial cable as a transmission line. If the digitiser input is terminated in  $50\Omega$ , the impedance looking into the probe end of the cable is a constant  $50\Omega$ , independent of frequency. This very-low loading impedance can be increased using a voltage divider. A  $450\Omega$  series-resistor will divide the amplitude ten times and result in a relatively constant loading impedance of  $500\Omega$ . A low capacitance or transmission-line probe (Figure 3) uses a terminated transmission line.

The input capacitance of a transmission-line probe such as this is quite low, typically about a fraction of a pF; however, the limiting factor with this probe is the low input resistance. For a 10x probe, the input resistance is only 500 $\Omega$  and may load circuits too heavily.

Transmission-line probes find application in high-frequency designs, where circuits normally run on  $50\Omega$  traces.

#### **Active Probes**

An active probe uses a compensated voltage divider driving an amplifier. The buffered output of the amplifier drives a coaxial cable terminated in its characteristic impedance just like the transmission-line probe. Here, it also isolates the probe from the cable's capacitive loading and the input circuitry of the digitiser.

Active probes are normally powered and controlled by an oscilloscope; to use them with a digitiser, the probe needs a standalone power supply and, if necessary, a control interface.

#### Selecting Passive Probes

High-impedance passive probes are available in several attenuation factors, with 10:1 and 100:1 the most common. Working into the digitiser's 1M $\Omega$  input termination, they offer 10M $\Omega$  or 100M $\Omega$  input resistance. Digitisers with 14- to 16-bit resolution are well matched to the 100:1 probes, since they have sufficient dynamic range to show small signals after the probe attenuation.

Probes must be matched to the input capacitance of the digitiser. For a digitiser channel with a 35pF input capacitance, a probe with a compensation range covering that capacitance must be used.

Most high-impedance passive probes use BNC connectors. It's great if the digitiser has BNC inputs, but BNC connectors need a lot of space and digitiser front panels are often very small, so an adapter should be used. For example, if the digitiser uses SMA

It's great if the digitiser has BNC inputs, but BNC connectors need a lot of space and digitiser front panels are often very small, so an adapter should be used

connectors, then an SMA-to-BNC adapter is required to mate with the probe.

Transmission-line probes work into the digitiser's  $50\Omega$  input termination. Because these

probes generally support bandwidths into the GHz range, they usually use SMA connectors.

#### Sensors

Sensors or transducers are sensitive to a physical property and convert it into a voltage level proportional to the value of the property being measured. A common example is a current probe, which converts current to voltage, with the voltage level proportional to the measured current level.

Matching a sensor or transducer to the digitiser requires knowledge of the sensor output range, output impedance, bandwidth and sensitivity. The output range must be within the digitiser's voltage range; if not, attenuators or amplifiers may be required to bring it within this range.

Most sensors are designed to work into a fixed impedance. Like other measuring instruments, digitisers generally offer input terminations of 1M $\Omega$  or 50 $\Omega$ . Most broadband transducers are designed to match 50 $\Omega$  load impedance. Lower bandwidth sensors

Figure 3: Simplified schematic for a 10:1 transmission line probe operating into  $50\Omega$  input termination of a digitiser analogue channel

may require a 1M $\Omega$  load. Some specialised transducers can be designed to work into other impedances, such as 75 or 600 $\Omega$ . In these cases, matching pads may be required along with suitable adjustments to the sensor sensitivity.

The bandwidth of the digitiser should be significantly greater than the bandwidth of the sensor to avoid reducing the effective bandwidth of the sensor-digitiser system. A digitiser-to-sensor bandwidth ratio of over 7:1 will result in a 1% or less uncertainty in amplitude measurements.

Sensitivity is the ratio of the given value of the sensor's electrical output to the equivalent measured property. For instance, an accelerometer's sensitivity may be specified as 10mV/g, which means for a measured physical input of 1g, the transducer produces a 10mV signal.

Knowledge of the sensitivity is important when calibrating the digitiser to read in the measured units rather than electrical units.

Most transducers require a saparate power source, which is normally external to the digitiser. lacktriangle

#### FREE BOOKS

This article is adapted from

"The Digitizer Handbook –

Precision and Performance in PC

Instrumentation" by Spectrum

Instrumentation.

To receive a free copy, go to

https://spectrum-instrumentation.com/en/contact-us and tick the box marked "Please send me a copy of the Digitizer Handbook", adding "EW" in the Comment section.

### Working the wetting index for the right cleaning choice

#### BY MIKE JONES, VICE PRESIDENT, MICROCARE

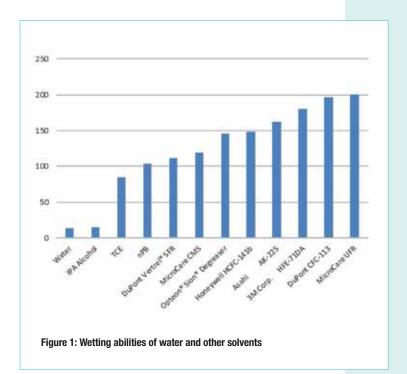

hoosing the correct cleaning chemical for a job can be confusing, especially with so many options to choose from. Fortunately, there's a 'secret weapon' that can help predict how good a cleaner can be, called the 'wetting index'. This index is a measure of a fluid's ability to clean complex shapes, calculated quickly from the product's specification or datasheet.

"Wetting" refers to the liquid's ability to remain in contact with a surface; there's a general rule that "it can't clean if it can't

Modern planet-friendly solvents do a much better job cleaning small, delicate or intricate shapes

wet", hence better wetting means better cleaning. The relative capacity of a fluid to wet a surface can be measured with the wetting index, which combines the relevant chemical characteristics to predict the quality of the cleaning.

Evaluating a cleaning

solution's ability to penetrate between parts is particularly important in the electronics industry, where components are getting smaller and more complex. More densely populated circuit boards make managing faults, quality and product longevity highly challenging. This is the reason so many companies consider their PCB cleaning a mission-critical process: if the cleaning is not effective, the device will simply not function reliably over its required life. It is also important to remember that wettability should be considered even for relatively flat surfaces, since agents with better wettability will penetrate more layers of soil and better lift particles off surfaces.

#### Accessing the 'Wet Index'

As Figure 1 shows, the cleaning abilities of water are not sufficient for today's modern electronics. Although waterbased cleaning was once the preferred choice, this perception has changed, and many manufacturers are now opting for solvent cleaning because they find it more effective, flexible, less expensive and more suitable for cleaning smaller spaces. Water has a very poor wetting index, a function of its inherent molecular structure, whereas modern planetfriendly solvents do a much better job of cleaning small, delicate or intricate shapes.

The surface tension of water is the highest of any cleaning agent available. The high surface tension results in a low wetting index - a score of only 14. For modern, nonflammable solvents it is 100 or higher, making solvent cleaning faster, more consistent and easier to use.

Solvents outperform other cleaning methods because of the very-low surface tension, high density and low viscosity of the different fluids:

- Low surface tension means the solvent can get into tight spaces more easily than solvents with high surface tensions (like aqueous systems).

- A heavy solvent can literally 'float away' contamination that other types of cleaning agents cannot move.

- A solvent with low viscosity flows in and around objects more effectively than solvents with high viscosity due to their greater fluid consistency.

Combining the density, viscosity and surface tension of a solvent into an index score gives a number on the wetting index. The higher the score, the better the cleaning.

The formula for calculating the wetting index is:

#### (Density x 1000)

#### (Surface Tension x Viscosity)

To improve the wetting index score of water-based cleaners, a surfactant can be added to lower the surface tension; but, even then, the surface tension will still be twice that of any solvent.

The viscosity of water or other inefficient cleaners like Isopropyl Alcohol (IPA) also works against good cleaning. Higher viscosities mean the solvent will not flow into tight spaces easily, and if water gets into small crevices it may not come out, resulting in an ineffective cleaning effort. Modern solvents are heavier - typically 20-30% heavier than water, and over 50% heavier than alcohol, which means solvents can get under particulates and lift them off the surface.

Working out the wetting index scores will give a clearer indication of a cleaner's ability to do its job well. Knowing the score through a simple calculation will save time and money, since the right cleaning solution will be chosen, and clean effectively first time.

#### FANTASTIC MODERN POWER SUPPLY ONLY IU HIGH PROGRAMMABLE

| LAMBDA GENESYS<br>LAMBDA GENESYS | PSU GEN100-15 100V 15A Boxed As New<br>PSU GEN50-30 50V 30A |          |        |  |

|----------------------------------|-------------------------------------------------------------|----------|--------|--|

| IFR 2025                         | Signal Generator 9kHz - 2.51GHZ Opt 04/11                   |          | 0002   |  |

| Marconi 2955B                    | Radio Communications Test Set                               |          | 0083   |  |

| R&S APN62                        | Syn Function Generator 1HZ-260KHZ                           |          | 2195   |  |

| HP3325A                          | Synthesised Function Generator                              |          | £195   |  |

| HP3561A                          | Dynamic Signal Analyser                                     |          | £650   |  |

| HP6032A                          | PSU 0-60V 0-50A 1000W                                       |          | £750   |  |

| HP6622A                          | PSU 0-20V 4A Twice or 0-50V 2A Twice                        |          | £350   |  |

| HP6624A                          | PSU 4 Outputs                                               |          | £350   |  |

| HP6632B                          | PSU 0-20V 0-5A                                              |          | £195   |  |

| HP6644A                          | PSU 0-60V 3.5A                                              |          | £400   |  |

| HP6654A                          | PSU 0-60V 0-9A                                              |          | €500   |  |

| HP8341A                          | Synthesised Sweep Generator 10MHZ-20GHZ                     |          | £2,000 |  |

| HP83731A                         | Synthesised Signal Generator 1-20GHZ                        |          | £1,800 |  |

| HP8484A                          | Power Sensor 0.01-18GHZ 3nW-10uW                            |          | 275    |  |

| HP8560A                          | Spectrum Analyser Synthesised 50HZ - 2.9GHZ                 |          | £1,250 |  |

| HP8560E                          | Spectrum Analyser Synthesised 30HZ - 2.9GHZ                 |          | £1,750 |  |

| HP8563A                          | Spectrum Analyser Synthesised 9KHZ-22GHZ                    |          | £2,250 |  |

| HP8566B                          | Spectrum Anaisyer 100HZ-22GHZ                               |          | £1,200 |  |

| HP8662A                          | RF Generator 10KHZ - 1280MHZ                                |          | £750   |  |

| Marconi 2022E                    | Synthesised AM/FM Signal Generator 10KHZ-1,0                | 1GHZ     | £325   |  |

| Marconi 2024                     | Synthesised Signal Generator 9KHZ-2.4GHZ                    |          | 0082   |  |

| Marconi 2030                     | Synthesised Signal Generator 10KHZ-1.35GHZ                  |          | £750   |  |

| Marconi 2305                     | Modulation Meter                                            |          | £250   |  |

| Marconi 2440                     | Counter 20GHZ                                               |          | 2295   |  |

| Marconi 2945/A/B                 | Communications Test Set Various Options                     | £2,000 - | €3,750 |  |

| Marconi 2955                     | Radio Communications Test Set                               |          | €595   |  |

| Marconi 2955A                    | Radio Communications Test Set                               |          | £725   |  |

| Marconi 6200                     | Microwave Test Set                                          |          | £1,500 |  |

| Marconi 6200A                    | Microwave Test Set 10MHZ-20GHZ                              |          | 21,950 |  |

| Marconi 6200B                    | Microwave Test Set                                          |          | £2,300 |  |

| Marconi 6960B with               | 6910 Power Meter                                            |          | £295   |  |

MARCONI 2955B Radio Communications Test Set - £800

CAN BE SUPPLIED WITH OPTIONAL TRANSIT CASE

PROPER 200MHZ ANALOGUE SCOPE - \$250

FLUKE/PHILIPS PM3092 Oscilloscope 2+2 Channel 200MHZ Delay TB. Autoset etc.

| TOTAL DESIGN TO CONTROL OF THE CO. | Country Country at a country                         | 21,000    |

|------------------------------------|------------------------------------------------------|-----------|

| Tektronix TDS3032                  | Oscilloscope 300MHZ 2.5GS/S                          | £995      |

| Tektronix TDS3012                  | Oscilloscope 2 Channel 100MHZ 1 25GS/S               | £450      |

| Tektronix 2430A                    | Oscilloscope Dual Trace 150MHZ 100MS/S               | £350      |

| Tektronix 2465B                    | Oscilloscope 4 Channel 400MHZ                        | 0003      |

| Farnell AP60/50                    | PSU 0-60V 0-50A 1KW Switch Mode                      | £195      |

| Farnell H60/50                     | PSU 0-60V 0-50A                                      | £500      |

| Farnell XA35/2T                    | PSU 0-35V 0-2A Twice Digital                         | £75       |

| Fameli LF1                         | Sine/sq Oscillator 10HZ-1MHZ                         | £45       |

| Racal 1991                         | Counter/Timer 160MHZ 9 Digit                         | £150      |

| Racal 2101                         | Counter 20GHZ LED                                    | £295      |

| Racal 9300                         | True RMS Millivoltmeter 5HZ-20MHZ etc.               | £45       |

|                                    |                                                      | £75       |

| Racal 9300B                        |                                                      | 0.000     |

| Fluke 97                           |                                                      | €75       |

| Fluke 99B                          | Scopemeter 2 Channel 100MHZ 5GS/S                    | £125      |

| Gigatronics 7100                   | Synthesised Signal Generator 10MHZ-20GHZ             | £1,950    |

| Seaward Nova                       | PAT Tester                                           | £95       |

| Solartron 7150/PLUS                | 6 1/2 Digit DMM True RMS IEEE                        | £65/£75   |

| Solatron 1253                      | Gain Phase Analyser 1mHZ-20KHZ                       | £600      |

| Tasakago TM035-2                   | PSU 0-35V 0-2A 2 Meters                              | £30       |

| Thuriby PL320QMD                   | PSU 0-30V 0-2A Twice                                 | £160-£200 |

| Thurlby TG210                      | Function Generator 0.002-2MHZ TTL etc Kenwood Badged |           |

| HP33120A                           | Function Generator 100 microHZ-15MHZ                 | £260-£300 |

| HP53131A                           | Universal Counter 3GHZ Boxed unused                  | £500      |

| HP53131A                           | Universal Counter 225MHZ                             | £350      |

| HEDGIGIN .                         | OTHERSON COUNTRY SESSION                             | 1.000     |

INDUSTRY STANDARD DMM ONLY £325 OR £275 WITHOUT HANDLE AND BUMPERS

Tektronix TDS3052B/C Oscilloscope 500MHZ 2.5GS/S

HP 34401A Digital Multimeter 6 1/2 Digit

YES! AN HP 100MHZ SCOPE FOR ONLY £75 OR COMPLETE WITH ALL ACCESSORIES \$125

£1,500

HP 54600B Oscilloscope Analogue/Digital Dual Trace 100MHZ

#### STEWART OF READING

17A King Street, Mortimer, near Reading, RG7 3RS Telephone: 0118 933 1111 Fax: 0118 9331275 USED ELECTRONIC TEST EQUIPMENT Check website www.stewart-of-reading.co.uk (ALL PRICES PLUS CARRIAGE & VAT)

## SWITCHING AND MONITORING HIGH-VOLTAGE DC POWER SUPPLIES

By Pinkesh Sachdev, Product Marketing Engineer, Power by Linear Products, Analog Devices

C power supplies in the hundreds of volts are not as uncommon as one might think. An application that may first come to mind is electric vehicles where Li-Ion battery stack voltages range up to 400V.

But some lesser-known high-voltage applications are in modern fighter aircraft, such as the F-22 Raptor and the F-35 Lightning II, which are primarily powered from 270V DC for faster and precise performance.

Large solar arrays can output 600V or higher, while rectifying AC voltages in industrial motor drives yield DC voltages ranging from 170-680V. And for many years, there has been research and development to move power distribution within a data centre from AC to high-voltage DC (380V or  $\pm$ 190V), lowering power conversion steps, facility footprint and operational costs while easing integration with renewable energy such as solar.

Distributing power at higher voltages lowers current levels, reducing resistive losses (I<sup>2</sup>R), which can be used to reduce cabling weight. All of these high-voltage supplies need to be switched on or off and soft-started into loads. For energy monitoring and optimisation, it is essential to digitally monitor the voltage and current flowing on these high-voltage buses. Any circuit controlling these supplies needs to be galvanically isolated for operator safety and to protect the low-voltage electronics from the dangerously high voltage.

#### **Methods to Control Inrush Current & Monitor Power**

When designing high-voltage supplies, an important goal is to safely control the startup inrush current into the capacitive load, e.g. the DC bus capacitors following a typical bridge rectifier. A simple method to lower inrush current is by using negative temperature coefficient (NTC) thermistors, also known as inrush current limiters, or ICL (Figure 1a). These thermistors start with high resistance (e.g., a few ohms) at

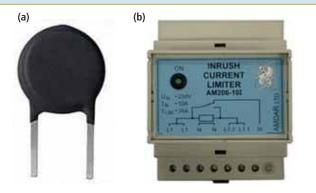

Figure 1: Inrush control limiters: (a) negative temperature coefficient (NTC) thermistor; (b) step-start relay

room temperature before the supply or load is turned on; the high resistance limits the inrush current at turn-on. As current flows, the thermistor heats up and its resistance drops by one to two orders of magnitude (by 10-100x to below an ohm). These thermistors cost anywhere from \$0.13 to \$7 each, depending on current and resistance ratings.

While simple to use, one problem is that a quick power cycling (on-off-on) may not limit inrush on the second power-up if the thermistor didn't have sufficient time to cool down to the high resistance state. NTC thermistors suffer from wide tolerances (±25%), and since the inrush current is tied to the steady state current through the resistance drop ratio, the inrush cannot be flexibly adjusted to arbitrarily low levels. ICLs find applications in vacuum cleaners, fluorescent lamps and switched-mode power supplies, reducing inrush to the bridge rectifier's DC bus capacitors.

To overcome the NTC thermistor downside of no inrush limiting on a quick restart, a shorting relay is used in parallel with the resistor. This is known as a step-start relay (Figure 1b). At turnon, the parallel relay is open and inrush is limited by the resistor. A timer is also started; when it expires, the relay is shorted across the resistor. Load current now flows through the relay. On a quick restart, the step-start relay is able to provide inrush limiting. This technique requires the addition of a shorting relay and a timer to control its turn-on. The increased complexity increases the cost to the \$20-30 range.

Other inrush current control techniques include zero crossing triacs, active power factor control circuits, and inductive input filtering with damping. Most of these are complicated, bulky, expensive and applicable only to AC inputs. One method for isolated current monitoring is by using an isolation amplifier across a current sense resistor and a differential-to-single-ended conversion amplifier feeding an ADC. Another method is to use an isolated delta-sigma ( $\Delta\Sigma$ ) modulator with an external digital filter.

As seen, controlling, protecting and monitoring high-voltage DC supplies requires cobbling many components together and making them work safely and seamlessly. This is not a trivial task. These discrete solutions are large, component-intensive, expensive and lack safety certifications. An integrated and certified solution is needed to shorten design time and certification effort from many months into a few weeks.

#### **Integrated Solution for High Voltage Power Control & Telemetry**

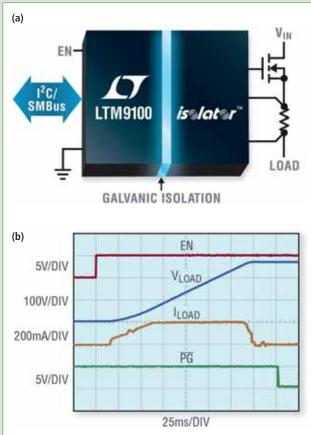

The LTM9100  $\mu$ Module IC is a compact all-in-one solution for controlling, protecting and monitoring high-voltage power supplies up to 1000V DC (Figure 2a). A  $5kV_{RMS}$  isolation barrier separates the logic and digital interface from the switch controller driving an external N-channel MOSFET or IGBT switch. The isolation

Figure 2: (a) LTM9100 Anyside high-voltage isolated switch controller with telemetry; (b) LTM9100 soft-starting a 270V load with controlled 200mA inrush current

is needed for control circuit protection, operator safety and breaking ground paths. The load is soft-started (Figure 2b) and the supply is protected from overload with a current-limited circuit breaker. Isolated 10-bit ADC measurements of load current and two voltage inputs are accessed via the I<sup>2</sup>C/SMBus interface, enabling power, energy and thermal monitoring of the high-voltage bus.

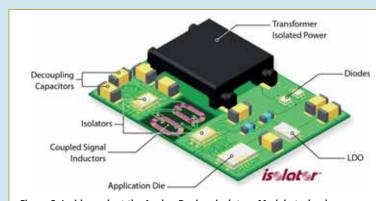

The LTM9100 uses Analog Devices's isolator μModule technology (Figure 3) to translate signals and power across an isolation barrier. Signals are encoded into pulses and passed across the isolation boundary using coreless transformers formed in the µModule substrate, resulting in an extremely robust bidirectional communication scheme. Uninterrupted communication is guaranteed for common mode transients of 50kV/μs. The isolated side is powered by a fully integrated DC/DC converter, including the transformer, eliminating the need for external components. To guarantee a robust isolation barrier, each LTM9100 controller is production-tested to 6kV<sub>RMS</sub>. The LTM9100 will be recognised by the UL 1577 standard, saving months of certification time for the end-equipment manufacturer. High distance through-insulation translates to a high ±20kV ESD level across the barrier. The µModule package integrates several components and technologies to deliver a cost effective, advanced solution that minimises board space and improves

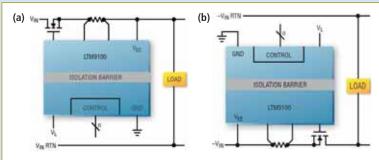

electrical and thermal performance. Due to its isolated nature, the LTM9100 is easily configured for high side, low side (ground return) and floating applications (Figure 4). The LTM9100 is versatile enough to control inrush current not just in hotswappable cards, but also in AC transformers, motor drives and inductive loads. Adjustable undervoltage and overvoltage lockout thresholds ensure that the load operates only when the input supply is in its valid range. The 22mm x 9mm x 5.16mm BGA package provides 14.6mm of creepage distance between the logic and the isolated sides.

#### Conclusion

Traditionally, high-voltage DC supplies are found in industrial environments, but other electronic systems are also moving towards higher voltages to lower costs and raise the efficiency of power distribution, especially in power-hungry systems. These supplies need a simple way to control inrush current, protect themselves and to monitor their usage. The first-of-its-kind LTM9100 delivers this simple and compact solution, beating discrete and relay-based circuits by providing a certified ready-to-go solution, saving board area and multiple months of design time and certification effort. All the needed functionality, including digital telemetry and isolated power, is wrapped in a compact, surface mount and low-profile BGA package.

Analog Devices (UK) Ltd • Tel: 01628 477066 Email: uksales@linear.com • www.analog.com

Figure 3: Inside peek at the Analog Devices isolator  $\mu Module$  technology

Figure 4: LTM9100 in a high-side or low-side switching application

## MikroBUS in embedded applications

By **Dr Dogan Ibrahim**, Professor at Near East University, Cyprus

ikroBUS is a standard originally developed by mikroElektronika to define the interface between a microcontroller or microprocessor development board and integrated circuits or add-on boards. The mikroBUS standard specifies the size and shape of the add-on boards, pinouts, communication and power supply pins used, the

positioning of the mikroBUS socket on the mainboard, and silkscreen marking conventions for both the add-on boards and sockets.

Typically, mikroBUS add-on boards may carry a sensor, transceiver, display driver, encoder, motor driver, relay driver, extension connector, power converter, or other modules or integrated circuits.

MikroBUS is an open standard where its details are available on the Internet, and anyone can implement it, as long as they follow the required specifications.

#### The MicroBUS Standard

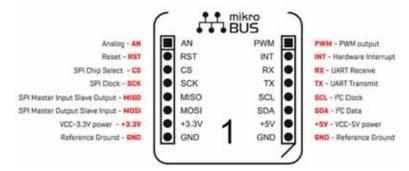

The mikroBUS socket consists of a pair of 1x8 female headers, with their sockets spaced at standard 100mil pitch and indicated with silkscreen markings. As shown in Figure 1, the pinout consists of three groups of communications pins, six additional pins and two power supply groups:

- SPI, UART, and I2C;

- PWM, interrupt, analogue input, reset, and chip select;

- +3.3V and GND (on the left);

- +5V and ground (on the right).

The SPI interface consists of four signals – CS, SCK, MISO and MOSI; the I2C interface of two – SCL and SDA; and the UART also two – Rx and Tx. Analogue input and reset, and the PWM output signals have a pin each. Both +3.3V and +5V outputs are available from a mikroBUS add-on board; there are also two GND pins. It's important to note that not all mikroBUS add-boards have all the specified pins, since this depends on their functionality. However, the power and ground pins are compulsory and always present.

#### **MikroBUS Compatible Boards**

The mikroBUS standard has been so popular that currently there are over 400 mikroBUS compatible add-on boards available, covering a wide range of interface requirements. Although several companies develop and manufacture these boards, the Serbian company mikroElektronika produces at least one mikroBUS-compatible board every week. These boards are also known as 'Click boards', since they are just plugged on top of (or clicked into) the mikroBUS sockets on the microcontroller development boards.

There are many Click boards, with functionalities such as:

- Wireless connectivity;

- Sensors;

- Interface;

- Display;

- Human-machine interface;

- Storage;

- Clock and timing;

- Motor control;

- Mixed signal;

- Power management;

- Shields.

An example is shown in Figure 2; it's an RS232 Click board used to convert standard UART serial communication signals to RS232 signal levels. A 9-pin standard D-type connector on the board provides the RS232 interface.

Figure 3 shows a more complex Click board – the LoRa Click – a long-range radio transceiver add-on board operating at the sub-gigahertz frequency of 868MHz using spread spectrum communications. Communication between the host and add-on boards is through an UART. An external SMA-type antenna can be connected to this board.

A sensor-based Click board, the DHT22 Click, is shown in Figure 4. It uses the DHT22 chip to measure ambient temperature and relative humidity. Communication is through an I2C interface.

#### **Click Board Shields**

In addition to the standard add-on Click boards, many manufacturers such as Microchip and mikroElektronika offer Click board shields that enable these boards to be used with various other development boards, such PIC, Raspberry Pi 3, Arduino Uno, Arduino Mega, STM32F4 Discovery, Intel Joule, and others. Figure 5 shows the Pi 3 Click shield that plugs into a Raspberry Pi 3 computer. It provides two on-board mikroBUS-compatible sockets, extending the selection to over 400 Click boards.

#### **Click Board Compatible Development Boards**

Several manufacturers offer microcontroller development boards with built-in mikroBUS sockets, including PIC Clicker, EasyPIC V7, Clicker 2 for PIC18FJ, PIC32MX Clicker, Clicker 2 for CEC1302, Microchip DM160228, ADM00576, and others.

Figure 6 shows the Clicker 2 for PIC18FJ development board with two mikroBUS-compatible sockets. This is a medium performance 8-bit, 12MIPS (48MHz) microcontroller development board incorporating the PIC18F87J50 microcontroller.

#### **Example Project**

Here we show how a Click board can be used in a microcontroller application. A GPS Click board is used to receive and display the latitude and longitude of the current position on an LCD; see Figure 7.

In this project, the EasyPIC V7 microcontroller development board is used with the LEA-6S-chip-based GPS Click board, plugged into the development board's mikroBUS socket 1. The development board uses the medium-performance PIC18F45K22 microcontroller.

The NMEA sentences generated by the GPS receiver start with the "\$" character, followed by the name of the sentence and then its parameters, with parameters separated by a comma, and a checksum added to the end of a sentence. Sample NMEA sentences generated by the LEA-6S GPS chip are shown in Listing 1.

The \$GPLL sentence in this project is decoded as follows:

\$GPGLL,517.35744,N,0003.13373,E,103109.00,A,A\*65

5127.35744,N Latitude 51 deg. 27.35744 min. North Longitude 000 deg. 03.1276 min. East

10124100 Fix taken at 10:31:09 UTC

A Data valid (V = data invalid)

A Mode (A=autonomous, D=diferential)

\*65 Checksum

We developed the software using the mikroC Pro for PIC language and compiler; see Listing 2.

At the beginning of the program the connection between LCD and microcontroller is defined, and PORTB and PORTC are configured as digital. The UART is initialised to operate at

9600 baud, and after initialising the LCD, the program runs in an endless loop.

At the beginning of the loop, the buffer that holds the GPS data is cleared. The program then reads data from the GPS and looks for the NMEA string "\$GPGLL,". Once detected, the function Uart1\_Read\_ Text is used to read data from the GPS, until the delimiting character "\*" is detected (at the end of the \$GPGLL sentence, just before the

Figure 2: RS232 Click board

Figure 3: LoRa Click board

Figure 4: DHT22 Click board

Figure 5: Pi 3 Click board

Figure 7: Project setup

Figure 8: Sample display

checksum). At this point the buffer contains all the parameters of the NMEA sentence \$GPGLL, starting from the latitude parameter. The remainder of the program extracts the latitude and longitude parameters and loads them into two string arrays, called LAT and LON, respectively. These arrays are then displayed on the LCD after adding the degree signs and spaces. The loop repeats every five seconds.

Figure 8 shows a sample display from the program.

```

$GPRMC,101241.00,A,5127.36070,N,0003.12726,,0.118,,28813,,,A*7F

$GPVTG,,T,M,0.118,N0.218,K,A*0

$GPGGA,01241.00,527.36070,N00003.1272,E,1,06,1.0,40.8,M,4.4,M,,*63

$GPGSA,A,329,02,31,1,25,14,,,,,2.57,1.6,2.01*0C

$GPGSV,,2,09,24,0,142,,25,7,072,21,2967,189,34,1,52,298,3*79

$GPGLL,517.35744,N,0003.13373E,103109.00,A,A*65

```

**Listing 1: Sample NMEA sentences**

```

/*********************

USING THE GPC CLICK

_____

$GPGLL,5127.35744,N,00003.13373,E,103109.00,A,A*65

5127.35744,N

Latitude 51 deg. 27.35744 min. North

00003.1276,E

Longitude 000 deg. 03.1276 min. East

103109.00

Fix taken at 10:31:09 UTC

Data valid

Data autonomous

Checksum

// Define LCD connections

sbit LCD_RS at RB4_bit;

sbit LCD_EN at RB5_bit;

sbit LCD_D4 at RBo_bit;

sbit LCD_D5 at RB1_bit;

sbit LCD_D6 at RB2_bit;

```

```

sbit LCD_RS_Direction at TRISB4_bit;

sbit LCD_EN_Direction at TRISB5_bit;

sbit LCD_D4_Direction at TRISBo_bit;

sbit LCD_D5_Direction at TRISB1_bit;

sbit LCD D6 Direction at TRISB2 bit;

sbit LCD_D7_Direction at TRISB3_bit;

// End of LCD connections

// Start of MAIN program

void main()

unsigned char buffer[50];

unsigned char i,flag,c;

unsigned char Lat[13], Lon[13];

unsigned char gps[]="$GPGLL,";

ANSELB = 0;

// PORTB digital

// PORTC digital

ANSELC = 0;

LCD_Init();

// Initialise LCD

```

#### Rittal - The System.

Faster – better – everywhere.

sbit LCD\_D7 at RB3\_bit;

### QUICK DATA FLOW. EASY WORKFLOW.

**ENCLOSURES**

POWER DISTRIBUTION

```

Uart1_Init(9600);

// Baud rate is 9600

while(1)

// Do forever

for(i = 0; i < 50; i++)buffer[i] = 0;

// Clear the buffer

i=0:

flag=o;

// Read until NMEA sentence "$GPGLL," is detected

//

while(flag == 0)

if(Uart1_Data_Ready() == 1)

c = Uart1_Read();

if(c == gps[i])

{

i++;

if(i == 7)flag=1;

}

else i = 0;

}

// NMEA sentence "$GPGLL," has been detected, now decode it

Uart1_Read_Text(buffer,"*",255);

// Read until "*" detected

if(buffer[37] == 'A')

// If the sentence is valid

Lat[o] = buffer[o];

Lat[1] = buffer[1];

// Latitude degrees

```

```

Lat[2] = 178;

// Degree character

Lat[3] = ";

Lat[4] = ";

for(i=0; i < 6; i++)Lat[5+i] = buffer[2+i]; // Latitude minutes

Lat[11] = buffer[11];

// Latitude direction

Lat[12] = oxo;

// Terminate the string

Lon[0] = buffer[13];

// Longitude Degrees

Lon[1] = buffer[14];

Lon[2] = buffer[15];

Lon[3] = 178;

// Degree character

Lon[4] = ";

for(i=0; i<6; i++)Lon[5+i] = buffer[16+i]; // Longitude minutes

Lon[11] = buffer[25];

// Longitude direction

Lon[12] = oxo; // Terminate the string

Lcd_Cmd(_LCD_CLEAR);

// Clear the LCD

Lcd_Out(1,1,"LAT="); // Display string LAT=

Lcd_Out_Cp(Lat);

// Display the latitude

Lcd_Out(2,1,"LON="); // Display string LON=

Lcd_Out_Cp(Lon); // Display the longitude

}

else

// If data is not valid

{

Lcd_Cmd(_LCD_CLEAR); // Clear the LCD

Lcd_Out(1,1,"DATA NOT VALID"); // Display data is not

valid

}

Delay_Ms(5000); // Wait 5 seconds

}

```

Listing 2: Project program

#### VX25. SYSTEM PERFECTION.

There are always two versions of this enclosure - real and digital. The maximum data quality of the VX25 ensures greater flexibility for configuration, manufacturing and assembly. And with the "digital twin", the person who knows your company best – you yourself – can plan, order, process and do much more besides.

PERFECTION

**SOFTWARE & SERVICES**

MicroPython and the Lonely32

#### BY LUCIO DI JASIO, MICROCHIP TECHNOLOGY

t's been almost a decade since I started adding Python to my daily programming. In the beginning it was only to create small scripts to perform "dirty" jobs, such as converting the odd file format or creating a quick visualisation while debugging a complex embedded application. Python is the kind of (programming) language that is usable and useful almost immediately, but

you can continue learning it for years.

One summer I even tried to join a small community of developers working on PyMite, an open-source project running Python on small microcontrollers. The community developed AVR, dsPIC and several 32-bit versions of the PyMite compiler/interpreter, and I ported it into the very first PIC32 models. The project eventually fizzled out (as many such projects eventually do), when the original author and maintainer changed jobs and lost interest in it; the small group of contributors then dissolved. You can still find PyMite in the Google Code archives today, but another open-source project – MicroPython – has replaced it, achieving much wider popularity.

#### **Constrained Devices**

MicroPython, just like the real Python language, is partly compiled and partly interpreted. The compilation process makes the executable code very compact, which is great for the constrained devices used in embedded control. And even more so, since the executable code is not based on the machine language of any particular architecture but is designed to be interpreted at run-time.

The Python interpreter understands and directly manipulates objects and complex data structures. This is in stark contrast to other, similar languages such as Java for example, where the virtual machine is limited to relatively low-level instructions and data structures. Unfortunately, this means that the interpreter can be quite large, using a lot of RAM and (worse) making extensive use of dynamic memory allocation. None of these characteristics bode particularly well for its adoption in the kind of constrained devices used in embedded applications today.

Fortunately, the definition of constrained devices is changing. In the ten years between the PyMite project and MicroPython, 32-bit

Figure 1: MicroPython (old) logo

And since the performance of such devices increases too, could MicroPython soon become viable for general use in embedded control?

#### Wi-Fi SoCs

In the last three years, the small Chinese start-up Espressif has introduced an interesting new concept: a small SoC that integrates a general-purpose embedded application processor with a Wi-Fi radio. While not entirely revolutionary, the company's first new product (ESP8266) has struck a chord with the large community of hackers and hobby developers. This is probably because of the small size of the evaluation modules, but mostly because of the unprecedentedly low price (\$2-5) for what is essentially a small but complete IoT node in a chip!

Even more recently, the company has produced a secondgeneration product (ESP32) that doubles the number of cores on the SoC, with Bluetooth connectivity.

#### Software is Eating the World

As most of you will have experienced, powerful hardware is useless if not matched by a complete software development suite and proper documentation. Like most Chinese companies, this would have been a huge challenge for Espressif if they had not been blessed with an open community of dedicated developers. While the (compiler) tool suite is mostly composed of free components from Tensilica (the vendor of the original IP used by the manufacturer for the 32-bit cores), peripheral libraries and TCP/IP and Wi-Fi stacks have been assembled by a mostly self-organised team of developers. Similarly, the best documentation for the silicon and software libraries has been coming from the open source community.

Yet, developing connected (IoT) applications using Wi-Fi and Bluetooth stacks in C/C++ remains a very complex job that only a minority of embedded developers can tackle; the new low price and reduced size did little to change the hard reality of the matter.

#### MicroPython to the Rescue

It is at this interesting juncture that MicroPython and Espressif paths crossed. Python is a great language for abstracting the kind of complex functionality required by typical IoT, networked applications. In fact, there are many such examples in the general Python libraries and its literature.

It turns out that the 512kB of RAM of the latest ESP32 is sufficient for a MicroPython interpreter, even though part of it must be shared with the Wi-Fi and Bluetooth stacks.

A MicroPython porting to the Espressif SoCs has been in steady development for a while by the community, and a relatively stable version is now available for download from the official website.

#### Taking the Plunge

Recently, I was looking for a MicroPython-capable evaluation board on Amazon and I stumbled upon the LOLIN32 lite model (a product of Wemos Electronics); see Figure 2. To avoid shopping around for a cheaper unit, I shelled out \$12.

Despite it being listed in stock, Amazon immediately and very politely notified me that the actual shipment (to my home office in Germany) would take an extraordinary three weeks! This was annoying, even though, admittedly, I was not in a hurry.

Once the package arrived - quite precisely three weeks later - the unboxing experience begun; or, rather, the "unwrapping", since there was no box. Instead, it was just a ball of bubble-wrap foil, oddly bulging from inside a small bubbly envelope. The envelope itself contained no indication of its origin (fading magic ink?). Nothing intelligible anyway, only my home address (handwritten) was on the envelope, but there was no company branding anywhere to be found. Not even a small sliver of paper, a sticker or any other recognisable marking. Nothing on the inner wrap, either.

Once I cut the strip of scotch tape holding it together, the tiny board literally fell into my hands. My puzzlement grew as I realised that even the board did not bear any markings on either top or bottom. There was simply no silk screen, just a black PCB – a very thin one, in fact. I had to look back at the order page on Amazon and zoom into the product images (Figure 2) to realise that all visible markings had been PhotoShopped; but, the board did match the product I'd ordered.

#### Feeling LONELY

By now, I had already a new nickname for the orphan board, the "Lonely32".

In the absence of any documentation, I followed my worst instinct and decided to do the only thing possible, plug the micro-USB connector into my MacBook and see what would happen. A pretty, blue LED lit up - and no smoke!

The joy produced by the little blue light was not to last long though, since there was no other perceptible feedback coming from the board or the laptop. No new drives appeared (not a USB-MSD

Figure 2: Lolin32 lite

Figure 3: MicroPython "Hello World" message

device) or new serial ports (not a USB-CDC device) - nothing popped up on screen. Nothing! How was I supposed to communicate with the little Python?

So, I went back to the Amazon order page, this time looking for a link to the vendor website. Eventually I found a link to what appears to be a Wiki link, mostly under construction. It offered some encouraging (if basic) information about the board features (four lines), a link to a schematic (a good start!) and a link to a driver download page (which I assumed was for all Windows users).

Strangely, there was no mention of MicroPython, but instead there was a link to a page for "Getting started with Arduino". Unfortunately, even that turned out to be a dead end – an empty page! Had I been duped?

#### **Open Support Odyssey**

After searching for a couple of hours, reading across several forums, many blogs and watching a few videos, I had reached a sad realisation: the only support I could count on was coming from a "community" of desperate souls (like me) that had eventually managed to figure out what to do by proceeding in random steps, much like ants exploring an unknown territory, revealing a complete and utter ignorance of the terrain – for us the technical details of the product at hand.

Often, the resulting recommendations/advice would include unnecessary steps and loops that obviously made no sense, which an "expert" would admit to but recommend keeping "just in case".

To spare you the agony, here's the summary:

- The (in)famous SoC did not have a USB port, so instead the board developers used a serial-to-USB bridge chip of Chinese origin (Winchiphead). This is apparently so cheap and poorly supported that it is the only such device to my knowledge to require a custom USB driver – even on a Mac!

- A version of the driver compatible with recent OSX versions can only be downloaded from Bjorn Sengotta's personal blog!

- Once the driver is installed (this requires full admin rights and a complete reboot), the serial port is exposed to the OS, but the board is still mostly unusable.

- The user is now supposed to install Python on the laptop first, then use standard Python tool (PIP) to download and run a special script (esptool.py) from the command line. Only through this tool the user can for the first time truly communicate with the board SoC. Notice that the user might have to install a second copy/version of a Python (v3) interpreter on his laptop in case the pre-installed version (Macs ship with Python v2.7) doesn't match that of the script.

- Only if the output of the esptool.py script resembles that in Listing 1 do you know the Lonely 32 is indeed alive!

> esptool.py --port /dev/tty.usbmodem14522 flash\_id

esptool.py v2.2

Connecting......\_

Detecting chip type ... ESP32

Chip is ESP32DoWDQ6 (revision o)

Uploading stub...

Running stub...

Manufacturer: c8

Device: 4016

Detected flash size: 4MB

Hard Resetting...

#### Listing 1: Status report: It's alive!

But that's not all. To get from here to a running copy of MicroPython, more commands are needed, installed via the same special Python script, as follows:

- First, erase the SoC companion serial flash memory (Listing 2).

- > esptool.py --port /dev/tty.usbmodem14522 erase\_flash esptool.py v2.2

...

Erasing flash (this may take a while)... Chip erase completed successfully in 3.1s Hard resetting ...

Listing 2: Erasing flash

- Then, access the MicroPython website https://micropython.org.

- Select the download page and choose the latest ESP32 image.

Note this image is not specifically built for the Lonely32 board,

but rather generic to all ESP32 boards. Users will have to hope that the board in their hands is sufficiently compatible (pinout, buttons locations, serial flash memory sizes, etc.) with the MicroPython default.

- Finally, upload to the SoC companion serial flash memory the MicroPython image; see Listing 3.

- > esptool.py --port /dev/tty.usbmodem14522 write\_flash esptool.py v2.2

•••

Configuring flash size...

Autodetected flash size: 4MB

Compressed 935888 bytes to 587151...

Wrote 935888 bytes at 0x1000 in 51.7 seconds

Hash data verified.

Leaving...

Hard resetting...

#### Listing 3: Uploading the MicroPython image

Notice the hexadecimal offset value (0x1000), cross your fingers and pray that it's indeed the correct value for the board! It is at this point, and only at this point, that MicroPython actually starts running.

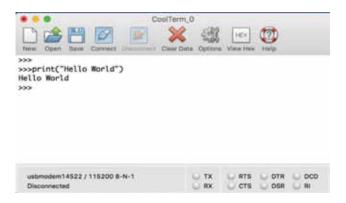

Connecting your favourite serial terminal (CoolTerm in my case) to the virtual serial port (use 115,200 baud), you'll get the first MicroPython command prompt and you'll be able to run your first MicroPython script: "Hello World"!

#### **Following the Money Trail**

While it all ended well and the Lonely32 board proved functional, I was left somewhat bitter after this first experience. If this had been the same experience with a product from any US or European company, there would have been a public outrage, social media mocking and mobs with pitchforks outside their corporate offices. It would have happened regardless of the cost of the tool and the target audience.

Surprisingly, instead, the general response that I could observe on the many forums and social postings was "enthusiastic", to say the least. Is this because we (collectively) have become accustomed to receiving such a poor service from Far Eastern firms that anything that eventually works is celebrated as a great success?

If we follow the money trail to see who's benefitting from this business model, it is interesting to observe that only a small fraction of the SoC price goes to the actual manufacturer (< \$2). A tiny fraction went to the board manufacturer (< \$1), but none to the many people worldwide who contributed with their expertise and hard work to create the software tools, libraries and documentation. Interestingly, it appears that Amazon took the lion's share from this sale – by my estimates, some \$6-8.

Miracles of the global economy, eh?! But, also, a sad moment of reflection about the sustainability of a model that seems to be spreading and gaining acceptance in our industry.

## Micropower zero-drift op-amp enables wireless current sense

By Kris Lokere, Strategic Applications Manager, Signal Conditioning Products, Analog Devices

any current sense circuits follow the same simple recipe: develop a voltage drop across a sense resistor, amplify the voltage, then read it with an ADC to know the current. However, if the sense

resistor is at a voltage that is different from system ground, things can quickly get complicated. Typical solutions bridge the voltage difference in either the analogue or digital domain. Now, there is a different approach – wireless.

High-side current sense amplifiers operate in the analogue domain. The ICs are compact, but the voltage difference they can withstand is limited by semiconductor processes. Devices rated over 100V are rare, and these circuits often lose accuracy if the sense resistor common-mode voltage changes quickly or swings both above and below system ground.

Magnetic or optical isolators usually break the isolation barrier in the digital domain. The hardware can be a bit more bulky, but works without loss of accuracy and can typically withstand thousands of volts. These circuits need an isolated power supply but that can sometimes be integrated into the isolator component. If the sense resistor is physically separated from the main system, you may also need to run long wires or cables.

Recent low-power signal conditioning and wireless technologies offer a new approach. By allowing the entire circuit to float with the common mode of the sense resistor, and transmitting the measured data wirelessly, there are no voltage limitations. The sense resistor can be anywhere, without the need to run cables. If the circuit is very low power, then it won't even need an isolated power supply and can run for many years from a small battery.

#### **Wireless Current Sense**

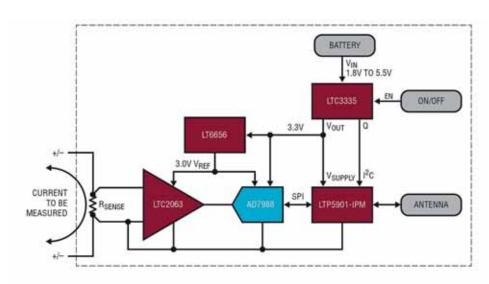

The current sense circuit in Figure 1 employs the LTC2063 chopper-stabilised op-amp to amplify the voltage drop across a sense resistor. The micropower SAR ADC AD7988 digitises the value and reports the result via an SPI interface. The LTP5901-IPM is the wireless module that automatically forms an IP-based mesh network with other nearby nodes. It also has a built-in microprocessor that reads the AD7988 ADC SPI port.

The LTC3335 is a nanopower buck-boost regulator that converts the battery voltage to a constant output voltage. It also includes a Coulomb counter which reports cumulative charge pulled from the battery.

#### Micropower Zero-Drift Op-amp

To minimise heat dissipation in sense resistors, the voltage drop is typically limited to the 10mV-100mV range. To measure this requires an input circuit with low offset errors, such as a zero-drift op-amp.

Figure 1: A low-power wireless current sense circuit

Figure 2: The current sense circuitry floats with the sense resistor voltage

(SOME SUPPLY BYPASS CAPACITORS OMITTED FOR CLARITY)

The LTC2063 is an ultralow power, chopper-stabilised op-amp with a maximum supply current of  $2\mu A.$  Because the offset voltage is less than  $10\mu V,$  it can measure even very small voltage drops without loss of accuracy.

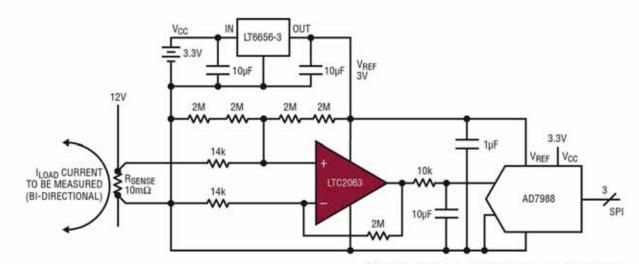

Figure 2 shows the LTC2063 configured to amplify and levelshift the voltage across a 10m $\Omega$  sense resistor. The gain is selected so that ±10mV full-scale at the sense resistor (corresponding to ±1A of current) maps to a near full-scale range at the output, centred around mid-supply. This amplified signal is fed into a 16-bit SAR ADC. At low sample rates, the ADC automatically shuts down in between conversions, resulting in average current consumption as low as 10 $\mu$ A at 1ksps. The LT6656 voltage reference consumes less than 1 $\mu$ A, and biases the amplifier, the level-shift resistors and the ADC's reference input.

#### **Industrial-Strength Wireless Mesh**

SmartMesh wireless modules such as LTP5901-IPM include the radio transceiver, embedded microprocessor and networking software. When multiple SmartMesh motes (wireless nodes), are powered up in the vicinity of a network manager, they automatically recognise each other and form a wireless mesh network. All motes in a network are automatically timesynchronised, which means that each radio is only powered on during very short, specific, time intervals. As a result, each can function as a source of sensor information, as well as a routing node to relay data from other nodes toward the manager. This creates a highly reliable, low-power mesh network, where multiple paths are available from each node to the manager, even though all nodes, including the routing ones, operate on very low power.

The LTP5901-IPM includes an ARM Cortex-M3 microprocessor core, which runs the networking software. In addition, users may write application firmware to perform tasks specific to the user application. In this example, the microprocessor inside the LTP5901-IPM reads both the SPI port of the current measurement ADC (AD7988) and the I<sup>2</sup>C port of the Coulomb

counter (LTC3335). The microprocessor can also put the chopper op-amp (LTC2063) in shutdown mode, further reducing its current consumption from 2µA to 200nA. This provides additional power savings when there are extremely long intervals between measurements.

#### **Nanopower Coulomb Counter**

Typical power consumption for a mote reporting once per second is less than  $5\mu A$  for the measurement circuit and can be  $40\mu A$  for the wireless radio. In practice, power consumption depends on various factors, such as how often the signal chain takes a reading and how the nodes are configured in the network.

The example circuit is powered from two alkaline primary battery cells. The battery input voltage is regulated by the LTC3335 nanopower buck-boost converter with integrated Coulomb counter. It can provide a regulated 3.3V output from an input supply between 1.8V and 5.5V. Load current in duty-cycled wireless applications can vary from 1 $\mu$ A to 20mA, depending on

whether the radio is in active or sleep mode.

Recent lowpower signal conditioning and wireless technologies offer a new approach to current sense circuits

The LTC3335 has a quiescent current of just 68onA at no load, which keeps the entire circuit at very low power when the radio and signal chain are in sleep mode. Still, the LTC3335 can output as much as 50mA, which provides enough power during radio transmit/receive and for a variety of signal chain circuits.

In high-reliability wireless

sensor deployments it is not acceptable for batteries to ever run out. At the same time, replacing batteries too often incurs unwanted downtime and cost. The upshot is that accurate battery drain circuitry is needed. The LTC3335 has a built-in Coulomb

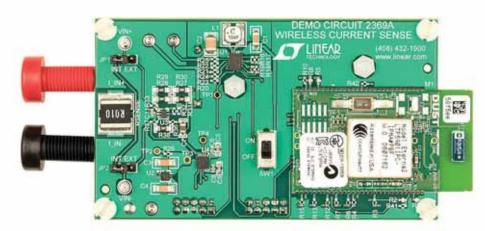

Figure 3: A complete wireless current sense circuit is implemented on a small circuit board

counter. Whenever the regulator switches, it keeps track of the total charge it draws from the battery. This information can be read out using an I<sup>2</sup>C interface, and can then be used as a predictor of the timing for battery replacement.

#### **Example Implementation**

Figure 3 shows an example implementation of a wireless current sense circuit. The ultralow power LTC2063 chopper op-amp can

accurately read small voltage drops across a sense resistor. The entire circuit, including micropower ADC and voltage reference, floats with the common mode of the sense resistor. The nanopower LTC3335 switcher can power the circuit for years from a small battery, while reporting cumulative battery usage with its built-in Coulomb counter. The LTP5901-IPM wireless module manages the entire application and automatically connects to a highly reliable SmartMesh IP network. •

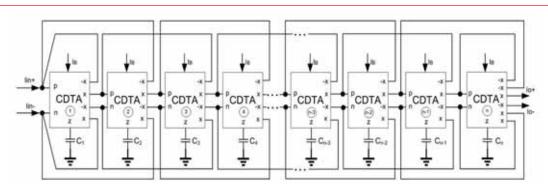

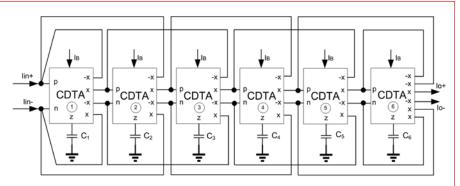

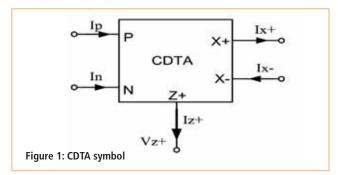

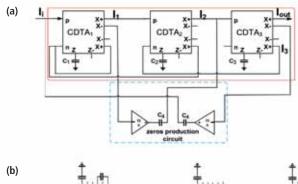

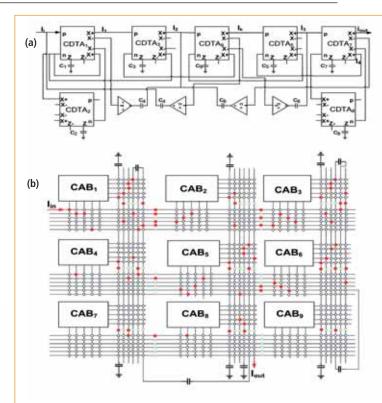

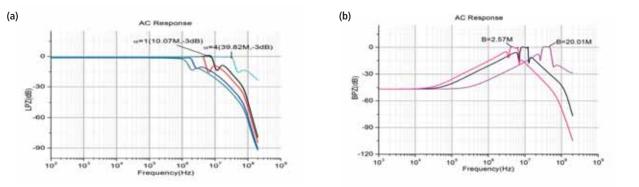

## CDTA-based resistorless current-mode full balanced n<sup>th</sup>-order leapfrog ladder filter

By Jun Xu, Hunan University, China

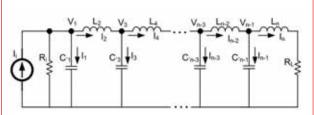

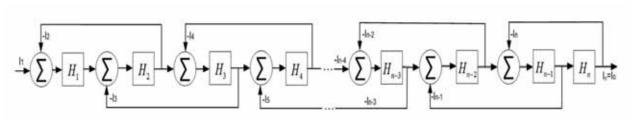

n the past few years, current-mode techniques have received wide attention due to their high slew rate, wide bandwidth, low voltage and low power consumption. Many current-mode devices, such as CCII, CFA and OTA, are widely used in circuit design. Recently, a new current-mode active element with two current inputs and two different current outputs has been introduced - the current differencing transconductance amplifier (CDTA). This device offers wider bandwidth than its close relative, the current differencing buffered amplifier (CDBA), so it has become more widely used in circuits, such as inductance simulators and sinusoidal oscillators, and is especially promising for building current-mode filters. However, for some high-order filters it is not well suited, especially in CDTA-based nth-order filter circuits. Researchers have proposed two types of nth-order currentmode filters using CDBAs.

#### Filter Design

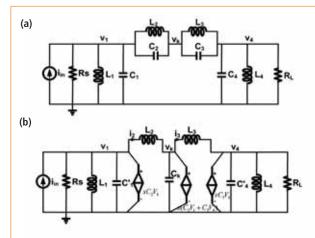

Filters are found in many applications, such as radiofrequency (RF) filters for image rejection, or intermediatefrequency (IF) filters for channel selection in wireless receivers. The design method of a high-order filter is mainly based on cascading second-order filters and negative feedback. The leapfrog structure is one of the most popular choices in active filter design due to its lower sensitivity than the cascade method.

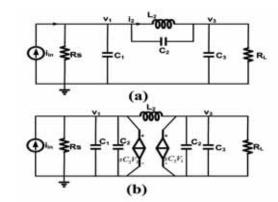

In leapfrog filter simulation of a current-mode ladder network, it is common to use combinations of active and passive components to simulate the inductances and operations of high-order LC ladder circuits.

We propose a circuit that adopts a minimum number of active and passive components to build an n<sup>th</sup>-order filter, which consumes very little power. The circuit has grounded capacitors and no resistors, which is convenient for

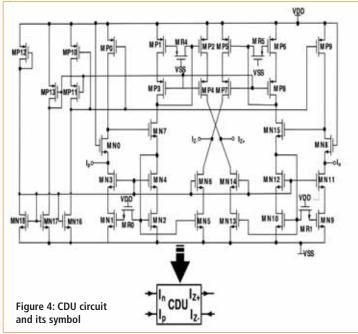

Figure 2: Realisation circuit of a CMOS-based CDTA

integrated circuit (IC) fabrication. This filter can be applied in many fields, including RF transmitters/receivers, phase-locked-loop FM demodulators, wireless communication and instrumentation, among others. It can also be used in the design of active filters instead of the surface acoustic wave (SAW) filters used in GSM systems.

#### **CDTA Realisation**

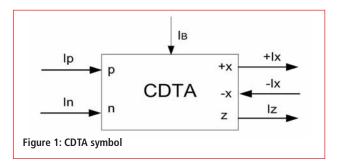

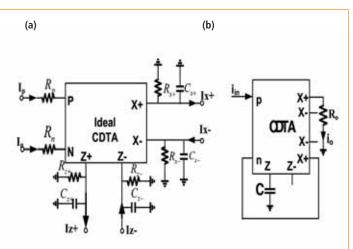

The circuit symbol of CDTA is shown in Figure 1, where p and n are positive and negative current input terminals, and z and x are current output terminals. Its characteristics are:

$$\begin{bmatrix} V_{\rho} \\ V_{\pi} \\ I_{z} \\ I_{z} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 \\ 1 & -1 & 0 & 0 \\ 0 & 0 & \pm g_{m} & 0 \end{bmatrix} \begin{bmatrix} I_{\rho} \\ I_{z} \\ V_{z} \\ V_{z} \end{bmatrix}$$

(1)

where  $V_x = I_z * Z_z$ ,  $g_m$  is the transconductance gain, and  $Z_z$  is an external impedance connected to terminal z. According to Equation 1, current through terminal z follows the difference of the currents through terminals p and p ( $I_p - I_n$ ), and flows from terminal p into impedance p. The voltage drop at terminal p becomes current at terminal p (p) with p<sub>m</sub>, controlled by the external bias current ( $I_B$ ).

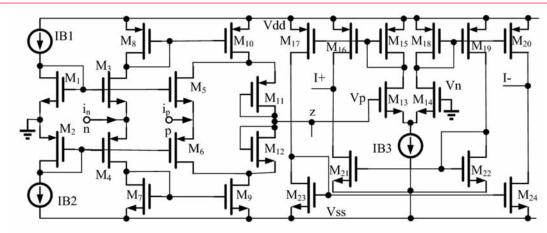

Usually this circuit can be built with techniques such as CMOS-based CDTA, which is good for monolithic IC fabrication; see Figure 2. Also, the transconductance stage can be copied in a circuit, so the number of CDTA x ports can be tailored as needed.

#### Leapfrog Ladder Filter Design Method

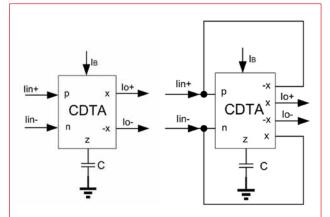

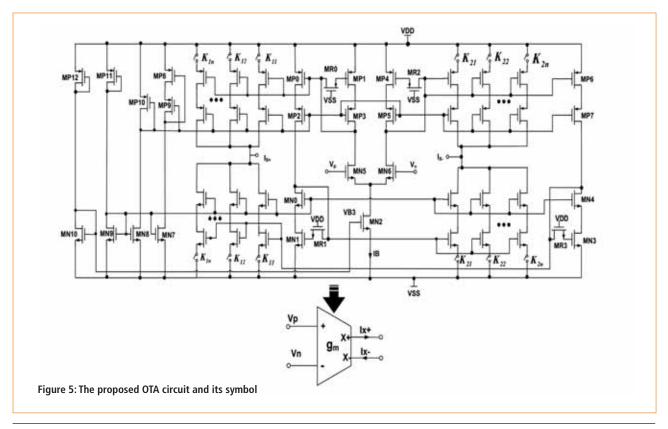

An integrator is the basic unit of a filter circuit. A firstorder integrator can be divided into two categories: lossless and lossy; see Figure 3.

Their transfer functions can be written as:

$$\frac{I_{o+} - I_{o-}}{I_{w-} - I_{o}} = \frac{2g_w}{sC}$$

(2)

$$\frac{I_{o+} - I_{o-}}{I_{in+} - I_{in-}} = \frac{2g_m/C}{s + 2g_m/C}$$

(3)

Figure 4 shows a current-mode nth-order all-pole passive LC low-pass filter network, with node equations:

Figure 3: CDTA-based lossless integrator circuit; CDTA-based lossy integrator circuit

Figure 4: Current-mode nth-order passive LC ladder network

$$V_{1} = (I_{i} - I_{2}) \frac{R_{i}}{R_{i} + \frac{1}{2} sC_{1}'}, \quad I_{2} = (V_{1} - V_{3}) \frac{1}{sL_{2}}$$

$$(4)$$

$$V_3 = (I_2 - I_4) \frac{1}{sC_3}$$

,  $I_4 = (V_3 - V_5) \frac{1}{sL_4}$  (5)

$$V_{n-3} = (I_{n-4} - I_{n-2}) \frac{1}{sC_{n-3}}, \ I_{n-2} = (V_{n-3} - V_{n-1}) \frac{1}{sL_{n-2}}$$

(6)

$$V_{n-1} = (I_{n-2} - I_n) \frac{1}{sC_{n-1}}, \quad I_n = V_{n-1} \frac{1}{sL_n + R_L}$$

(7)

To implement these equations, the voltage variables are divided by resistance  $R_o$  (the conversion factor), leading to:

$$I_{1} = (I_{i} - I_{2}) \frac{\frac{1}{R_{o}C_{1}'}}{s + \frac{1}{R_{o}C_{1}'}}, I_{2} = (I_{1} - I_{3}) \frac{R_{o}}{sL_{2}}$$

(8)

Figure 5: Signal flow diagram of a current-mode nth-order passive LC ladder network

$$I_3 = (I_2 - I_4) \frac{1}{sC_1 R_o}, I_4 = (I_3 - I_5) \frac{R_o}{sL_4}$$

(9)

$$I_{n-3} = (I_{n-4} - I_{n-2}) \frac{1}{sC_{n-3}R_o} , I_{n-2} = (I_{n-3} - I_{n-1}) \frac{R_o}{sL_{n-2}}$$

(10)

$$I_{n-1} = (I_{n-2} - I_n) \frac{1}{sC_{n-1}R_o} , I_n = I_{n-1} \frac{R_o/L_n}{s + R_L/L_n}$$

(11)

We then have:

$$H_1 = \frac{\frac{1}{R_o C_1'}}{s + \frac{1}{R_i C_1'}}, \ H_2 = \frac{R_o}{sL_2}$$

(12)

$$H_3 = \frac{1}{sC_3'R_o}, \ H_4 = \frac{R_o}{sL_4}$$

(13)

$$H_{n-3} = \frac{1}{sC_{n-3}R_o}$$

,  $H_{n-2} = \frac{R_o}{sL_{n-2}}$  (14)

$$H_{n-1} = \frac{1}{s\dot{C}_{n-1}R_o} , H_n = \frac{R_o/L_n}{s + R_L/L_n}$$

(15)

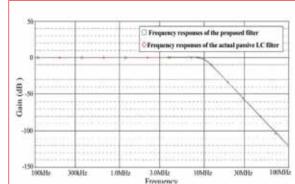

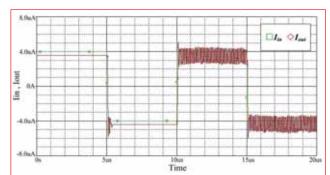

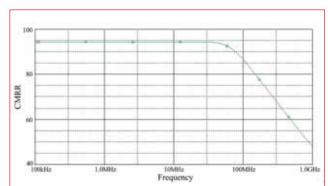

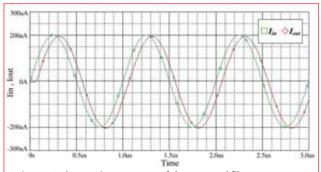

which help determine the circuit's signal flow diagram; see Figure 5. The proposed CDTA-based current-mode n<sup>th</sup>-order leapfrog ladder filter is shown in Figure 6. The circuit's simple structure adopts n active components, n grounded capacitors and uses no resistors, which safeguards the bandwidth and is convenient for IC fabrication.

#### Circuit Parameters

Assuming

$$R_i = R_I = R_o$$

(16)

and using Equations 2-15 helps determine the parameter relationships of the components in the circuits of Figures 4 to 6.

$$\frac{2g_{m1}/C_1}{s + 2g_{m1}/C_1} = \frac{1/R_0C_1}{s + 1/R_0C_1}$$

(17)

then

$$C_1 = 2g_{in1}R_oC_1$$

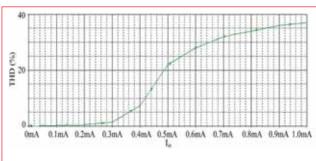

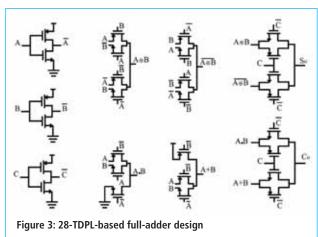

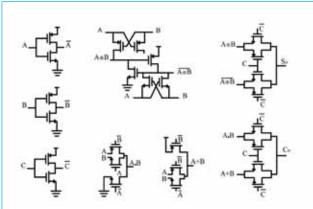

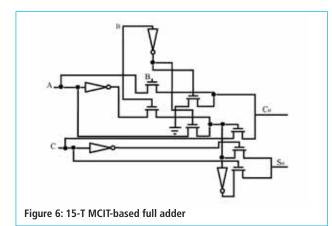

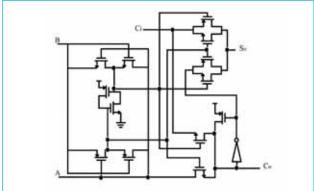

(18)